# A distributed ramp signal generator of column-parallel single-slope ADCs for CMOS image sensors

# Kaita Imai<sup>1a)</sup>, Keita Yasutomi<sup>2</sup>, Keiichiro Kagawa<sup>2</sup>, and Shoji Kawahito<sup>2</sup>

<sup>1</sup> Graduate School of Science and Technology, Shizuoka University,

3-5-1 Johoku, Nakaku, Hamamatsu, Shizuoka 432-8011, Japan

<sup>2</sup> Research Institute of Electronics, Shizuoka University,

3-5-1 Johoku, Nakaku, Hamamatsu, Shizuoka 432-8011, Japan

a) *imai@idl.rie.shizuoka.ac.jp*

This paper proposes a distributed ramp signal gener-Abstract: ator of column-parallel single-slope ADCs for CMOS image sensors. This architecture does not require any power-hungry amplifiers of the conventional one but consists of miniaturized column-wise ramp signal generators connected together by metal wires, which achieves high linearity and high uniformity. Simulation results show less than 1LSB nonlinear error of the ramp signal at 12-bit ADC resolution is attained only by having the consumption current of 6.4 mA and the area of  $2.4 \,\mathrm{mm^2}$  which are much smaller than the conventional one. It is also confirmed that  $100 \,\mathrm{m}\Omega$  resistive connection attains less than 1LSB gain error mismatching, even though the mismatch of the column-wise ramp signal generators is as large as 20%.

Keywords: CMOS image sensors, ramp signal generator, columnparallel single-slope ADC, ultra-high-definition television, mismatch reduction

**Classification:** Integrated circuits

#### References

- [1] S. Huang, et al., "A 2.5 inch, 33 Mpixel, 60 fps CMOS Image Sensor for UHDTV Application," IEEE Int. Image Sensor Workshop, pp. 304–307, 2009.

- [2] T. Watabe, et al., "A 33 Mpixel 120 fps CMOS Image Sensor Using 12b Column-Parallel Pipelined Cyclic ADCs," ISSCC Dig. Tech. Papers, pp. 388-390, Feb. 2012.

- [3] T. Toyama, et al., "A 17.7 Mpixel 120 fps CMOS Image Sensor with 34.8 Gb/s Readout," ISSCC Dig. Tech. Papers, pp. 420-422, Feb. 2011.

- [4] S. Yoshihara, et al., "A 1/1.8-inch 6.4 MPixel 60 frames/s CMOS Image Sensor With Seamless Mode Change," IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2998-3006, Dec. 2006.

#### 1 Introduction

The next-generation vision systems require image sensors with aggressive performance. For instance, in ultra-high-definition television (UHDTV) broadcasting, a 33 Mpixel (8k4k) CMOS image sensor with 12-bit ADC resolution at 120 fps has been developed. A column-parallel ADCs is the key element for the CMOS image sensor to realize the high pixel rate [1, 2, 3]. However the power consumption, which determines dark current noise, is still greater than 2W and the pixel pitch of  $2.8\,\mu\text{m}$  is quite large compared with the state-of-the-art pixel size. In order to achieve high speed operation at very low power consumption and finer pitch column implementation, a single-slope ADC (SS-ADC) is an attractive architecture [3, 4]. However, if the horizontal number of pixels becomes as large as 8000, there is a difficulty to supply a ramp signal into all the columns uniformly, even though a power-hungry driver for the ramp signal generator (RSG) is used. In particular, a nonconstant gate capacitance of the comparator in SS-ADCs seriously distorts the ramp signal where several thousands of comparators turn over simultaneously. Furthermore, a conventional RSG of the CMOS image sensor for UHDTV applications occupies large area of  $5 \text{ mm}^2$  as reported approximately in [3].

This paper proposes a new architecture for ramp signal generation to reduce the power consumption and the waveform distortion of the ramp signal. In this architecture, small-size RSG units are distributed over all the columns and connected with neighboring units together by a same metal wire. The proposed RSG does not require the power-hungry driver amplifier which is essential in the conventional one but has high immunity of the waveform distortion and results in high linearity, just having the consumption current of 6.4 mA and the area of 2.4 mm<sup>2</sup>. Moreover the resistive interconnection by the metal wire helps to reduce the influence of inherent mismatching between the columns due to the variation in transistor characteristics caused by semiconductor manufacturing process.

#### 2 Circuit architectures

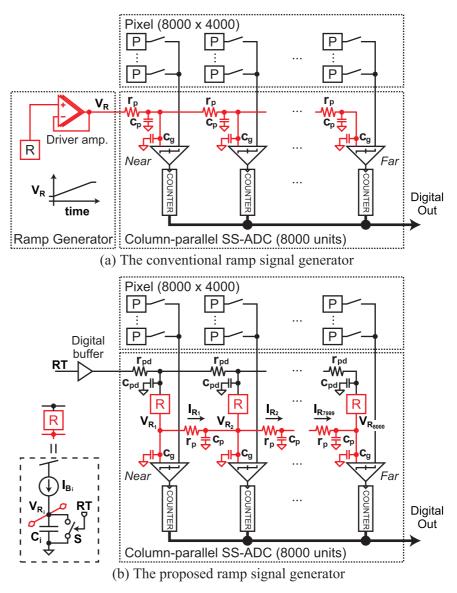

Fig. 1 describes the architectures of the conventional (Fig. 1 (a)) and proposed (Fig. 1 (b)) RSGs for CMOS image sensors which have 8000 column-parallel SS-ADCs consisting of a comparator and a counter. The time interval from the beginning of the ramp signal to the time when the ramp signal exceeds the pixel output is measured by the counter.

In the conventional architecture (Fig. 1 (a)), one input of the comparator is connected with a ramp signal line. This ramp signal is supplied by a common RSG outside the columns. In this architecture, a power-hungry driver amplifier is necessary to satisfy high linearity and high speed operation because a parasitic resistance  $r_p$  and a parasitic capacitance  $c_p$  of the ramp signal line distorts the linearity of the ramp signals, depending on bias current of the driver amplifier.

Moreover the ramp signal suffers from the voltage-dependent impedance

Fig. 1. The architectures for CMOS image sensors

loads because a gate capacitance  $c_g$  of the comparator in SS-ADCs has a large variation due to the input transistor's operating point and the ramp signal is distorted particularly when several thousands of comparators turn over simultaneously.

In the architecture of the proposed RSG used at the column as shown in Fig. 1 (b), each SS-ADC consists of an RSG, a comparator and a counter. The *i*-th (i = 1, ..., 8000) RSG unit consists of a capacitor  $C_i$ , a constant current source  $I_{B_i}$  and a switch S controlled by the common reset signal RT whose line has a parasitic resistance  $r_{pd}$  and a parasitic capacitance  $c_{dp}$ . When the switch is turned off, the ramp signal  $V_{R_i}$  is supplied to the comparator and the *i*-th column pixel output is compared with  $V_{R_i}$ . And  $V_{R_i}$  is connected with neighboring units ( $V_{R_{i-1}}, V_{R_{i+1}}$ ) together by a same metal wire.

One of the features of the proposed RSG is that only digital signal RT is supplied from outside of columns. It is quite easier to maintain the uniformity of the signal by a digital buffer without consuming DC current and the wiring

delay of RT is not so severe as the analog ramp signal itself. Moreover using much larger  $C_i$  than  $c_g$  can reduce nonlinearity due to the gate voltage dependence of  $c_g$ .

Another feature is the resistive interconnection of  $V_{R_i}$  by the metal wire. The deviation of the ramp signal gain between the columns due to the use of small-size components is reduced by the low-impedance interconnection of neighboring RSG outputs. Since adjacent two nodes are connected by the metal wire, a current  $I_{R_i}$  flows along with  $r_p$ , if  $V_{R_i}$  deviates from  $V_{R_{i+1}}$ . This current has an effect of averaging the voltage difference between the columns depending on  $r_p$ . As a result, the eventual ramp signal mismatch is drastically reduced.

# **3** Improvement of linearity

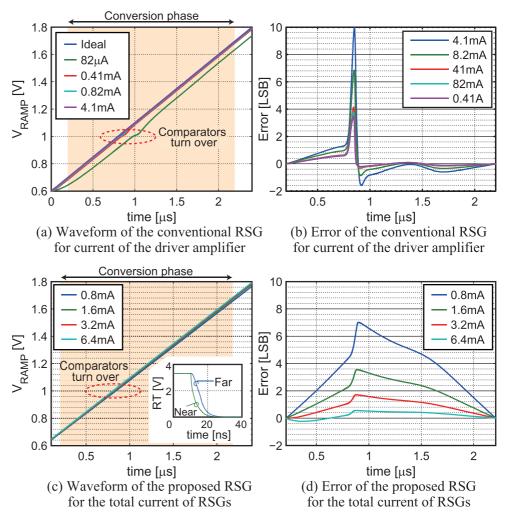

Fig. 2 shows characteristics of transient SPICE simulations at the farthest column (the left side) from signal sources (the right side). As the severest condition for the ramp signal, all the pixel outputs are fixed at 1 V, assuming that a row of the pixels is illuminated at the same level and the outputs of the comparators turn over simultaneously when the ramp signal level becomes

© IEICE 2012 DOI: 10.1587/elex.9.1893

at 1 V. The conversion phase is from  $0.2 \,\mu\text{m}$  to  $2.2 \,\mu\text{m}$ , not including very nonlinear starting period. Here we estimates  $r_p$  of  $10 \,\mathrm{m}\Omega$ ,  $c_p$  of  $2.3 \,\mathrm{fF}$ ,  $r_{pd}$  of  $100 \,\mathrm{m}\Omega$  and  $c_{pd}$  of  $0.23 \,\mathrm{fF}$ , using  $0.11 \,\mu\text{m}$  CMOS image sensor process.

Fig. 2 (a) shows the results for the conventional RSG. In the parametric simulation, the driver bias current is changed while maintaining the current density of transistors for the driver amplifier in which we employ a single-stage topology. This is a design example but we can immediately notice that the nonlinearity of the ramp signal is closely related to the bias current of the driver amplifier. From Fig. 2 (b), the case of 0.41 A is still larger than 3LSB of the error at 12-bit resolution, which is calculated by comparing the simulated values and the linearly-fitted values during the conversion phase.

Fig. 2 (c) shows the results for the proposed RSG. Here we change the total current of  $I_{B_i}$  as the parameter, while  $C_i$  is also changed to keep the ratio of  $I_{B_i}/C_i$  to  $0.5 \text{ V}/\mu\text{s}$ . In all the cases, the mean value and the transient peak value of the digital buffer current are 94 nA and 1.2 mA, respectively. Fig. 2 (d) shows that the total current of 6.4 mA, which corresponds to  $I_{B_i}$  of 800 nA and  $C_i$  of 1.6 pF, can achieve less than 1LSB error. Furthermore this can be implemented within the area of 2.4 mm<sup>2</sup>, assuming the use of a MIM capacitor of 8 fF/ $\mu$ m<sup>2</sup>. In addition, it should be noted that thermal (kT/C) noise of the RSG is only 51  $\mu$ V<sub>rms</sub> and much smaller than 1LSB of 244  $\mu$ V.

#### 4 Mismatch analysis

For any distributed architectures, the influence of inherent mismatching between the columns due to the variation in transistor characteristics caused by semiconductor manufacturing process is very crucial. However, in the proposed RSG, the mismatch can be reduced by the resistive interconnection of the metal wire. In order to estimate the effect, numerical simulations are conducted by MATLAB. Here we choose  $C_i$  of 100 fF and  $I_{B_i}$  of 50 nA as very small-size components to investigate the condition that the circuit components greatly deviate from column to column.

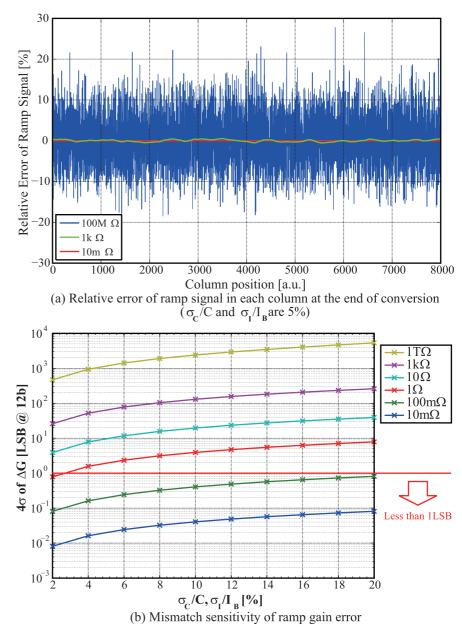

Fig. 3 (a) shows relative errors of the ramp signals at the end of conversion, where the standard deviations,  $\sigma_C/C$  and  $\sigma_I/I_B$  are 5%, respectively. For the resistance of 100 MΩ which corresponds to supposing no wire resistive connection, the ramp signals greatly deviate from column to column because of the mismatch on both capacitors and constant current sources. Even 1 kΩ resistive connection well reduces the relative error to be less than ±1%. Using 10 mΩ resistive wire connection, the error can be negligibly small (less than ±0.001%).

Fig. 3 (b) shows how the parasitic resistance and circuit component mismatches are related to the ADC accuracy. The gain error ( $\Delta G$ ) of the ramp signals is expressed as a unit of LSB at 12-bit resolution by using

$$\Delta G = \frac{\Delta g \cdot T_c}{V_{FS}} \times 2^{12}$$

where  $\Delta g$  is the gain error as a unit of volt per second. Assuming that mismatches in the RSGs are normally distributed over the columns, the standard

Fig. 3. Mismatch simulation results for 8000 columns

deviation of  $\Delta G$  in each ADC is an index to evaluate the column-parallel ADC. Therefore  $4\sigma$  of  $\Delta G$  is calculated because the probability of taking outside of  $4\sigma$  is 0.0063% which corresponds to less than 1 column out of 8000 columns (8000 × 0.0063% = 0.51).

As a result, even if 20% of the circuit component mismatches occurs, the available resistive connections of  $100 \,\mathrm{m}\Omega$  and  $10 \,\mathrm{m}\Omega$  well reduces the error to be less than 1LSB. This low sensitivity to circuit component mismatches allows us to use a small-size capacitance and current source.

# **5** Conclusion

A distributed ramp signal generator of column-parallel SS-ADCs for ultrahigh-definition television CMOS image sensors has been described. This can solve the problem on how to supply the analog ramp signal evenly over all

the columns by the column implementation of unit ramp signal generators and those interconnections by a same metal wire.

In the proposed architecture, only the digital signal is supplied from the outside of columns instead of the ramp signal itself. As a result, without the power-hungry driver amplifier in the conventional one, high linearity and high uniformity of the ramp signal are maintained, even though several thousands of comparators turn over simultaneously. From the simulation results, the nonlinear error is efficiently reduced to less than 1LSB at 12-bit resolution.

Although the column mismatch due to the variability on semiconductor manufacturing process may occur, the wire interconnection of ramp signal nodes between the columns provides high uniformity, reducing the eventual ramp signal mismatch. Numerical simulation results show that  $100 \text{ m}\Omega$  resistive connection which is attained in  $0.11 \,\mu\text{m}$  CMOS image sensor process reduces the number of column having more than 1LSB of the gain error to less than one column.

In conclusion, the proposed architecture achieves the consumption current of 6.4 mA and the area of  $2.4 \text{ mm}^2$  for the conversion time of  $2 \mu \text{s}$  and 8000 columns, while the conventional one has the consumption current of larger than 0.4 A and the area of  $5 \text{ mm}^2$ . Therefore in order to realize ultra-highdefinition CMOS image sensors with very high pixel rate and lower power consumption, this distributed ramp signal generator for column-parallel singleslope ADCs becomes essential.

# Acknowledgments

This work is supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Cadence Design Systems, Inc.