# A new curvature-corrected CMOS bandgap voltage reference

## Ruhaifi Abdullah Zawawia) and Othman Sidek

Collaborative Microelectronic Design Excellence Centre (CEDEC),

Universiti Sains Malaysia (USM),

Engineering Campus, 14300, Nibong Tebal

Seberang Prai Selatan, Pulau Pinang, Malaysia

a) ruhaifi@usm.my

**Abstract:** The current paper presents an improved bandgap voltage reference (BGR) that utilizes curvature-corrected current generators which compensate for the voltage reference at lower and higher temperature range. The voltage reference is operated with a supply voltage of  $2.5\,\mathrm{V}$  to achieve an output reference of  $1.1835\,\mathrm{V}$ . The temperature coefficient achieved from the circuit is  $1.342\,\mathrm{ppm/^\circ C}$ , resulting from temperature changes between  $-50\,\mathrm{^\circ C}$  to  $125\,\mathrm{^\circ C}$ , sixfold improvement from first-order BGR. The proposed circuit is simulated using Silterra  $0.13\,\mu\mathrm{m}$  CMOS technology.

**Keywords:** CMOS bandgap reference, low variation

**Classification:** Integrated circuits

### References

- [1] B. Razavi, Book Temperature Independent References, McGraw-Hill, City, 2001

- [2] G. A. Rincon-Mora and P. E. Allen, "A 1.1-V current-mode and piecewise-linear curvature-corrected bandgap voltage reference," *IEEE J. Solid-State Circuits*, vol. 33, no. 10, pp. 1551–1554, Oct. 1998.

- [3] K. N. Leung and P. K. T. Mok, "A 2-V 23 J1 A 5.3 ppm/°C curvature-compensated CMOS bandgap voltage reference," *IEEE J. Solid-State Circuits* vol. 38, no. 3, pp. 561–564, March 2003.

- [4] J. H. Li, X. B. Zhang, M. Y. Yu, and L. Han, "A 10 ppm 1.8-V Piecewise Curvature-Corrected Bandgap Reference in 0.5  $\mu$ m CMOS," Asia Pacific Conference on Postgraduate Research in Microelectronics Electronics, 2009, pp. 416–419, Jan. 2009.

# 1 Introduction

The performance of most circuit blocks is connected to that of the voltage references used to bias and power them. A first-order bandgap reference adds the forward-bias voltage across the p-n diode, and that voltage is weighted by adjusting the ratio of two resistors [1]. The voltage across the p-n diode is

expressed as the sum of a constant term, a term proportional to temperature and a nonlinear term clearly explained in [2]. The variation of the nonlinear term with respect to temperature reported in [2] is  $4.5\,\mathrm{mV}$  for the temperature between  $-50^{\circ}\mathrm{C}$  to  $150^{\circ}\mathrm{C}$ . A few works reported on curvature-corrected BGR are presented in [3, 4]. Although these circuits have been proven to lower the voltage variation, the variation only ranges from  $0^{\circ}\mathrm{C}$  to  $125^{\circ}\mathrm{C}$ . In the current work, the variation of the nonlinear term is decreased through the inclusion of curvature-corrected current generators that compensate for the voltage reference at lower and higher temperature.

## 2 Proposed design

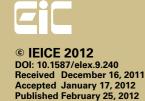

The operation of the proposed design is shown in Fig. 1. The first-order BGR produces an output given as

$$V_{REF} = K_1 V_T ln(n) + V_{EB}, \tag{1}$$

where  $K_1$  is the temperature independent coefficient,  $V_T$  is the thermal voltage, and n is the emiter area ratio of BJT.

Fig. 1. Curvature-corrected BGR.

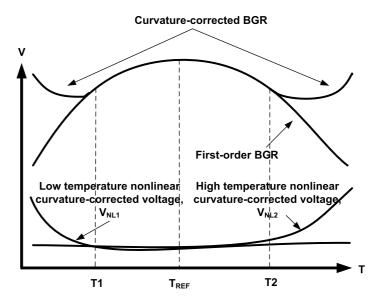

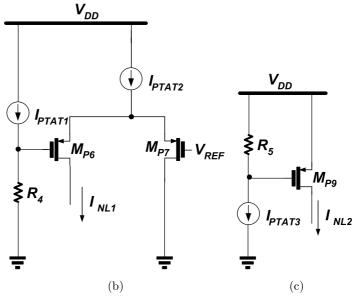

To compensate the nonlinearity of the first-order BGR, the nonlinear curvature-corrected voltages,  $V_{NL1}$  and  $V_{NL2}$ , are added. As a result, a curvature-corrected BGR is obtained, as graphically shown in Fig. 1. The proposed BGR consists of first-order BGR, current generators,  $G_A$  and  $G_B$ , and a startup circuit, as illustrated in Fig. 2 (a).

The output of the first-order BGR is expressed as follows:

$$V_{ref} = \frac{R_2 + R_3}{R_1} V_T ln(n) + V_{EB3},$$

(2)

where n is the emitter area ratio of  $Q_2$ . The proposed current generator  $G_A$  is illustrated in Fig. 2(b). The current  $I_{PTAT1}$  flowing through the resistor

© IEICE 2012

DOI: 10.1587/elex.9.240

Received December 16, 2011

Accepted January 17, 2012

Published February 25, 2012

**Fig. 2.** (a) Proposed BGR, (b) Current generator,  $G_A$ , and (c) Current generator,  $G_B$ .

$R_4$  produces a PTAT voltage given as

$$V_{GMP6} = R_4 I_{PTAT1}, (3)$$

where

$$I_{PTAT1} = \alpha \frac{V_T ln(n)}{R_1}.$$

(4)

Parameter  $\alpha$  is the ratio of the size of  $M_{P4}$  to  $M_{P2}$ . The size of  $M_{P7}$  is larger than  $M_{P6}$  to reduce the variation of the source voltage  $M_{P6}$  and  $M_{P7}$ . At temperature below  $T_{REF}$ , when the voltage  $V_{SGMP6}$  is much larger than its threshold voltage,  $M_{P6}$  is operating in the saturation region. By further increasing the temperature,  $M_{P6}$  will no longer be in the saturation region; it starts operating in the weak inversion region.

When  $V_{SGMP6}$  is much lower than its threshold voltage, the transistor  $M_{P6}$  will be completely cut off and there will be no current flowing through  $M_{P6}$ . The operation of the proposed circuit by [4] is illustrated in Fig. 2 (c). It works similar to the circuit of Fig. 2 (b), but it produces current  $I_{NL2}$  at high temperature only. The voltage at gate terminal of  $M_{P9}$  is given by

$$V_{GMP9} = VDD - R_5 I_{PTAT3}, (5)$$

where

$$I_{PTAT3} = \frac{\gamma V_T ln(n)}{R_1}. (6)$$

Parameter  $\gamma$  is the ratio of the size of  $M_{P8}$  to  $M_{P2}$ . The gate-source voltage of transistor  $M_{P9}$  is insensitive to power supply variation expressed as follows

$$V_{SGMP9} = \frac{R_5 V_T ln(n)}{R_1}. (7)$$

Currents  $I_{NL1}$  and  $I_{NL2}$  run through  $R_3$ . As a result, the corrected voltages  $V_{NL1}$  and  $V_{NL2}$  are generated. The addition of the corrected voltages with the output voltage produced by the first-order BGR expresses the following equation:

$$V_{REF} = \frac{R_2 + R_3}{R_1} V_T ln(n) + V_{EB3} + (I_{NL1} + I_{NL2}) R_3.$$

(8)

The corrected voltages are given by the third term of Eq. (8). It efficiently compensates the voltage variation, thereby keeping the output voltage of  $V_{REF}$  from changing with the change in temperature.

## 3 Simulation results

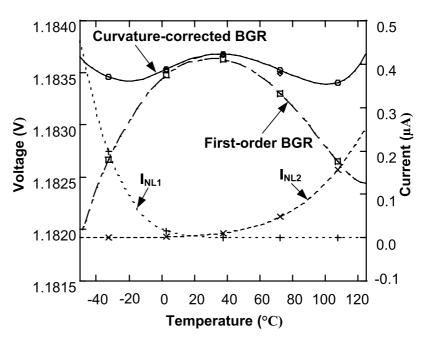

The proposed BGR shown in Fig. 2 (a) is carried out in a standard  $0.13\,\mu\mathrm{m}$  CMOS process. Figure 3 shows the variation of voltage reference within the temperature range  $-50^{\circ}\mathrm{C}$  to  $125^{\circ}\mathrm{C}$ . The voltage variation is only  $0.278\,\mathrm{mV}$  for the proposed BGR, sixfold improvement from  $1.714\,\mathrm{mV}$  for the first-order BGR. The curvature-corrected currents  $I_{NL1}$  and  $I_{NL2}$  are also shown in Fig. 3. When the temperature is less than  $20^{\circ}\mathrm{C}$ , the nonlinear-corrected current  $I_{NL1}$  is increasing while  $I_{NL2}$  is completely cut off. By contrast, the current  $I_{NL2}$  starts increasing, whereas the current generator  $G_A$  is in off state when the temperature is greater than  $20^{\circ}\mathrm{C}$ . The maximum currents of  $I_{NL1}$  and  $I_{NL2}$  are 450 and  $250\,\mathrm{nA}$ , respectively.

#### 4 Conclusion

A BGR with very low voltage variation has been presented. The proposed design produces an output voltage reference of  $1.1835\,\mathrm{V}$  over a temperature range of  $-50^{\circ}\mathrm{C}$  to  $125^{\circ}\mathrm{C}$ . The temperature coefficient achieved from the circuit is  $1.342\,\mathrm{ppm/^{\circ}C}$ , whereas the temperature coefficient of  $8.276\,\mathrm{ppm/^{\circ}C}$  is obtained for the first-order BGR.

Fig. 3. Voltage reference and nonlinear current.

# **Acknowledgments**

The authors would like to express their sincerest appreciation to all the ICDC group members, Silterra Malaysia Sdn. Bhd., and the Collaborative Microelectronic Design Excellence Centre (CEDEC).