# Low-voltage differential voltage follower for WTA and fully differential applications

Ivan Padilla-Cantoya<sup>1a)</sup>, Paul M. Furth<sup>2</sup>, Jesus E. Molinar-Solis<sup>3</sup>, and Alejandro Diaz-Sanchez<sup>4</sup>

<sup>1</sup> Departamento de Electronica, Sistemas e Informatica DESI, Instituto Tecnologico y de Estudios Superiores de Occidente ITESO, Periférico Sur Manuel Gómez Morín No. 8585 Tlaquepaque, Jalisco, Mexico

<sup>2</sup> Klipsch School of Electrical and Computer Engineering, New Mexico State University, Las Cruces, NM 88001 USA

<sup>3</sup> Facultad de Ingenieria, Universidad Autonoma del Estado de Mexico UAEM, Jose Revueltas 17, Tierra Blanca, Ecatepec, Estado de Mexico, Mexico

<sup>4</sup> National Institute for Astrophysics, Optics and Electronics, INAOE,

Luis E. Erro 1, Tonantzintla, Puebla, Mexico

a) ivapadil@iteso.mx

**Abstract:** A low-voltage differential version of a high performance voltage follower is presented. The proposed circuit is very compact, and symmetric with respect to the input devices. Both differential input devices are enhanced by local shunt feedback, increasing the gain and, thus, reducing the output resistance for higher precision. The circuit has proved useful as a winner-take-all (WTA) circuit. It also features operation as a fully differential amplifier with low supply voltage requirements close to a transistor's threshold voltage. Experimental results verifying the operation of the proposed structure are provided. **Keywords:** analog CMOS integrated circuits, winner-take-all (WTA)

**Classification:** Integrated circuits

### References

analog circuits

- [1] J. Lazzaro, S. Lyckenbush, M. A. Malhowad, and C. Mead, "Winner takeall of O(n) complexity," *Advances in Neural Signal Processing Systems*, ed. D. S. Touretzky, pp. 703–711, Morgan Kaufmann, 1989.

- [2] R. G. Carvajal, J. Ramírez-Angulo, A. López-Martin, A. Torralba, J. Galán, A. Carlosena, and F. Muñoz, "The flipped voltage follower: A useful cell for low-voltage low-power circuit design," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 7, pp. 1276–1291, July 2005.

- [3] B. Razavi, Design of Analog CMOS Integrated Circuits, p. 324, McGraw-Hill, 2001.

© IEICE 2012 DOI: 10.1587/elex.9.491 Received January 17, 2012 Accepted February 21, 2012 Published March 25, 2012

# 1 Introduction

Winner-take-all (WTA) circuits have become fundamental in many systems that require minimum (MIN) and maximum (MAX) operations. Some applications of these types of operation include non linear analog systems such as data acquisition, function synthesis and precision rectifiers. In this type of circuits a given set of inputs are available, in which the input with the highest or lowest level, depending on the operation being performed, defines the output signal.

### 2 Conventional WTA

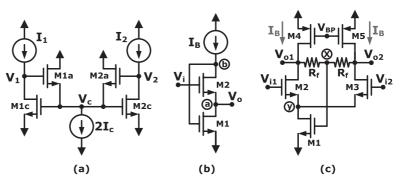

Fig. 1 a shows a basic current-mode WTA consisting of two inputs [1]. Consider the initial condition where  $I_1 = I_2$ , if transistors M1a and M2a are identical their gate-source voltages are also the same, thus  $V_1 = V_2$ . Under these conditions the current in both transistors is  $I_c$ , and M1c and M2c have the current  $I_1 = I_2$ . Therefore, the output exhibits a voltage  $V_c = V_{GSM1c,2c}$ . Now consider the case where  $I_1$  increases, this causes the gate-source voltage of M1c to increase. Due to the fact that the gate terminals of M1c and M2c are connected,  $V_{GSM2c}$  also increases; although the current  $I_2$  is not increasing; hence the drain-source voltage of M2c tends to decreases to compensate this effect, forcing the operation into triode. Consequently, the output voltage adopts the gate-source voltage of the input transistor with the larger input current, corresponding to the expression:

$$V_c = \sqrt{\frac{I_i^{\text{max}}}{K(W/L)}} - V_T \tag{1}$$

Where  $K = (\mu C_{ox})/2$ , W/L represents the dimensions of the transistor and  $V_T$  is the threshold voltage. Note that the minimum supply requirement is that of two gate-source voltages and a drain-source saturation voltage.

**Fig. 1.** a) Conventional WTA [1], b) Flipped voltage follower (FVF) [2], and c) proposed symmetrical differential FVF (SDFVF).

# 3 Symmetric differential voltage follower as WTA

As mentioned previously, the WTA follows the input signal with the dominant voltage level, thus the proposed circuit is based on a high performance

© IEICE 2012 DOI: 10.1587/elex.9.491 Received January 17, 2012 Accepted February 21, 2012 Published March 25, 2012

voltage follower denominated Flipped Voltage Follower (FVF) [2], and shown in Fig. 1 b. Note that transistor M2 has a constant biasing current  $I_B$ , which produces a constant voltage  $V_{GS2}$ , reflecting variations in  $V_i$  at node a level shifted by  $V_{GS2}$ . Additionally, M1 can sink large currents, offering a very low impedance at this node of approximately  $1/(g_{m1}g_{m2}r_{o2})$ .

The proposed circuit is shown in Fig. 1 c. It consists of two FVF's, where M1 offers shunt feedback for both M2 and M3. The resistors R<sub>f</sub> avoid the necessity of connecting the gate of M1 directly to the drain of the differential transistors as in the FVF. This permits the architecture to have different voltage levels at the drain of M2 and M3, which also results in moderate gain as explained later. M1 behaves as a current sensing transistor for both M2 and M3, offering a symmetric current-sinking capability to both of the input transistors. Thus, it is denominated the "Symmetric Differential FVF" or SDFVF. The SDFVF presents an enhanced output resistance of  $1/(2g_{m1}g_{m2,3}r_{o2,3})$ . When large differential signals are present, node y reflects the voltage variations of the minimum of the input voltages, with a constant dc level shift of  $V_{GS}$  of the corresponding input transistor. Under this condition, the other input transistor obtains a gate-source voltage larger than the required to operate with a current I<sub>B</sub>, forcing it to go into triode region with a small V<sub>DS</sub>. At this point, this transistor presents a resistance of R<sub>triode</sub>, whereas the other transistor combined with M1 present a much lower resistance as described for the FVF, thus, controlling the voltage at

In addition, this structure also offers moderate gain at the output voltages  $V_{o1}$  and  $V_{o2}$  when small signals are present at the inputs, and both M2 and M3 operate in saturation, the output voltages  $V_{o1}$  and  $V_{o2}$  present moderate gain, operating as a fully differential amplifier. In such case, common-mode output voltages are mounted on a DC level of value  $V_{GSM1}-V_{ss}$ . Under these conditions no current flows across the resistors  $R_f$ , thus M1 operates as a diode connected transistor adjusting  $V_{GSM1}$  to sink the current provided by M4 and M5. The small-signal gain is defined by  $g_{m1,2}(r_{o4,5}||r_{o2,3}||R_f)$ , and node x behaves as a signal ground, maintaining the voltage  $V_{GSM1}$  required to have  $2I_B$ . For small signal applications this circuit operates similar to the conventional fully differential (FD) amplifier reported in [3] with reduced supply voltage. The conventional FD in [3] requires a gate-source voltage and two drain-source voltages, whereas the proposed requires a gate-source voltage and one drain-source saturation voltage.

#### 4 Experimental results

To validate the proposed structure, the conventional and proposed structures were assembled on a breadboard using commercial transistor arrays ALD06 and ALD07 (NMOS and PMOS). Their parameters are: for  $\beta=\mu C_{\rm ox}(W/L);~\beta_{\rm NMOS}=480\,\mu A/V^2,~\beta_{\rm PMOS}=220\,\mu A/V^2,~\lambda_{\rm NMOS,PMOS}=0.05\,V^{-1},~|V_{\rm T(NMOS,PMOS)}|=0.7\,V,~\gamma=0.3\,\surd{\rm V}.$  The circuits were tested with a biasing current  $I_{\rm B}=50\,\mu A,$  resistances  $R_{\rm f}=100\,\rm k\Omega$  and a load capac-

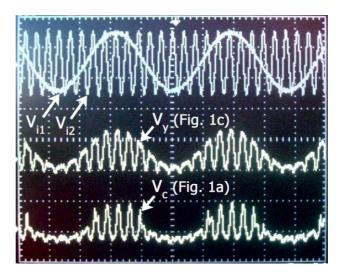

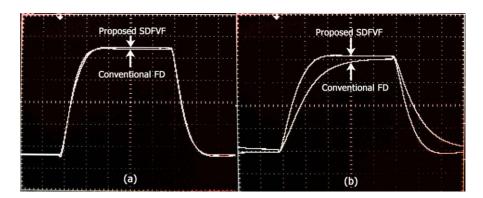

itance of 140 pF on each of the differential outputs. Fig. 2 shows the WTA operation of the circuits in Fig. 1 a and 1 c, where the conventional WTA has a supply voltage of  $V_{\rm dd}-V_{\rm ss}=3.5\,\rm V$  and the proposed SDFVF has  $V_{\rm dd}-V_{\rm ss}=2.5\,\rm V$ . Two different input signals were used for the SDFVF, a sine waveform  $V_{i1}=1\,V_{pp}$  at 10 kHz and  $V_{i2}=1\,V_{pp}$  at 100 kHz. These signals were also used to generate linear currents  $I_1$  and  $I_2$  for the conventional WTA using independent PMOS FVF's with sensing resistors of  $5\,\rm k\Omega$ . Observe that the output voltage  $V_y$  in the SDFVF follows accurately the minimum of the input signals whereas voltage  $V_c$  in the conventional WTA presents a distortion due to the quadratic terms of the current-voltage relation of transistors M1c and M2c. Fig. 3 shows the transient response of the circuits in Fig. 1 c and the conventional FD in [3] using a supply voltage of  $V_{\rm dd}-V_{\rm ss}=3\,\rm V$ . The circuits were tested in a conventional inverting configuration with feedback and input resistors of  $100\,\rm k\Omega$ . An input signal of

**Fig. 2.** Output voltage of the conventional WTA and the proposed SDFVF operating as a WTA with sine input signals  $V_{i1}=1\,V_{pp}$  at  $10\,kHz$  and  $V_{i2}=1\,V_{pp}$  at  $100\,kHz$ .

Fig. 3. Transient response of the conventional FD and proposed SDFVF with a  $V_i=1.2\,V_{pp}$  at  $40\,kHz$  using a supply voltage of a)  $3\,V$  and b) Using  $1.4\,V$ .

$V_{\rm i}=1.2\,V_{\rm pp}$  at 40 kHz was used. Observe that the signal from the conventional FD is not able to follow the input signal, showing that transistors have been forced out of saturation, whereas the proposed structure maintains its operation.

#### 5 Conclusion

A high performance differential voltage follower for WTA application was discussed. The operation was demonstrated experimentally with high precision. Also, results from experimental measurement of the circuit as a fully-differential amplifier with low power supply were presented.

# **Acknowledgments**

This work has been supported in part by the Mexican Consejo Nacional de Ciencia y Tecnologia (CONACYT) under Grant 134886.

© IEICE 2012 DOI: 10.1587/elex.9.491 Received January 17, 2012 Accepted February 21, 2012 Published March 25, 2012