| Title        | Low-Voltage Wireless Analog CMOS Circuits toward 0.5 V Operation                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Wang, Jun; Kihara, Takao; Ham, Hyunju et al.                                                                        |

| Citation     | IEICE TRANSACTIONS on Fundamentals of Electronics, Communications and Computer Sciences. 2010, E93-A(2), p. 356-366 |

| Version Type | VoR                                                                                                                 |

| URL          | https://hdl.handle.net/11094/51697                                                                                  |

| rights       | copyright©2010 IEICE                                                                                                |

| Note         |                                                                                                                     |

# Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

INVITED PAPER Special Section on Analog Circuit Techniques and Related Topics

# **Low-Voltage Wireless Analog CMOS Circuits toward 0.5 V Operation**

Toshimasa MATSUOKA<sup>†a)</sup>, *Member*, Jun WANG<sup>†</sup>, Takao KIHARA<sup>†</sup>, Hyunju HAM<sup>†</sup>, *Nonmembers*, and Kenji TANIGUCHI<sup>†</sup>, *Member*

**SUMMARY** This paper introduces several techniques for achieving RF and analog CMOS circuits for wireless communication systems under ultra-low-voltage supply, such as 0.5 V. Forward body biasing and inverterbased circuit techniques were applied in the design of a feedforward  $\Delta$ - $\Delta$ A/D modulator operating with a 0.5 V supply. Transformer utilization is also presented as an inductor area reduction technique. In addition, application of stochastic resonance to A/D conversion is discussed as a future technology.

key words: analog, RF, CMOS, forward body biasing, transformer, stochastic resonance

### 1. Introduction

Wireless integrated transceivers based on RF-CMOS technology have advantages of scalability and performance ( $f_T$  and NF). The International Technology Roadmap for Semiconductors (ITRS) [1] predicts that the supply voltages of low-power digital circuits will decrease to 0.5 V in the near future. Considering the integration of RF and analog circuits with digital circuits, the development of receiver circuits operating at such a low supply voltage will be required.

However, with such a low voltage supply, degradation in performance due to non-idealities of the analog building blocks becomes a serious problem, especially for IF amplifier and A/D converters. For example, integrators of  $\Delta$ - $\Sigma$  A/D modulators with a supply voltage close to  $V_{TH}$  may force the transistors to operate in weak inversion, thereby inducing poor accuracy and low operation speed. At the same time, a low supply voltage also limits the integrator output swing, thereby degrading the performance of the A/D modulator.

Apart from low-voltage operation, the continuous scaling of CMOS technologies has imposed another challenge on CMOS radio-frequency integrated circuits (RFICs); a small chip area [2], [3]. Under the integration of RF circuits with digital circuits in advanced CMOS technologies, the development of low-voltage and small-area (low-cost) RF circuits is required. Although digital RF circuit design methodologies can help contribute to a solution [2], [3], analog-centric circuits still remain.

Even using a matured CMOS process, low-voltage operation RF and analog circuits are important and attract

Manuscript received November 11, 2009.

a) E-mail: matsuoka@eei.eng.osaka-u.ac.jp DOI: 10.1587/transfun.E93.A.356 some interest, especially in wireless sensor applications with requirements of long battery life time.

This paper introduces some techniques to achieve low-voltage operation such as 0.5 V. Sections 2 and 3 describe forward body biasing and inverter-based circuit techniques. These techniques were applied in design of a feedforward  $\Delta$ - $\Sigma$  A/D modulator operating at 0.5 V supply, as described in Sect. 4. Transformer utilization is also demonstrated as an inductor area reduction technique in Sect. 5. Section 6 outlines predictions of stochastic resonance application to future signal detection and A/D conversion techniques based on numerical simulations.

# 2. Forward Body Biasing Technique

For logic circuits and SRAM operating at ultra-low voltage ( $\leq 0.6 \text{ V}$ ), dynamic-threshold (DT)-MOS [4]–[6] and active-body-biasing techniques [7] have already been proposed. These techniques utilize the forward body bias effect with tied gate and body to realize a device with a low  $V_{TH}$  at the on-state with low off-state leakage current. Forward body biasing has other advantages, such as (1) reduction of the short channel effect [6] and (2) reduction of the  $V_{TH}$  mismatch due to random dopant fluctuations [7]. Focusing on the latter, the standard deviation of  $V_{TH}$ ,  $\sigma_{VTH}$ , among MOS devices with the same gate length L and width W on the same chip is expressed as [8]–[10]

$$\sigma_{VTH} = \frac{A_{VTH}}{\sqrt{LW}},\tag{1}$$

where  $A_{VTH}$  is constant, depending on the process technology and body bias. Therefore, device scaling deteriorates matching, which is important in analog circuit design [11]. Under careful consideration, Eq. (1) is expected to be applied to estimate the  $V_{TH}$  mismatch, even in advanced structures of MOS devices, such as fully-depleted siliconon-insulator (FD-SOI) devices [12]. This issue is essential in device scaling. Forward body biasing can reduce  $A_{VTH}$  through a decrease of the depletion layer width.

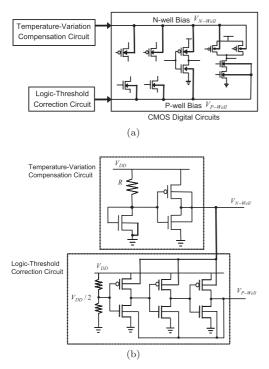

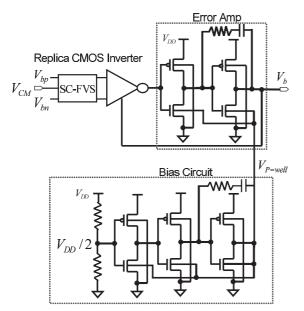

Forward body biasing is also useful to compensate device characteristic variations due to process and temperature. Figure 1 shows a simple implementation for 0.5 V logic circuits [13]. The temperature-variation compensation circuit compensates the threshold voltage of PMOS through its body. The logic-threshold correction circuit assures a balance between the drivability of the PMOS and NMOS de-

<sup>&</sup>lt;sup>†</sup>The authors are with Osaka University, Suita-shi, 565-0871 Japan.

**Fig. 1** (a) Compensation of device characteristic variations with forward body biasing, and (b) corresponding control circuits.

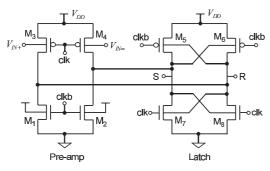

Fig. 2 A body-input gate-clocked comparator.

vices by monitoring the logic threshold voltage of a replica inverter.

For dynamic operation with a body terminal, the body resistance and parasitic capacitances [6] must be considered. The time constant related to the body is generally larger than that of the gate electrode. When signals applied to the gate and body are different, the lower-frequency signal can be selected to apply to the body in terms of speed. Note that the forward body biasing technique requires a triple-well CMOS structure. Latch-up in the circuit is avoided, because a 0.5 V supply cannot switch on the emitter-base junction of parasitic bipolar transistors.

A body-input gate-clocked comparator has been proposed, which employs body terminals of transistors for signal input (lower-frequency) while the gate terminals are used for clock input (higher-frequency) [14], [15]. Figure 2 shows that the comparator consists of pre-amp and latch stages, operating when the clock is 'LOW' and 'HIGH', re-

**Fig. 3** Boot-strapped single NMOS switch with a local charge pump circuit.

spectively. The differential input signal with the common-mode level of  $V_{CM}$  is amplified by the body transconductance of the input PMOS transistors, and then latched by the following stage, which consists of two cross-coupled body-input inverters. Note that the body terminals of the NMOS transistors in the pre-amp are forward biased to ensure rapid on-state operation of the NMOS side in our work [15].

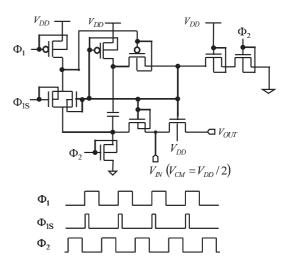

A signal with common-mode level at  $V_{DD}/2$  is not sufficient to turn on a transistor switch with a 0.5 V supply. An effective solution is to employ a voltage higher (in the case of NMOS) than the supply with a charge pump to control the switch transistor gate. Figure 3 shows a boot-strapped single NMOS switch with a local charge pump circuit [15]. This boot-strapping circuit is fundamentally similar to previously proposed one [16] except for the forward body biasing. This allows rail-to-rail switch operation while limiting all gate-source and body-source voltages, and avoids any overstress in the gate oxide and body-source junction. Clock  $\Phi_{1S}$  only gives sampling trigger at the beginning of  $\Phi_1$ .

#### 3. Inverter-Based Circuit Topology

To develop a high-performance analog circuit with the condition of  $V_{DD}$  close to  $V_{TH}$ , such as for a 0.5 V supply, the advantages of the CMOS inverter's high transconductance and good compatibility with digital circuits can be utilized. However, for a 0.5 V supply, the DC common-mode voltage is set to 250 mV and may cause weak inversion operation of the CMOS transistors for a typical transistor threshold voltage  $V_{TH}$  of approximately 450 mV. In order to achieve high performance transistor operation, techniques such as level shifting with a floating voltage source (FVS) [17], [18] are used to increase the gate-source voltage, thus achieving higher performance of analog circuits.

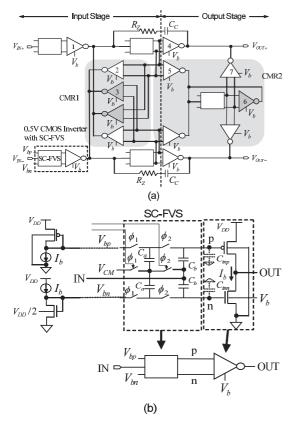

Figure 4 shows the proposed inverter-based operational amplifier (op-amp) used for switched-capacitor applications [15]. The proposed circuit is based on a previously proposed CMOS amplifier [19]. The op-amp mainly consists

Fig. 4 (a) Inverter-based op-amp and (b) inverter with SC-FVS circuit.

Fig. 5 Common-mode voltage adjustment circuit.

of four 0.5 V CMOS inverters with switched-capacitor floating voltage sources (SC-FVS), and two common-mode rejection circuits denoted CMR1 and CMR2 [20]. SC-FVS circuits are used to increase the gate-source voltage of the PMOS and NMOS transistors, while the two common-mode rejection circuits CMR1 and CMR2 increase the common-

mode rejection ratio (CMRR) and stabilize the DC output common-mode level. Given the total transconductance and output impedance of each inverter (1~7)  $g_{m1\sim7}$  and  $r_{o1\sim7}$ , respectively, the differential DC gain is given by

$$Gain = \frac{g_{m1}g_{m4}(r_{o4}//r_{o7})}{1/(r_{o1}//r_{o2}) - (g_{m2} - g_{m3})}.$$

(2)

Inverters 4 and 7 with the same size  $(g_{m4} = g_{m7})$  are used. The CMRR is represented by

$$CMRR = \frac{1/r_{o1} + g_{m2} + g_{m3}}{1/(r_{o1}//r_{o2}) - (g_{m2} - g_{m3})} \times \frac{1/r_{o5} + g_{m6}}{1/r_{o5} - (g_{m5} - g_{m6})}.$$

(3)

Equations (2) and (3) show that the DC gain and CMRR can be enhanced by slight changes in the size ratios of inverters 2 and 3, and inverters 5 and 6, respectively.

All the bodies of the NMOS transistors in the inverters are forward biased and are employed as common-mode feedback terminals,  $V_b$ , to provide accurate control of the DC common-mode output voltage and maintain good independence of process and temperature variations.

Figure 4(b) illustrates the detail of the SC-FVS blocks. The current mirrors provide accurate control of the quiescent current  $I_b$  flowing through the inverter [17]. All switches are controlled by nonoverlap clocks  $\phi_1$  and  $\phi_2$ .  $V_{bp}$ and  $V_{bn}$  are set to 0.1 and 0.4 V, respectively, so that there is no bootstrapped switch required at these two paths. The other two switches connected with  $V_{CM}$  are added to stabilize the DC common-mode output level, in comparison to the circuit in our previous work [20]. These two switches require clocks with higher levels than  $V_{DD}$  to ensure switching operation, and this requirement is met by the bootstrapped clock switches shown in Fig. 3. Each switching cycle refreshes the capacitors  $C_b$ , which maintains the voltage difference,  $V_{bn}$ - $V_{bp}$ , between the inverter input nodes 'n' and 'p.' At the same time, the forward body bias lowers the  $V_{TH}$ by approximately 100~150 mV for a 0.18 μm CMOS process. Thus, the transistors operate in the moderate or even strong inversion region ( $|V_{GS}| \ge V_{TH}$ ), even under such a lowvoltage supply.

Figure 4(b) shows that a gain degradation of approximately  $C_b/(C_b+C_{in})$  is caused by the parasitic capacitances  $C_{inp}$  and  $C_{inn}$  (assume  $C_{inp} = C_{inn} = C_{in}$ ), which can be reduced by using a large  $C_b$ . A large  $C_b$  also alleviates the effect of charge injection during switching, but induces an area penalty. Therefore,  $C_b$  with a size greater than 5 times that of  $C_{in}$  was adopted for the design of the 0.5 V feedforward  $\Delta$ - $\Sigma$  A/D modulator described in Sect. 4, while keeping the area and gain degradation small.

A replica inverter circuit with SC-FVS and an error amplifier, as reported in previously proposed ones [20], [21] were employed to provide the common-mode feedback voltage  $V_b$  in Fig. 4. Figure 5 shows the common-mode voltage adjustment circuit. When NMOS rather than PMOS devices are used for common-mode adjustment, the total sizes of

the MOS devices can be reduced. This technique can accurately set the DC common-mode output voltage to  $V_{DD}/2$  with good independence of process and temperature variations, and the PMOS and NMOS transistors need not be carefully sized.

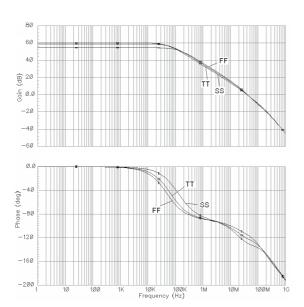

Figure 6 indicates the corner simulation results of the op-amp designed with a 0.18  $\mu$ m CMOS process. Under typical conditions (TT, 25°C), the op-amp has an open loop DC gain of 59 dB, a unity gain bandwidth of 42 MHz and a phase margin of 60° with a load of 8 pF. The power consumption is 168  $\mu$ W. Additionally, the inverter-based op-amp shows excellent common-mode gain characteristics in the high frequency range, in addition to a good figure of merit (FOM;  $\eta = (V_{DD} \cdot \text{GBW} \cdot C_L)$ /Power) compared with other conventional 0.5 V op-amps [21].

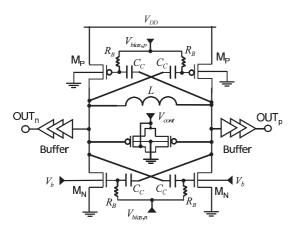

Such a CMOS-inverter-based approach can also be applied to some RF circuits. The recently developed 5 GHz CMOS voltage-controlled-oscillator(VCO) operating with a 0.5 V supply uses CMOS inverters with capacitive coupling

Fig. 6 Corner simulations of the proposed op-amp in open loop.

**Fig. 7** Schematic of a low-voltage complementary cross-coupled LC-VCO.

to ensure strong inversion operation [22]. The CMOS VCO can be easily modified to realize good independence of process and temperature variations through the forward body biasing scheme, as shown in Fig. 7. The gate biases of the MOS devices in the VCO core can be optimized for phase noise performance [22].

# Design of 0.5 V-Operation Feedforward Δ-Σ A/D Modulator

Wideband communication applications demand higher oversampling or higher order  $\Delta$ - $\Sigma$  A/D modulators to achieve the required performance. To meet such requirements, continuous-time (CT)  $\Delta$ - $\Sigma$  modulators have been widely developed [23]. However, a switched-capacitor (SC)  $\Delta$ - $\Sigma$  modulator is suitable for the CMOS-inverter-based opamp described in Sect. 3. In addition, the use of SC  $\Delta$ - $\Sigma$  modulators have proven to be a very robust and linear technique that has a manufacturing advantage, because it does not require any tuning compared with CT  $\Delta$ - $\Sigma$  modulator. In this section, a 4th-order  $\Delta$ - $\Sigma$  A/D modulator using a CMOS-inverter-based op-amp operating at 0.5 V supply is explained as an example [15].

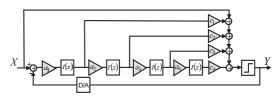

Full feedforward  $\Delta$ - $\Sigma$  topology was adopted with reduced sensitivity to integrator nonlinearities [24], making it appropriate in low-voltage wideband applications. Compared to feedback topology, the quantization noise transfer function of the feedforward topology remains the same and the signal transfer function is unity, so that it is difficult for this modulator to be affected by the non-idealities of analog building blocks. In this modulator, the internal signal swing can be well controlled by optimizing the loop coefficients, and thus significantly reducing modulator distortion. Furthermore, only one feedback D/A converter is required, which remarkably simplifies the feedback circuit, and is especially helpful for high-order design.

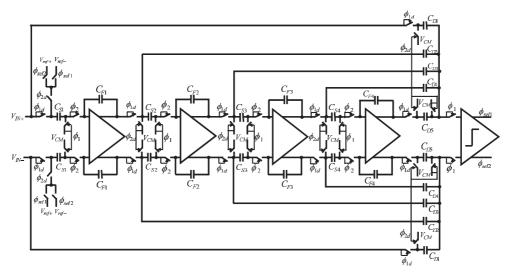

Figure 8 shows the topology of a 4th-order feedforward  $\Delta$ - $\Sigma$  A/D modulator [25]. It mainly consists of four inverter-based integrators, denoted as I(z), and a 1-bit comparator. The coefficients  $[a_1, a_2, a_3, a_4; c_1, c_2, c_3, c_4]$  are selected as [0.2, 0.4, 0.1, 0.1; 1, 1, 1, 2] to maintain loop stability. MATLAB behavior simulations show a good SNR, and each of the integrator output levels is limited in the range of  $0.1 \sim 0.4$  V under 0.5 V supply and with a reference voltage of  $V_{ref} = \pm 0.3$  V.

The circuit implementation of the designed low-voltage A/D modulator is shown in Fig. 9. The switched-capacitor integrator is used in this design. The body-input gate-

**Fig. 8** A 4th-order feedforward  $\Delta$ -Σ modulator.

Fig. 9 Circuit implementation of the designed A/D modulator.

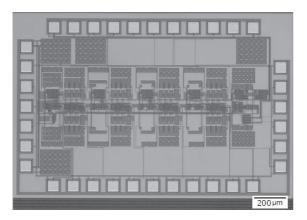

**Fig. 10** Micrograph of a 0.5 V feedforward  $\Delta$ -Σ A/D modulator fabricated in a 0.18  $\mu$ m CMOS process.

clocked comparator shown in Fig. 2, boot-strapped single NMOS switches as shown in Fig. 3, and the CMOS-inverter-based op-amp as shown in Fig. 4 are utilized in this design. At the same time, forward body biasing is used in the digital SR latch following the comparator and output buffers to increase the operation speed. The reference voltages of  $V_{ref\pm} = V_{CM} \pm 0.15 \, \text{V}$  are used, corresponding to  $V_{ref} = \pm 0.3 \, \text{V}$  in MATLAB behavior simulations.

However, the use of bootstrapping capacitance induces a large area penalty. Therefore, the switches in this design are classified. Each of the switches at a signal path has an individual bootstrapped clock circuit to reduce signal distortion, while the other switches connected with  $V_{CM}$  share bootstrapped clocks according to their clock phases. In this way the chip area is significantly decreased.

The feedforward  $\Delta$ - $\Sigma$  A/D modulator is designed in a standard 0.18  $\mu$ m CMOS process with metal-insulator-metal (MIM) capacitors and six metal layers with a 0.5 V supply. A micrograph of the chip is shown in Fig. 10. Excluding the bonding pads and other peripheral circuitry, the core area is approximately  $0.5 \times 1.5 \, \text{mm}^2$ . Figures 11 and 12

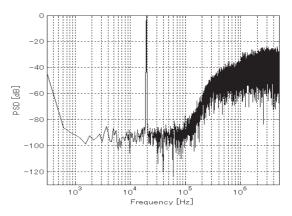

**Fig. 11** Measured output spectrum at  $V_{in} = -8 \, \mathrm{dB} V_{ref}$  (Spectrum computed with 32768-point FFT).

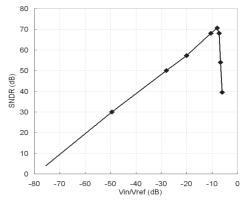

Fig. 12 Test SNDR vs. input amplitude.

show the output spectrum characteristics and the main performance parameters are summarized in Table 1. The sampling frequency is 10 MHz and the spectra are computed with a 32768-point fast Fourier transform (FFT). Test results show a good FOM, in that a peak SNDR of 71 dB is achieved for a 78 kHz signal bandwidth with power consumption of

**Table 1** Main performance of 0.5-V feedforward  $\Delta$ -Σ A/D modulator fabricated in 0.18  $\mu$ m CMOS process.

| Parameter                                              | This study |

|--------------------------------------------------------|------------|

| Supply [V]                                             | 0.5        |

| Sampling Frequency [MHz]                               | 10         |

| Bandwidth [kHz]                                        | 78         |

| SNDR [dB]                                              | 71         |

| Power [ $\mu$ W]                                       | 860        |

| FOM* [pJ/conv.]                                        | 1.9        |

| Op-amp DC Gain [dB]                                    | 59         |

| Op-amp UGB [MHz]                                       | 42         |

| Op-amp Power [ $\mu$ W]                                | 168        |

| *FOM= $\frac{Power}{2^{ENOB}\times 2\times Bandwidth}$ |            |

$860\,\mu\text{W}$  under 0.5 V supply.

# 5. Area-Efficient Transformer Folded-Cascode CMOS Low-Noise Amplifier

Continuous CMOS technology scaling imposes two challenges on RFICs; low-voltage operation and a small chip area. Previously reported low-voltage low-noise amplifiers (LNAs) [26]–[29] require many inductors, which increase both the chip area and the cost. Although folded-cascode LNAs [26], [29] are more suitable for low voltage operation  $(V_{DD} > V_{DS,sat})$ , they require more inductors, which leads to an increase in the chip area. In this section, a low-voltage transformer folded-cascode CMOS LNA is proposed [30].

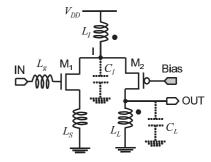

Figure 13 shows the proposed LNA based on a conventional folded-cascode LNA with inductive source degeneration. The gate and source inductors,  $L_q$  and  $L_s$ , provide input impedance matching at an operating frequency [31]. The PMOS transistor  $M_2$  reduces the Miller effect of the gatedrain capacitor of the input transistor  $M_1$ , and improves the reverse isolation performance of the LNA. The internal inductor  $L_I$ , resonates with parasitic capacitance  $C_I$  at node I and provides a high impedance, thereby the signal current amplified by  $M_1$  flows into  $M_2$ . The load inductor  $L_L$  also resonates with parasitic capacitance  $C_L$ , resulting in a high impedance. These inductors,  $L_I$  and  $L_L$ , are magnetically coupled to form a transformer in such a way so as to have positive magnetic coupling while retaining the LNA performance. The transformer shifts the peak of the LNA gain to a lower frequency. The peak frequency  $\omega_p$  is approximately

$$\omega_p \approx \sqrt{\frac{1 - nk}{1 - k^2}} \frac{1}{\sqrt{L_I C_I}},\tag{4}$$

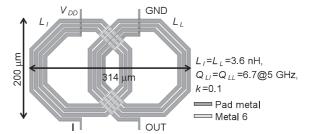

where  $n = \sqrt{L_L/L_I}$  and k are the turn ratio and coupling factor of the transformer, respectively. Based on careful consideration on peak frequency of the LNA gain, the partially coupled transformer ( $k \simeq 0.1$ ) shown in Fig. 14 can give less performance deterioration in input matching, peak gain, and NF, compared to the conventional one.

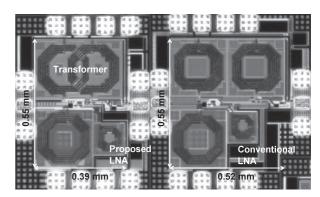

The proposed LNA was implemented in a 90 nm digital CMOS process. For comparison, the conventional folded-cascode LNA was also implemented on the same chip. Micrographs of the fabricated LNAs are shown in Fig. 15. The

Fig. 13 Schematic of the transformer folded-cascode CMOS LNA.

Fig. 14 Layout of a partially-coupled transformer.

**Fig. 15** Micrographs of the proposed LNA (left) and conventional folded-cascode LNA (right), fabricated in a 90 nm digital CMOS process.

active chip areas (excluding pads) of the proposed and conventional LNAs are  $0.39 \times 0.55 \,\mathrm{mm}^2$  and  $0.52 \times 0.55 \,\mathrm{mm}^2$ , respectively. The S-parameters, NFs, and linearity of the LNAs were measured using on-wafer RF probes. The power consumption, excluding the buffer, was 1.0 mW at a supply voltage of 0.5 V. The proposed LNA obtained  $|S_{11}|$  <  $-10 \,\mathrm{dB}$ ,  $|S_{21}| = 16.8 \,\mathrm{dB}$ , and NF = 3.9 dB at 4.7 GHz. The magnetic coupling in the proposed LNA had a small impact on the  $S_{11}$  and NF performance. Table 2 shows a summary of the performance and a comparison with previously reported low-voltage (< 0.7 V) CMOS LNAs for 5 GHz application. The proposed LNA achieved performance comparable with the conventional folded-cascode LNA, while having only 75% of the chip area of the conventional LNA. FoM in Table 2 is defined in Ref. [26], [30] Among the reported low-voltage CMOS LNAs, the proposed LNA obtained the best FoM with the smallest chip area.

Recently, we developed an ultra-wideband (UWB)

| Reference          | CMOS<br>Technology | Frequency<br>[GHz] | NF<br>[dB] | Gain<br>[dB] | IIP <sub>3</sub> [dBm] | P <sub>in-1 dB</sub><br>[dBm] | Supply [V] | Power [mW] | Area [mm <sup>2</sup> ] | FOM [mW <sup>-1</sup> ] |

|--------------------|--------------------|--------------------|------------|--------------|------------------------|-------------------------------|------------|------------|-------------------------|-------------------------|

| This work          | 90 nm              | 4.7                | 3.9        | 16.8         | -14.8                  | -27                           | 0.5        | 1.0        | 0.21                    | 4.8                     |

| Folded-cascode LNA | 90 nm              | 5.0                | 4.1        | 16.1         | -14.8                  | -27                           | 0.5        | 1.0        | 0.29                    | 4.1                     |

| [26]               | 90 nm              | 5.5                | 3.6        | 9.2          | -7.25                  | -15.8                         | 0.6        | 1.0        | 0.30                    | 2.2                     |

| [27]               | 130 nm             | 5.1                | 5.3        | 10.3         | N/A                    | -22                           | 0.4        | 1.0        | 0.75                    | 1.4                     |

| [28]               | 180 nm             | 5.0                | 4.5        | 9.2          | -16                    | -27                           | 0.6        | 0.9        | 0.54                    | 1.8                     |

| [29]               | 180 nm             | 5.8                | 2.9        | 7.0          | N/A                    | -9                            | 0.7        | 12.5       | 0.40                    | 0.2                     |

| [32]               | 180 nm             | 5.0                | 3.65       | 14.1         | -17.1                  | -25                           | 0.6        | 1.68       | 0.46                    | 2.3                     |

| _                  |                    |                    |            |              |                        |                               |            |            |                         |                         |

**Table 2** Measured performance and comparison of low-voltage CMOS LNAs.

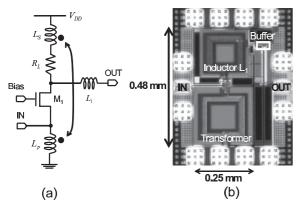

**Fig. 16** (a) Proposed transformer noise-canceling UWB CMOS LNA and (b) micrograph of the LNA fabricated in a 90 nm digital CMOS process.

CMOS LNA with transformer noise-canceling [33], as shown in Fig. 16. The transformer composed of magnetically coupled inductors  $L_p$  and  $L_s$  cancels the noise produced by  $M_1$  and the load resistor  $R_L$ . This transformer technique can also contribute to chip area reduction. One approach to chip area reduction is the use of transformers instead of inductors. The transformer in the UWB LNA shown in Fig. 16 is a fully-coupled type used to enhance noise canceling.

### 6. Signal Detection Suitable to Mismatch and Noise

Receiver architectures based on conventional A/D converters are approaching their limit in maintaining resolution under low-voltage operation [11], [34]. Even if A/D converters follow the gain stages of amplifiers in the receiver chain to maintain resolution, the amplifiers themselves will have difficulty in retaining nonlinear-distortion with sufficient gain under such a low supply voltage. For example, comparison with linear-in-dB variable gain amplifiers (VGAs) with almost the same topology, which are designed under different supply voltages and different process technologies (2.5 V in a  $0.25 \,\mu \text{m}$  CMOS process and  $1.5 \,\text{V}$  in a  $150 \,\text{nm}$  FD-SOI CMOS process), reveals scaling merits in bandwidth and occupied area, while they can have only similar IIP3, NF, and gain ranges by adjusting the central value of gain [35], [36]. If a larger gain is set under a low supply voltage, the VGAs have less linearity (smaller IIP3). Therefore, new signal detection techniques to break through this limitation have be-

Fig. 17 Schematic diagram of the proposed signal detection system.

come an urgent research target.

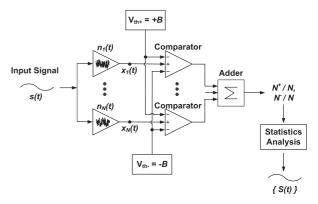

Although noise-aided detection of weak signals in neurons has been the subject of considerable attention in connection with the phenomenon of stochastic resonance (SR) [37], [38], recent research has also demonstrated SR in nanoscale electron devices [39], [40]. As described in the comprehensive review by Gammaitoni et al. [38], the SR phenomenon can be generally observed in bistable threshold-based systems that are forced by both of two components: (1) a signal with an amplitude lower than the system threshold, and (2) noise that is inherent in the system. This phenomenon can be interpreted as a reduction in system threshold, which is simply modeled using Brownian particles in a quartic-double-well potential [38]. Recently, a novel subthreshold signal detection technique was developed for a communication system, which is suitable for implementation in future nanoscale CMOS technology [41]. This section briefly introduces this faint-signal detection technique.

Figure 17 shows a schematic representation of the proposed system. Using an analog comparator as a detection device, it is assumed that the input signal of the comparator is smaller than the noise level, in addition to the threshold value. As the input signal is shared with N amplifiers of the same gain, each output signal x(t) is the sum of the amplified input signal and the inherent yet uncorrelated noise generated in each amplifier. The comparator then converts the output signal x(t) to a digital signal by comparison with the threshold levels, +B and -B. From the N comparator outputs, the number of output signals that are larger than +B is represented as  $N^+$ , and that smaller than -B as  $N^-$ . As a

result, two output values,  $N^+$  and  $N^-$ , are obtained from one input signal s(t).

Note that the thermal and shot noise in electrical devices are represented as typical Gaussian white noise [42]. Under such Gaussian white noise, the input signal s(t) can be restored from the probability for detection of a signal using the time or ensemble statistics of the comparator outputs, that is,  $N^+/N$  and  $N^-/N$ , as follows.

$$S(i) = \begin{cases} B - \sqrt{2} \,\sigma_n \operatorname{erf}^{-1} \left\{ 2 \left( \frac{1}{2} - \frac{N^+}{N} \right) \right\} \\ (N_i^+ > N_i^-), \\ -B - \sqrt{2} \,\sigma_n \operatorname{erf}^{-1} \left\{ 2 \left( \frac{N^-}{N} - \frac{1}{2} \right) \right\} \\ (N_i^+ < N_i^-), \\ 0 \qquad (N_i^+ = N_i^-). \end{cases}$$

(5)

Here  $\sigma_n$  is the standard deviation of the noise, and S(i) represents the sample value of s(t) at  $t = i T_s$  ( $i = 0, 1, 2, \cdots$ ), where  $T_s$  is the sampling period.

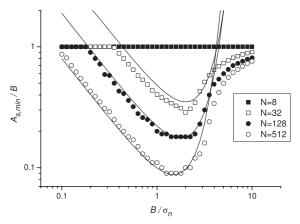

In order to estimate the detection sensitivity or limit of the proposed system, numerical simulations are carried out under a set-up of unity gain amplifiers for simplification. For the m-phase-shift-keying (m-PSK) modulated input signal, a bit error rate (BER) less than or equal to  $10^{-3}$  is required for reliable signal detection in typical wireless communications, which provides the detection sensitivity for the subthreshold signal. The minimum amplitude of the input signal satisfying this requirement,  $A_{s,min}$ , can be obtained by the numerical simulations.  $A_{s,min}/B$  is used as the detection sensitivity, which is normalized by the threshold B. A smaller  $A_{s,min}/B$  indicates better detection sensitivity.

The numerical simulation results shown in Fig. 18 can be approximated by

$$\frac{A_{s,min}}{B} = \frac{P}{Q} \sqrt{\frac{m}{OSR \times N}} \frac{\sigma_n}{B} \exp\left(Q^2 \frac{B^2}{2\sigma_n^2}\right),\tag{6}$$

where  $P \approx 2.4$  and  $Q = (\sigma_n/B)_{\rm opt}$  are fitting parameters. The deduction of Eq. (6) is described in Ref. [41]. For large N, Eq. (6) explains the detection behavior very well. As seen in Fig. 18, the increase of N can enhance the detection sensitivity and also provide a slightly wider margin for the optimal threshold value. This behavior is similar to that in many SR systems [37]–[40].

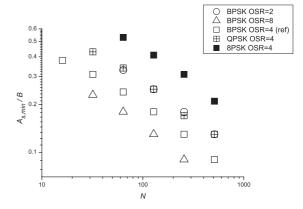

Figure 19 reveals the enhancement in detection sensitivity with the increase of N and oversampling ratio (OSR). This indicates that the performance of the proposed architecture can be improved with scaling-down of the integrated circuit. The detection sensitivities for the QPSK and 8PSK modulated input signals differ from that for BPSK by a factor  $\sqrt{2}$  and 2, respectively. This means that OSR or N should be doubled and quadrupled for the QPSK and 8PSK input signals, respectively, to achieve the same sensitivity as that for BPSK. These results are consistent with the theoretical results from Eq. (6).

**Fig. 18** Detection sensitivity  $A_{s,min}/B$  as a function of  $B/\sigma_n$  (OSR = 4, BPSK). The solid lines represent the data approximated using Eq. (6).

**Fig. 19** Detection sensitivity  $A_{s,min}/B$  as a function of N, OSR and m-PSK  $(B/\sigma_n=1.77)$ .

Device parameter mismatches in the chip tend to limit the resolution of many analog integrated circuits [11]; therefore, acceptable parameter mismatches were investigated for the proposed signal detection system. In the proposed system, the mismatch of each arrayed circuit can be evaluated equivalently as DC noise. Thus, the total noise and device mismatch can be expressed as

$$\sigma_{total} = \sqrt{\sigma_n^2 + \sigma_{th}^2 + \sigma_{gain}^2 A_s^2 / G^2},\tag{7}$$

where  $\sigma_n$ ,  $\sigma_{th}$  and  $\sigma_{gain}$  are the standard deviations of noise, comparator threshold B, and amplifier gain G, respectively. The mismatches of threshold and gain approximately follow the Gaussian distribution, which is based on experimental device mismatch data [9], [10]. The numerical simulation results shown in Fig. 20 reveals no degradation in performance for the proposed signal detection system, even for 20% parameter mismatches, and even exhibits sensitivity improvement in the case of high threshold. These results indicate that the parameter mismatches are effectively equivalent to the DC noise. Recently, a flash A/D converter using offset variations of comparators instead of references was reported [43]. The performance of the flash A/D converter supports the present numerical simulations.

**Fig. 20** Detection sensitivity with consideration of the variation in (a) gain, and (b) threshold (OSR = 4, BPSK).

The proposed signal detection technique can have superior detection sensitivity, beyond that of conventional A/D-converter-based CMOS receivers, and provide a solution for maintaining resolution under low-voltage operation. In addition, improved performance in signal restoration is expected when combined with a q-bit A/D converter (q > 2). In other words, the proposed technique can provide superresolution features beyond the LSB of conventional q-bit A/D converters. This feature is useful for high-speed A/D converters with low-to-moderate resolution that can easily have scaling advantages. Even in  $\Delta$ - $\Sigma$  A/D modulators, SR may help to enhance resolution [44]. Whereas dynamic element matching, which is applied for the improvement of D/A converters and programmable gain amplifiers [45], [46], relaxes the influence of device mismatches on circuit precision, this technique instead utilizes device mismatches.

This technique is at an early stage of development; therefore, there is much room for further investigation, such as circuit design. However, it is our belief that the proposed technique will provide a new design paradigm for wireless receivers.

#### 7. Conclusions

There are some techniques available to achieve low-voltage

analog circuits, such as forward body biasing, inverter-based circuit techniques, area-efficient passive elements, and SR signal detection. Forward body biasing can enhance device drivability while maintaining low off-state leakage current. This technique is also useful to compensate for device characteristic variations due to process and temperature. Inverter-based circuit techniques ensure the possibility of analog CMOS circuit utilization when digital CMOS circuits can be realized. Use of area-efficient passive elements, such as transformers in RF circuits, can reduce the total occupation area of the passive elements. Although the area efficiency may not be sufficient, it is one promising technique for analog-centric RF circuit designs. Although application of SR to CMOS signal detection circuits is in the early stage of development, it promises to provide a new design paradigm for ultra-low-voltage analog circuit design.

# Acknowledgments

This work was supported by the Semiconductor Technology Academic Research Center (STARC), the Industrial Technology Research Grant Program in 2006 from the New Energy and Industrial Technology Development Organization (NEDO) of Japan, and the Global COE Program, "Center for Electronic Devices Innovation," from the Ministry of Education, Culture, Sports, Science and Technology of Japan. In addition, this work was partially supported by the Japan Society for the Promotion of Science (JSPS) for Grants-in-Aid for Scientific Research (C) (#20560324). Chip fabrication in this study was also supported by the University of Tokyo in collaboration with Synopsys, Inc. and Cadence Design Systems, Inc.

#### References

- Semiconductor Industry Association, "International technology roadmap for semiconductors 2007 edition." Available: http://www. itrs.net/

- [2] A. Matsuzawa, "Analog IC technologies for future wireless systems," IEICE Trans. Electron., vol.E89-C, no.4, pp.446–454, April 2006.

- [3] A. Matsuzawa, "Digital-centric RF CMOS technologies," IEICE Trans. Electron., vol.E91-C, no.11, pp.1720–1725, Nov. 2008.

- [4] F. Assaderaghi, D. Sinitsky, S.A. Parke, J. Bokor, P.K. Ko, and C. Hu, "Dynamic threshold-voltage MOSFET (DTMOS) for ultralow voltage VLSI," IEEE Trans. Electron Devices, vol.44, no.3, pp.414–422, March 1997.

- [5] H. Kotaki, S. Kakimoto, M. Nakano, T. Matsuoka, K. Adachi, K. Sugimoto, T. Fukushima, and Y. Sato, "Novel bulk dynamic threshold voltage MOSFET (B-DTMOS) with advanced isolation (SITOS) and gate to shallow-well contact (SSS-C) processes for ultra low power dual gate CMOS," 1996 International Electron Device Meeting, pp.459–462, San Francisco, Dec. 1996.

- [6] A. Shibata, T. Matsuoka, S. Kakimoto, H. Kotaki, M. Nakano, K. Adachi, K. Ohta, and N. Hashizume, "Ultra low power supply voltage (0.3 V) operation with extreme high speed using bulk dynamic threshold voltage MOSFET (B-DTMOS) with advanced fast-signal transmission shallow well," 1998 Symposium on VLSI Technology, pp.76–77, Honolulu, June 1998.

- [7] Y. Hirano, M. Tsujiuchi, K. Ishikawa, H. Shinohara, T. Terada, Y. Maki, T. Iwamatsu, K. Eikyu, T. Uchida, S. Obayashi, K. Nii,

- Y. Tsukamoto, M. Yabuuchi, T. Ipposhi, H. Oda, and Y. Inoue, "A robust silicon-on-insulator static-random-access-memory architecture by using advanced actively body-bias controlled technology," Jpn. J. Appl. Phys., vol.47, no.4, pp.2092–2096, April 2008.

- [8] M.J.M. Pelgrom, A.C.J. Duinmaijer, and A.P.G. Welbers, "Matching properties of MOS transistors," IEEE J. Solid-State Circuits, vol.24, no.5, pp.1433–1440, Oct. 1989.

- [9] Y. Shimizu, M. Nakamura, T. Matsuoka, and K. Taniguchi, "Test structure for precise measurement of MOSFET matching properties," IEICE Trans. Electron (Japanese Edition), vol.J86-C, no.7, pp.726–733, July 2003.

- [10] Y. Shimizu, M. Nakamura, T. Matsuoka, and K. Taniguchi, "Test structure for precise measurement of MOSFET matching properties," Electron. Commun. Jpn 2, Electron, vol.87, no.3, pp.21–28, 2004

- [11] K. Uyttenhove and M.S.J. Steyaert, "Speed-power-accuracy tradeoff in high-speed CMOS ADCs," IEEE Trans. Circuits Syst. II, vol.49, no.4, pp.280–287, April 2002.

- [12] Y. Shimizu, T. Matsuoka, and K. Taniguchi, "Threshold voltage mismatch of FD-SOI MOSFETs," IEICE Trans. Electron., vol.E87-C, no.6, pp.1013–1014, June 2004.

- [13] K. Yasue, J. Wang, T. Matsuoka, and K. Taniguchi, "Characteristics compensation of ultra-low-voltage CMOS digital circuits," IEICE Trans. Electron. (Japanese Edition), vol.J93-C, no.2, pp.75–77, Feb. 2010.

- [14] K.P. Pun, S. Chatterjee, and P. Kinget, "A 0.5-V 74-dB SNDR 25-kHz continuous-time Delta-Sigma modulator with a return-toopen DAC," IEEE J. Solid-State Circuits, vol.42, no.3, pp.496–507, March 2007.

- [15] J. Wang, T. Matsuoka, and K. Taniguchi, "A 0.5 V feedforward delta-sigma modulator with inverter-based integrator," 35th European Solid-State Circuits Conference, pp.328–331, Athens, Sept. 2009

- [16] M. Dessouky and A. Kaiser, "Input switch configuration suitable for rail-to-rail operation of switched-opamp circuits," Electron. Lett., vol.35, no.1, pp.8–10, Jan. 1999.

- [17] F. Munoz, A. Torralba, R.G. Carvaja, and J. Ramirez-Angulo, "Two new VHF tunable CMOS low-voltage linear transconductors and their application to HF GM-C filter design," Proc. IEEE Int. Symp. Circuits and Systems, Geneva, vol.V, pp.173–176, May 2000.

- [18] R.G. Carvajal, A. Torralba, J. Ramirez-Angulo, J. Tombs, and F. Munoz, "Low voltage class AB output stages for CMOS op-amps using floating capacitors," Proc. IEEE Int. Symp. Circuits and Systems, vol.I, pp.14–16, Geneva, May 2000.

- [19] B. Nauta, "A CMOS transconductance-C filter technique for very high frequencies," IEEE J. Solid-State Circuits, vol.27, no.2, pp.142–153, Feb. 1992.

- [20] J. Wang, T.-Y. Lee, D.-G. Kim, T. Matsuoka, and K. Taniguchi, "Design of a 0.5 V Op-Amp based on CMOS inverter using floating voltage sources," IEICE Trans. Electron., vol.E91-C, no.8, pp.1375– 1378, Aug. 2008.

- [21] S. Chatterjee, Y. Tsividis, and P. Kinget, "0.5-V analog circuit techniques and their application in OTA and filter design," IEEE J. Solid-State Circuits, vol.40, no.12, pp.2373–2387, Dec. 2005.

- [22] F. Yamashita, T. Matsuoka, T. Kihara, I. Takobe, H.-J. Park, and K. Taniguchi, "Analytical design of a 0.5V 5GHz CMOS LC-VCO," IEICE Electronics Express, vol.6, no.14, pp.1025–1031, July 2009.

- [23] Y.L. Guillou, "Analyzing sigma-delta ADCs in deep-submicron CMOS technologies," RF Design, pp.18–26, Feb. 2005.

- [24] J. Silva, U. Moon, J. Steensgaard, and G.C. Temes, "Wideband low-distortion delta-sigma ADC topology," Electron. Lett., vol.37, no.12, pp.737–738, June 2001.

- [26] D. Linten, L. Aspemyr, W. Jeamsaksiri, J. Ramos, A. Mercha,

- S. Jenei, S. Thijs, R. Garcia, H. Jacobsson, P. Wambacq, S. Donnay, and S. Decoutere, "Low-power 5 GHz LNA and VCO in 90 nm RF CMOS," Symp. VLSI Circuits Dig. Tech. Papers, pp.372–375, Honolulu, HI, June 2004.

- [27] D. Wu, R. Huang, W. Wong, and Y. Wang, "A 0.4-V low noise amplifier using forward body bias technology for 5 GHz application," IEEE Microw. Wireless Compon. Lett., vol.17, no.7, pp.543–545, July 2007.

- [28] H.H. Hsieh and L.H. Lu, "A CMOS 5-GHz micro-power LNA," IEEE Radio Frequency Integrated Circuits Symp. Dig. Papers, pp.31–34, Long Beach, CA, June 2005.

- [29] T.K.K. Tsang and M.N. El-Gamal, "Gain and frequency controllable sub-1 V 5.8 GHz CMOS LNA," Proc. IEEE Int. Symp. Circuits and Systems, pp.795–798, Scottsdale, AZ, May 2002.

- [30] T. Kihara, H.-J. Park, I. Takobe, F. Yamashita, T. Matsuoka, and K. Taniguchi, "A 0.5 V area-efficient transformer folded-cascode CMOS low-noise amplifier," IEICE Trans. Electron, vol.E92-C, no.4, pp.564–575, April 2009.

- [31] D.K. Shaeffer and T.H. Lee, "A 1.5 V, 1.5 GHz CMOS low noise amplifier," IEEE J. Solid-State Circuits, vol.32, no.5, pp.745–759, May 1997.

- [32] H.H. Hsieh, J.H. Wang, and L.H. Lu, "Gain-enhancement techniques for CMOS folded cascode LNAs at low-voltage operations," IEEE Trans. Microw. Theory Tech., vol.56, no.8, pp.1807–1816, Aug. 2008.

- [33] T. Kihara, T. Matsuoka, and K. Taniguchi, "A transformer noise-canceling ultra-wideband CMOS low-noise amplifier," IEICE Trans. Electron, vol.E93-C, no.2, pp.187–199, Feb. 2010.

- [34] R.H. Walden, "Analog-to-digital converter survey and analysis," IEEE J. Sel. Areas Commun., vol.17, no.4, pp.539–550, April 1999.

- [35] S. Cha, T. Hirose, M. Haruoka, T. Matsuoka, and K. Taniguchi, "A CMOS IF variable gain amplifier with exponential gain control," IEICE Trans. Fundamentals, vol.E88-A, no.2, pp.410–415, Feb. 2005.

- [36] S. Cha, Y. Shimizu, G. Kim, T. Matsuoka, and K. Taniguchi, "A 1-V 120-MHz FD-SOI CMOS linear-in-dB variable gain amplifier," IEICE Electronics Express, vol.2, no.7, pp.249–253, April 2005.

- [37] J.J. Collins, C.C. Show, and T.T. Imhoff, "Stochastic resonance without tuning," Nature, vol.376, pp.236–238, July 1995.

- [38] L. Gammaitoni, P. Hänggi, P. Jung, and F. Marchesoni, "Stochastic resonance," Rev. Mod. Phys., vol.70, no.1, pp.223–287, Jan. 1998.

- [39] I. Lee, X. Liu, C. Zhou, and B. Kosko, "Noise-enhanced detection of subthreshold signals with carbon nanotubes," IEEE Trans. Nanotechnol., vol.5, no.6, pp.613–627, Nov. 2006.

- [40] T. Oya, T. Asai, and Y. Amemiya, "Stochastic resonance in an ensemble of single-electron neuromorphic devices and its application to competitive neural networks," Chaos, Soliton and Fractals, vol.32, pp.855–861, 2007.

- [41] H. Ham, T. Matsuoka, and K. Taniguchi, "Application of noise-enhanced detection of subthreshold signals for communication systems," IEICE Trans. Fundamentals, vol.E92-A, no.4, pp.1012–1018, April 2009.

- [42] A. van der Ziel, Noise in Solid State Devices and Circuits, John Wiley & Sons, Toronto, 1986.

- [43] T. Sundström and A. Alvandpour, "Utilizing process variations for reference generation in a flash ADC," IEEE Trans. Circuits Syst. II, vol.56, no.5, pp.364–368, May 2009.

- [44] O. Oliaei, "Stochastic resonance in sigma-delta modulators," Electron. Lett., vol.39, no.2, pp.173–174, Jan. 2003.

- [45] R.J. van de Plassche, "Dynamic element matching for high-accuracy monolithic D/A converters," IEEE J. Solid-State Circuits, vol.11, no.6, pp.795–800, Dec. 1976.

- [46] J. Wang, T. Matsuoka, and K. Taniguchi, "A switched-capacitor programmable gain amplifier using dynamic element matching," IEEJ Transactions on Electrical and Electronic Engineering, vol.2, no.6, pp.600–607, Nov. 2007.

Toshimasa Matsuoka received his B.S., M.S. and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 1989, 1991 and 1996, respectively. During 1991–1998, he worked for Central Research Laboratories at Sharp Corporation, Nara, Japan, where he was engaged in the research and development of deep submicron CMOS devices and ultra thin gate oxides. Since 1999, he has been working for Osaka University, where he is currently Associate Professor. His current research

includes CMOS RF circuits and device modeling. Dr. Matsuoka is a member of the Japan Society of Applied Physics, the IEEE, and the IEEJ.

Jun Wang was born in Shandong, China, in 1977. She received her B.S. degree in electronic materials & devices in 1998 and her M.S. degree in microelectronics & solid state electronics in 2001 from South China University of Technology, Guangzhou, China, and a Ph.D. degree in electronic engineering from Osaka University, Osaka, Japan, in 2008. From 2001 to 2003, she worked for Avant! Microelectronics Co., Ltd and Synopsys Inc, Shanghai, China, where she was engaged in the research and development

of memory technology. She is currently working for Osaka University. Her current research interests are high performance analog-to-digital and digital-to-analog converters.

**Takao Kihara** received his B.S., M.S., and Ph.D. degrees in electronic engineering from Osaka University, Osaka, Japan, in 2005, 2006, and 2009, respectively. His current research interests include CMOS RF transceivers.

**Hyunju Ham** was born in Ulsan, Korea, in 1983. He received the B.S. and M.S. degrees in electronic engineering from Osaka University, Osaka, Japan in 2007 and 2009, respectively. He is currently pursuing a Ph.D. degree at Osaka University, Japan. His current research interests are analog-to-digital conversion.

Kenji Taniguchi received his B.S., M.S. and Ph.D. degrees from Osaka University, Osaka, Japan, in 1971, 1973 and 1986 respectively. From 1973 to 1986, he worked for Toshiba Research and Development Center, Kawasaki, Japan, where he was engaged in process modeling and the design of MOS LSI fabrication technology. He was a Visiting Scientist at Massachusetts Institute of Technology, Cambridge, from July 1982 to November 1983. Presently, he is a Professor of Electronics Engineering at

Osaka University. His current research interests include analog circuits, radio frequency circuits, device physics and process technology. Prof. Taniguchi is a member of the Japan Society of Applied Physics and the IEEJ, and a fellow of the IEEE.