PDF issue: 2024-04-19

# Soft-Error Resilient and Margin-Enhanced N-P Reversed 6T SRAM Bitcell

Yoshimoto, Shusuke Kawaguchi, Hiroshi Yoshimoto, Masahiko

#### (Citation)

IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 97(9):1945-1951

(Issue Date) 2014-09

(Resource Type) journal article

(Version)

Version of Record

(Rights)

copyright©2014 IEICE

(URL)

https://hdl.handle.net/20.500.14094/90002985

#### **PAPER**

## Soft-Error Resilient and Margin-Enhanced N-P Reversed 6T SRAM Bitcell

Shusuke YOSHIMOTO<sup>†a)</sup>, Hiroshi KAWAGUCHI<sup>†</sup>, and Masahiko YOSHIMOTO<sup>††</sup>, Members

SUMMARY This paper describes a soft-error tolerant and margin-enhanced nMOS-pMOS reversed 6T SRAM cell. The 6T SRAM bitcell comprises pMOS access and driver transistors, and nMOS load transistors. Therefore, the nMOS and pMOS masks are reversed in comparison with those of a conventional bitcell. In scaled process technology, The pMOS transistors present advantages of small random dopant fluctuation, strain-enhanced saturation current, and small soft-error sensitivity. The four-pMOS and two-nMOS structure improves the soft-error rate plus operating margin. We conduct SPICE and neutron-induced soft-error simulations to evaluate the n-p reversed 6T SRAM bitcell in 130-nm to 22-nm processes. At the 22-nm node, a multiple-cell-upset and single-bit-upset SERs are improved by 34% and 51% over a conventional 6T cell. Additionally, the static noise margin and read cell current are 2.04× and 2.81× improved by leveraging the pMOS benefits.

**key words:** robust SRAM, soft error rate, neutron particle, single bit upset, multiple cell upset, nucleus reaction

#### 1. Introduction

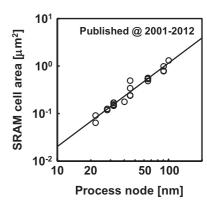

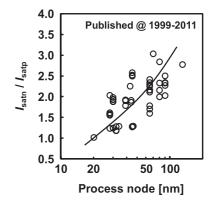

Process scaling continuously decreases an SRAM cell area by a factor of two in every technology generation, as presented in Fig. 1 [1], [2]. To scale CMOS transistors down to a 45-nm process or less, it is important to use compressive and tensile strain engineering for pMOS and nMOS, respectively, thereby increasing the drain current [3]. Particularly, for a pMOS, embedded SiGe (eSiGe) in a source and drain boosts its saturation current ( $I_{\text{satp}}$ ). The strain engineering is thereby more effective against  $I_{\text{satp}}$  than that in an nMOS (Isatn). Current enhancement using eSiGe strain for the pMOS increases more effective with the process scaling: +30% and +45% in a 45-nm and 22-nm processes [3], [4]. Figure 2 shows the trend of the saturation current ratio of an nMOS to a pMOS (=  $I_{\text{satn}}/I_{\text{satp}}$ ) along with a process node [5], [6]. The ratio becomes unity because  $I_{\text{satp}}$  is comparable with  $I_{\text{satn}}$  at a 22-nm node. In addition, the pMOS has less threshold voltage variation ( $V_{th}$  variation) because of lesser dopant fluctuation [7]. The standard deviation of the threshold voltage ( $\sigma_{Vth}$ ) of the pMOS is 25% less than that of nMOS [7].

The nanoscaled integrated circuits are susceptible to particle-induced single event effects because of their low signal charge [8]. Multiple cell upsets (MCUs) are caused by a collection of charge produced by secondary ions in a

Manuscript received December 11, 2013.

Manuscript revised May 5, 2014.

<sup>†</sup>The authors are with Kobe University, Kobe-shi, 657-8501 Japan.

††The author is with JST CREST, Kobe-shi, 657-8501 Japan.

a) E-mail: yoshipy@cs28.cs.kobe-u.ac.jp DOI: 10.1587/transfun.E97.A.1945

**Fig. 1** Process scaling trends of 6T SRAM cell areas published during 2001–2012 [1], [2].

**Fig. 2** Trend of saturation current ratios of  $I_{\text{satn}}$  to  $I_{\text{satp}}$  in 1999–2011 [3]–[6].

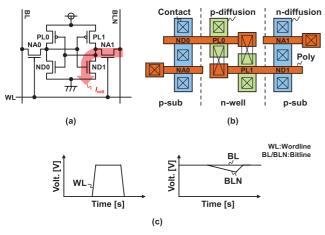

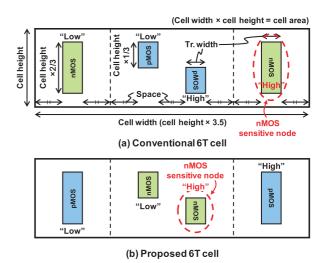

neutron-induced nuclear reaction. The ratio of the MCUs to single-event upsets (SEUs) is predicted to increase drastically in nanoscaled SRAMs [9]–[11]. Reportedly, the pMOS has less sensitivity to soft error effect than the nMOS [12]. The linear energy transfer threshold (*LET*<sub>th</sub>) of the pMOS is 1/4 of that of the nMOS. Figures 3(a), 3(b) and 3(c) respectively show a schematic, a layout and read waveforms of the conventional six transistor (6T) SRAM cell. The conventional 6T cell comprises pMOS load transistors (PL0 and PL1), nMOS driver transistors (ND0 and ND1), and nMOS access transistors (NA0 and NA1). The shared nMOS diffusion area (ND and NA) is larger than that of the pMOS (PL). The large nMOS is strongly affected by radiation strikes. In addition, the sensitive nMOS nodes are in the same p-well in the horizontal direction. Horizontal up-

**Fig. 3** (a) Schematic, (b) layout and (c) read waveforms of a conventional 6T SRAM cell. Cell current ( $I_{\text{cell}}$ ) flows through nMOS access and driver transistors in read operation.

sets can be incurred easily in the conventional 6T SRAM. An earlier report [13] describes that the nMOS-centered 6T SRAM cell can suppress the horizontal MCU by 67–98% because the horizontally adjacent nMOS nodes are separated by the n-well. However, the nMOS-centered 6T cell has area overhead because shared contacts cannot be applied [13].

As described above, the conventional 6T cell suffers from the shortcomings of the large  $V_{\rm th}$  variation and the softerror vulnerability in the nMOS driver transistors. To cope with these nMOS problems and to leverage the pMOS benefits, we propose using pMOS access and driver transistors instead: an n-p (nMOS-pMOS) reversed structure. A static noise margin, cell current, and soft-error tolerance are enhanced in the proposed n-p reversed 6T SRAM cell in future 22-nm node or advanced ones. Moreover, the horizontal MCU can be improved by the intrinsic nMOS-centered structure without area overhead.

The remainder of this paper is organized as follows. Section 2 presents the proposed n-p reversed 6T SRAM cell and setups for SPICE and soft-error simulations. In Sect. 3, simulation results are introduced with consideration of process scaling. Finally, Sect. 4 concludes this paper.

## 2. Proposed N-P Reversed 6T SRAM Cell and Simulation Setups

#### 2.1 N-P Reversed 6T SRAM Cell

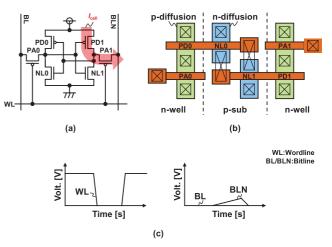

Figures 4(a), 4(b), and 4(c) respectively depict a schematic, a layout, and read waveforms of the proposed nMOS-pMOS (n-p) reversed 6T SRAM cell. The 6T cell consists of nMOS load transistors (NL0 and NL1), pMOS driver transistors (PD0 and PD1), and pMOS access transistors (PA0 and PA1). The number of transistors and the poly-gate alignment are similar, as depicted in Fig. 3(b), although the n-and p-diffusions are swapped. The shared contacts are applicable for both 6T cells. Therefore, the proposed cell has

**Fig. 4** (a) Schematic, (b) layout and (c) read waveforms of the proposed n-p reversed 6T SRAM cell. Cell current ( $I_{cell}$ ) flows through pMOS load and nMOS access transistors in read operation.

no area overhead over the conventional one. In a read operation, either bitline (BL or BLN in Fig. 4(a)) is pulled up by a cell current flowing through a pMOS access transistor. Generally, the read current of the proposed cell is degraded because  $I_{\text{satp}}$  is smaller than  $I_{\text{satn}}$ . However, as presented in Fig. 2, the saturation current ratio of  $I_{\text{satn}}$  to  $I_{\text{satp}}$  becomes smaller in the scaled process. Moreover, the random dopant fluctuation of the pMOS is less than that of the nMOS. Consequently, the cell current of the proposed cell will be larger than that of a conventional cell. This paper also investigates the breakpoint. The proposed cell decreases the soft-error rate because it has a 33% smaller nMOS diffusion area than a conventional cell. Moreover, the intrinsic nMOS-centered structure has horizontal-MCU resilience, which is similar to a previous study [13]. The horizontal pitch of the sensitive nMOS nodes is larger than those of conventional ones. Horizontally adjacent nMOSes do not share the same psubstrate.

#### 2.2 Simulation Setups for HSPICE and PHITS

Table 1 presents simulation parameters for the HSPICE circuit simulator and a particle transport code (PHITS) [14]. The supply voltage (VDD) and equivalent oxide thickness (EOT) for each process node are referred from ITRS 2001–2011 [15]. The standard deviations of the threshold voltages for nMOS and pMOS ( $\sigma_{\text{Vthn}}$  and  $\sigma_{\text{Vthp}}$ ) are normalized at the 65-nm node with the Stalk equation ( $\sigma_{\text{Vth}} \propto \text{EOT}/\sqrt{\text{(channel area: width} \times \text{length})}$ ) [16]. At the 65-nm node,  $\sigma_{\text{Vthn}}$  and  $\sigma_{\text{Vthp}}$  are 40 mV and 30 mV, respectively, for the minimum transistors, as derived from measurements of test chips [7]. The saturation current ratios ( $I_{\text{satn}}/I_{\text{satp}}$ ) and cell area are obtained using the fitting curves in Figs. 2 and 1. The critical charge is calculated at each node according to related reports [17], [18].

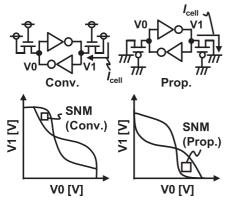

Figure 5 shows the circuit setup for HSPICE to estimate static noise margins (SNMs) of the conventional and proposed cells. The SNM is defined as a minimum square

**Table 1** Parameters in HSPICE and PHITS simulations.

| Process<br>node [nm] | VDD <sup>*1</sup><br>[V] | EOT <sup>*1</sup><br>[Å] | σ <sub>Vthn</sub> *2<br>[mV] | σ <sub>Vthp</sub> <sup>*2</sup><br>[mV] | / <sub>sat</sub> ratio <sup>*3</sup><br>(/ <sub>satn</sub> / / <sub>satp</sub> ) | Cell area <sup>*4</sup><br>[μm²] | Critical <sup>*5</sup><br>charge [fC] |

|----------------------|--------------------------|--------------------------|------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|----------------------------------|---------------------------------------|

| 22                   | 0.9                      | 12                       | 83.8                         | 62.9                                    | 1.01                                                                             | 0.0813                           | 0.224                                 |

| 32                   | 1.0                      | 15                       | 64.6                         | 48.5                                    | 1.40                                                                             | 0.1562                           | 0.285                                 |

| 45                   | 1.0                      | 19                       | 51.2                         | 42.9                                    | 1.84                                                                             | 0.2830                           | 0.430                                 |

| 65                   | 1.1                      | 21                       | 40.0                         | 30.0                                    | 2.26                                                                             | 0.5369                           | 0.793                                 |

| 90                   | 1.2                      | 24                       | 32.3                         | 24.2                                    | 2.70                                                                             | 0.9465                           | 1.700                                 |

| 130                  | 1.2                      | 27                       | 25.7                         | 19.3                                    | 3.08                                                                             | 1.7960                           | 3.300                                 |

<sup>1</sup>[10], <sup>2</sup>[7,11], <sup>3</sup>Fitting in Fig. 2, <sup>4</sup>Fitting in Fig. 1, <sup>5</sup>[17,18]

**Fig. 5** Circuit setup for Static Noise Margin (SNM) and  $I_{cell}$  estimation. The read margin is defined as a minimum square in butterfly curves.

Fig. 6 Flow chart of the soft-error rate simulator [20] using PHITS [9].

in butterfly curves in Monte Carlo simulations (20 K trials) [19]. Furthermore, the cell current ( $I_{\text{cell}}$ ) is taken from the minimum one by the SPICE Monte Carlo simulations, which reflects the readout speed.

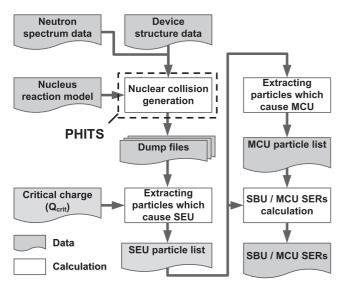

Figure 6 illustrates a flow chart of our neutron-induced soft error simulator [20] using PHITS. The input data for PHITS are neutron spectrum data, device structure data, and nucleus reaction models.

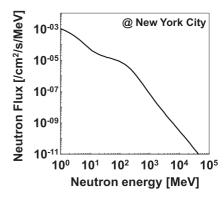

The cosmic-ray neutron spectrum is calculated using an Excel-based Program for calculating Atmospheric Cosmic-ray Spectrum (EXPACS) [21], as shown in Fig. 7.

Fig. 7 Cosmic-ray neutron flux normalized to ground level in New York City. Flux is calculated with EXPACS [16].

**Fig. 8** Models of SRAM cell width, height, and positions of sensitive nodes in 22-nm to 130-nm processes using parameters in Table 2.

Table 2

Size and position parameters in Fig. 8 for PHITS simulations.

|                 | Process node [nm] |       |       |       |       |       |  |  |  |

|-----------------|-------------------|-------|-------|-------|-------|-------|--|--|--|

|                 | 22                | 32    | 45    | 65    | 90    | 130   |  |  |  |

| Cell area [μm²] | 0.081             | 0.156 | 0.283 | 0.537 | 0.947 | 1.796 |  |  |  |

| Cell height [   | 0.152             | 0.211 | 0.284 | 0.392 | 0.520 | 0.716 |  |  |  |

| Cell width [µm] | 0.533             | 0.739 | 0.995 | 1.371 | 1.820 | 2.507 |  |  |  |

| Tr. width [μm]  | 0.044             | 0.064 | 0.090 | 0.130 | 0.180 | 0.260 |  |  |  |

| Space [μm]      | 0.051             | 0.069 | 0.091 | 0.122 | 0.157 | 0.210 |  |  |  |

The device structure includes the cell property (width, height, and position of sensitive nodes), a cell-to-cell pitch in a cell array, and data patterns. The cell height, width, and position of the sensitive nodes are modeled as presented in Fig. 8. The ratio of the cell height to the cell width is set as 3.5. Each transistor width is doubled from the process node to suppress threshold voltage variation. The diffusion area is derived from the transistor width and the cell height. The clearances between diffusion edged are all equal. The parameters are presented in Table 2.

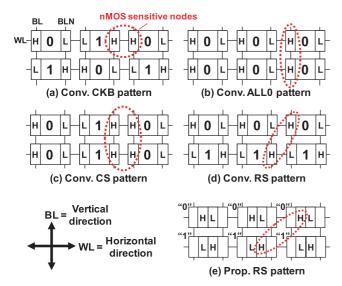

Figures 9(a)–9(d) respectively show four data patterns in a conventional memory cell array, with checkerboard

**Fig. 9** Data patterns for soft-error evaluation: (a) checker board (CKB), (b) all 0 (ALL0), (c) column stripe (CS), (d) row stripe (RS) patterns in the conventional SRAM cell array and (e) RS patterns in the proposed one. The red circles show nMOS sensitive nodes.

(CKB), all 0 (ALL0), column stripe (CS), and row stripe (RS) patterns. The red circles show nMOS sensitive nodes. As described in Sect. 1, the nMOS nodes share the same psubstrate in the horizontal direction, which possibly causes horizontal MCUs. However, the n-p reversed 6T cell has the nMOS transistors in the center of the cell, as shown in Fig. 9(e). The structure obtains the horizontal-MCU tolerance as well as the previous nMOS-centered 6T cell [13].

As a nucleus reaction model, the intra-nuclear cascade (INC) model [22] and the generalized evaporation model (GEM) [23] are used with a nucleus database: Japanese Evaluated Nuclear Data Library (JENDL-4.0) [24].

PHITS simulates the nucleus reaction and particle transportation. In the simulation, dump files are exported. They include the secondary ion particle states: atomic weight, nucleus reaction point (X, Y, Z), velocity vector (dX, dY, dZ), and energy per nucleon. If a particle crosses the surface of the sensitive volume, then the particle state at the cross point is also exported to the dump file. The deposit energy  $(E_{deposit})$  is calculated with the dump files in the respective sensitive nodes.

The deposit charge ( $Q_{deposit}$ ) is calculated using the following equation, in which e is the elementary charge.

$$Q_{deposit}[C] = \frac{e}{3.6} \times E_{deposit}[eV]$$

(1)

When a secondary particle deposits more than a critical charge ( $Q_{\rm crit}$ ) to at least one memory cell, that particle is classified as a single-event-upset (SEU) particle. Finally, single-bit-upset and multiple-cell-upset soft-error rates (SBU and MCU SERs) are calculated at every SEU particle event.

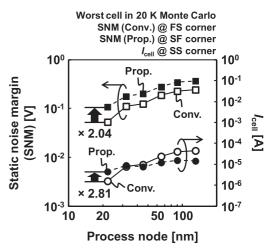

Fig. 10 SNM and  $I_{\rm cell}$  comparisons between conventional and proposed cells

#### 3. Simulation Results

## 3.1 Static Noise Margin (SNM) and Cell Current (*Icell*) Estimations with HSPICE

The SNMs of the conventional and proposed 6T SRAM cells are calculated using the 20 K Monte Carlo HSPICE simulations at the worst process corners: The FS (nMOS = Fast; pMOS = Slow) corner for the conventional cell and the SF corner for the proposed cell. The  $I_{cell}$  is calculated at the SS corner. Figures 10 shows that the SNM and  $I_{cell}$ of the worst cell are decreasing continuously with process scaling attributable to the reduced VDD and the increased  $\sigma_{\mathrm{Vth}}$ . The proposed cell, however, has a greater SNM and  $I_{\text{cell}}$  because the proposed cell has pMOS access and driver transistors and their  $\sigma_{\mathrm{Vthp}}$  is smaller than the  $\sigma_{\mathrm{Vthn}}$  in the conventional one. The SNM of the proposed cell is larger at every node and is 2.04 times as large at the 22-nm node. The  $I_{\text{cell}}$  in the proposed cell is larger than that in the conventional one at the 32-nm and less nodes and is 2.81 times as large at the 22-nm node. Simulation results show that the proposed n-p reversed 6T cell achieves greater read stability and faster readout operation than the conventional one in the scaled process.

### 3.2 Neutron-Induced Soft-Error Rate Calculation with PHITS

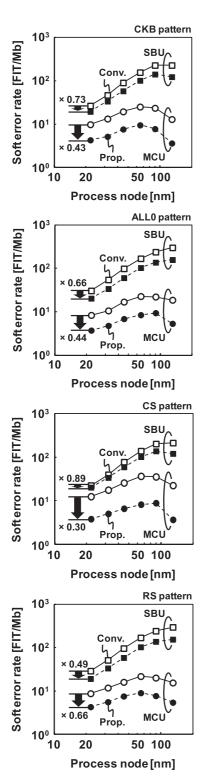

Figure 11 shows neutron-induced soft-error simulation results obtained using CKB, ALLO, CS, and RS patterns. Although the critical charge is decreasing, the SBU SER is also decreasing with process scaling thanks to the smaller critical area. The MCU SER exhibits a similar tendency at the 65-nm and less nodes. The proposed n-p reversed cell has 50% smaller nMOS diffusion area in our definition. Therefore, its SBU and MCU SERs are reduced respectively by 11–51% and 34–70% at the 22-nm node. Particularly for

Fig. 11 SBU and MCU SERs of conventional and proposed cells in the CKB, ALLO, CS and RS patterns.

the column stripe pattern, the MCU SER is improved by 70% (but the SBU SER is decreased by only 11%) because nMOS diffusions in the conventional cells share the same psubstrate in the vertical direction and vertical MCUs occur easily. However, in the row stripe pattern, the MCU SER

improvement is the smallest, 34% (but the SBU SER improvement is the largest, 51%), because the distance from a sensitive nMOS node to another in the conventional cells is the longest among the four patterns.

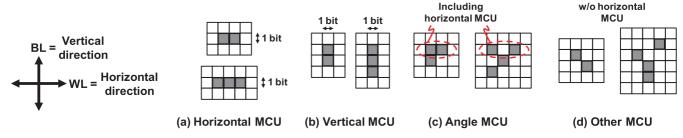

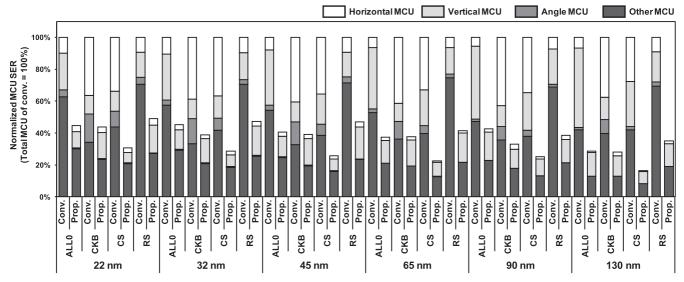

Figures 12(a)–12(d) show MCU error patterns defined in this paper: (a) horizontal, (b) vertical, (c) angle, and (d) other MCU patterns. The horizontal MCU includes upsets in a single raw occurred in a wordline (= horizontal direction). The vertical MCU includes upsets in a single column occurred in a bitline (= vertical direction). The angle MCU includes horizontal MCU and more upsets. The other MCUs are categorized in the other type shown in Fig. 12(d). Figure 13 shows the normalized MCU SER (total MCU in the conventional SRAM equals 100%). The MCU SER including horizontal upsets (horizontal and angle MCUs) is improved by 91.8–97.9% using the n-p reversed 6T cell in CKB and CS patterns because horizontal upsets easily occurs in those patterns in the conventional cell array.

#### 4. Conclusion

An n-p reversed 6T SRAM cell was proposed to improve the read stability, readout speed, and soft-error tolerance. Toward an advanced process node, a pMOS saturation current is enhanced with embedded SiGe strain technology, and a standard deviation of a pMOS threshold voltage is intrinsically smaller than that of nMOS. We leveraged the pMOS. The pMOS access and driver transistors are used in the proposed cell. Therefore, the soft-error sensitive nMOS transistors are centered on a shared p-substrate, which obviates the area overhead, extra mask, or design cost. At a 22-nm process, a static margin and cell current are improved, respectively, by factors of 2.04 and 2.81. Neutron-induced soft-error rates of the conventional proposed cells were investigated using the PHITS-based simulator. The proposed 6T cell improves the SBU and MCU soft-error rates by 11-51% and 34–70%, respectively, because the proposed n-p reversed cell has a 33% smaller nMOS diffusion than the conventional one and reduces a collected charge induced by a secondary ion. Moreover, the MCU SER, including horizontal upsets (horizontal and angle MCUs), is improved by 91.8–97.9% in CKB and CS patterns using the n-p reversed 6T cell.

#### Acknowledgments

This work was supported by Grant-in-Aid for Japan Society for the Promotion of Science (JSPS) Fellow. This work is also supported by VLSI Design and Education Center(VDEC), the University of Tokyo in collaboration with Synopsys, Inc.

#### References

[1] S.M. Jung, H. Kwon, J. Jeong, W. Cho, S. Kim, H. Lim, K. Koh, Y. Rah, J. Park, H. Kang, G. Lyu, J. Park, C. Chang, Y. Jang, D. Park, K. Kim, and M.Y. Lee, "A novel 0.79 μm<sup>2</sup> SRAM cell by KrF

Fig. 12 MCU error patterns: (a) horizontal, (b) vertical, (c) angle, and (d) other MCUs.

Fig. 13 Normalized MCU SERs at 22-nm to 130-nm process nodes.

- lithography and high performance 90 nm CMOS technology for ultra high speed SRAM," IEEE International Electron Devices Meeting (IEDM), pp.419–422, 2002.

- [2] M.E. Sinangil, H. Mair, and A.P. Chandrakasan, "A 28 nm high-density 6T SRAM with optimized peripheral-assist circuits for operation down to 0.6 V," IEEE International Solid-State Circuits Conference (ISSCC), pp.260–261, 2011.

- [3] C. Auth, A. Cappellani, J.S. Chun, A. Dalis, A. Davis, T. Ghani, G. Glass, T. Glassman, M. Harper, M. Hattendorf, P. Hentges, S. Jaloviar, S. Joshi, J. Klaus, K. Kuhn, D. Lavric, M. Lu, H. Mariappan, K. Mistry, B. Norris, N. Rahhal-orabi, P. Ranade, J. Sandford, L. Shifren, V. Souw, K. Tone, F. Tambwe, A. Thompson, D. Towner, T. Troeger, P. Vandervoorn, C. Wallace, J. Wiedemer, and C. Wiegand, "45 nm high-k + metal gate strain-enhanced transistors," IEEE Symposium on VLSI Technology, pp.128–129, 2008.

- [4] H.J. Cho, K.I. Seo, W.C. Jeong, Y.H. Kim, Y.D. Lim, W.W. Jang, J.G. Hong, S.D. Suk, M. Li, C. Ryou, H.S. Rhee, J.G. Lee, H.S. Kang, Y.S. Son, C.L. Cheng, S.H. Hong, W.S. Yang, S.W. Nam, J.H. Ahn, D.H. Lee, S. Park, M. Sadaaki, D.H. Cha, D.W. Kim, S.P. Sim, S. Hyun, C.G. Koh, B.C. Lee, S.G. Lee, M.C. Kim, Y.K. Bae, B. Yoon, S.B. Kang, J.S. Hong, S. Choi, D.K. Sohn, J.S. Yoon, and C. Chung, "Bulk planar 20 nm high-k/metal gate CMOS technology platform for low power and high performance applications," IEEE International Electron Devices Meeting (IEDM), pp.350–353, 2011.

- [5] C.C. Wu, Y.K. Leung, C.S. Chang, M.H. Tsai, H.T. Huang, D.W. Lin, Y.M. Sheu, C.H. Hsieh, W.J. Liang, L.K. Han, W.M. Chen, S.Z. Chang, S.Y. Wu, S.S. Lin, H.C. Lin, C.H. Wang, P.W. Wang, T.L. Lee, C.Y. Fu, C.W. Chang, S.C. Chen, S.M. Jang, S.L. Shue, H.T. Lin, Y.C. See, Y.J. Mii, C.H. Diaz, B.J. Lin, M.S. Liang, and Y.C. Sun, "A 90-nm CMOS device technology with high-speed,

- general-purpose, and low-leakage transistors for system on chip applications," IEEE International Electron Devices Meeting (IEDM), pp.65–68, 2002.

- [6] C. Shin, N. Damrongplasit, X. Sun, Y. Tsukamoto, B. Nikoli, and T.J.K. Liu, "Performance and yield benefits of quasi-planar bulk CMOS technology for 6-T SRAM at the 22-nm node," IEEE Trans. Electron Devices, vol.58, no.7, pp.1846–1854, 2011.

- [7] T. Tsunomura, A. Nishida, and T. Hiramoto, "Analysis of NMOS and PMOS difference in V<sub>T</sub> variation with large-scale DMA-TEG," IEEE Trans. Electron Devices, vol.56, no.9, pp.2073–2080, 2009.

- [8] A. Dixit and A. Wood, "The impact of new technology on soft error rates," IEEE International Reliability Physics Symposium (IRPS), pp.486–492, 2011.

- [9] E. Ibe, S. Chung, S. Wen, Y. Yahagi, H. Kameyama, and S. Yamamoto, "Multi-error propagation mechanisms clarified in CMOSFET SRAM devices under quasi-mono energetic neutron irradiation," IEEE Nuclear and Space Radiation Effects Conference (NSREC), no.PC-6, 2006.

- [10] N. Seifert and V. Zia, "Assessing the impact of scaling on the efficacy of spatial redundancy based mitigation schemes for terrestrial applications," IEEE Silicon Errors in Logic — System Effects (SELSE), pp.1–6, 2007.

- [11] J. Maiz, S. Hareland, K. Zhang, and P. Armstrong, "Characterization of multi-bit soft error events in advanced SRAMs," IEEE International Electron Devices Meeting (IEDM), pp.519–522, 2003.

- [12] G. Gasiot, D. Giot, and P. Roche, "Alpha-induced multiple cell upsets in standard and radiation hardened SRAMs manufactured in a 65 nm CMOS technology," IEEE Trans. Nucl. Sci., vol.53, no.6, pp.3479–3486, 2006.

- [13] S. Yoshimoto, T. Amashita, S. Okumura, K. Nii, H. Kawaguchi, and

- M. Yoshimoto, "NMOS-inside 6T SRAM layout reducing neutron-induced multiple cell upsets," IEEE International Reliability Physics Symposium (IRPS), pp.5B.5.1–5, April 2012.

- [14] H. Iwase, K. Nitta, and T. Nakamura, "Development of general-purpose particle and heavy ion transport monte carlo code," IEEE Trans. Nucl. Sci., vol.39, pp.1142–1151, 2002. http://phits.jaea.go.jp/

- [15] International Technology Roadmap for Semiconductors (ITRS), 2001–2011. http://www.itrs.net/

- [16] P.A. Stolk, F.P. Widdershoven, and D.B.M. Klaassen, "Modeling statistical dopant fluctuations in MOS transistors," IEEE Trans. Electron Devices, vol.45, no.9, pp.1960–1971, 1998.

- [17] H. Kobayashi, N. Kawamoto, J. Kase, and K. Shiraishi, "Alpha particle and neutron-induced soft error rates and scaling trends in SRAM," IEEE International Reliability Physics Symposium (IRPS), pp.206–211, 2009.

- [18] B.D. Sierawski, R.A. Reed, M.H. Mendenhall, R.A. Weller, R.D. Schrimpf, S.J. Wen, R. Wong, N. Tam, and R.C. Baumann, "Effects of scaling on muon-induced soft errors," IEEE International Reliability Physics Symposium (IRPS), pp.247–252, 2011.

- [19] T. Douseki and S.I. Mutoh, "Static-noise margin analysis for a scaled-down CMOS memory cell," IEICE Trans. Electron, vol.J75– C–II, no.7, pp.350–361, July 1992.

- [20] S. Yoshimoto, T. Amashita, M. Yoshimura, Y. Matsunaga, H. Yasuura, S. Izumi, H. Kawaguchi, and M. Yoshimoto, "Neutron-induced soft error rate estimation for SRAM using PHITS," IEEE International On-Line Testing Symposium (IOLTS), pp.173–176, 2012.

- [21] T. Sato, H. Yasuda, K. Niita, A. Endo, and L. Sihverd, "Development of PARMA: PHITS-based analytical radiation model in the atmosphere," Radiat. Res., vol.170, pp.244–259, 2008; EXPACS ver. 2.21, 2011. http://phits.jaea.go.jp/expacs/index.html

- [22] H.W. Bertini, Oak Ridge National Laboratory, ORNL-3383, 1963.

- [23] S. Furihata, "Statistical analysis of light fragment production from medium energy proton-induced reactions," Nucl. Instr. and Meth. in Phys. Res. B, vol.171, pp.251–258, 2000.

- [24] K. Shibata, O. Iwamoto, T. Nakagawa, N. Iwamoto, A. Ichihara, S. Kunieda, S. Chiba, K. Furutaka, N. Otuka, T. Ohsawa, T. Murata, H. Matsunobu, A. Zukeran, S. Kamada, and J. Katakura, "JENDL-4.0: A new library for nuclear science and engineering," J. Nucl. Sci. Technol., vol.48, no.1, pp.1–30, 2011.

Shusuke Yoshimoto received B.E. and M.E. degrees in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2009 and 2011, respectively. He earned Ph.D. degree in Engineering from the university in 2013. He moved to Department of Electrical Engineering, Stanford University, as a Postdoc in 2013. His current research interests include testing, verification, nanoelectronics, soft error, low-power and robust memory design. He was a recipient of 2011 and 2012 IEEE SSCS Japan Chapter

Academic Research Awards, 2013 IEEE SSCS Kansai Chapter IMFEDK Student Paper Award, and 2013 Intel/Analog Devices/Catalyst Foundation/Cirrus Logic CICC Student Scholarship Award. He is a member of IEICE, IPSJ and IEEE. He was a representative for student members in VDEC Designer's Forum Ph.D. session 2012 and 2013. He is working on a member of ICD student TPC in 2012–2013. He is a Research Fellow of the Japan Society for the Promotion of Science from 2013 to 2014.

Hiroshi Kawaguchi received his B.E. and M.E. degrees in Electronic Engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and earned a Ph.D. degree in Engineering from The University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corporation, Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to the Institute of Industrial Science, The University of Tokyo, as a Technical Associate in 1996, and was appointed as a Research Asso-

ciate in 2003. In 2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with the Department of Information Science at that university. He is also a Collaborative Researcher with the Institute of Industrial Science, The University of Tokyo. His current research interests include low-voltage SRAM, RF circuits, and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for IEEE Signal Processing Society, as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips), and as a Guest Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of IEEE, ACM, IPSJ, and IEICE.

Masahiko Yoshimoto earned his B.S. degree in Electronic Engineering from Nagoya Institute of Technology, Nagoya, Japan, in 1975, and an M.S. degree in Electronic Engineering from Nagoya University, Nagoya, Japan, in 1977. He earned a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan in 1998. He joined the LSI Laboratory, Mitsubishi Electric Corporation, Itami, Japan, in April 1977. During 1978–1983 he was engaged in the design of NMOS and CMOS static RAM

including a 64 K full CMOS RAM with the world's first divided-wordline structure. From 1984, he was involved in research and development of multimedia ULSI systems for digital broadcasting and digital communication systems based on MPEG2 and MPEG4 Codec LSI core technology. Since 2000, he has been a Professor of the Department of Electrical and Electronic Systems Engineering at Kanazawa University, Japan. Since 2004, he has been a Professor of the Department of Computer and Systems Engineering at Kobe University, Japan. His current activities are research and development of multimedia and ubiquitous media VLSI systems including an ultra-low-power image compression processor and a low-power wireless interface circuit. He holds 70 registered patents. He served on the Program Committee of the IEEE International Solid State Circuit Conference during 1991-1993. Additionally, he served as a Guest Editor for special issues on Low-Power System LSI, IP, and Related Technologies of IEICE Transactions in 2004. He received R&D100 awards in 1990 and 1996 from R&D Magazine for development of the DISP and development of a real-time MPEG2 video encoder chipset, respectively.