Abstract

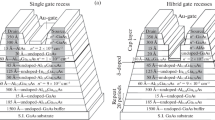

A two-step gate-recess process combining high selective wet-etching and non-selective digital wet-etching techniques has been proposed for InAlAs/InGaAs InP-based high electron mobility transistors (HEMTs). High etching-selectivity ratio of InGaAs to InAlAs material larger than 100 is achieved by using mixture solution of succinic acid and hydrogen peroxide (H2O2). Selective wet-etching is validated in the gate-recess process of InAlAs/InGaAs InP-based HEMTs, which proceeds and automatically stops at the InAlAs barrier layer. The non-selective digital wet-etching process is developed using a separately controlled oxidation/de-oxidation technique, and during each digital etching cycle 1.2 nm InAlAs material is removed. The two-step gate-recess etching technique has been successfully incorporated into device fabrication. Digital wet-etching is repeated for two cycles with about 3 nm InAlAs barrier layer being etched off. InP-based HEMTs have demonstrated superior extrinsic transconductance and RF characteristics to devices fabricated during only the selective gate-recess etching process because of the smaller gate to channel distance.

Similar content being viewed by others

References

Cao, X., Thoms, S., Macintyre, D., et al., 2004. Fabrication and performance of 50 nm T-gates for InP high electron mobility transistors. Microelectron. Eng., 73–74: 818–821. https://doi.org/10.1016/j.mee.2004.03.058

Deal, W.R., Mei, X.B., Leong, K., et al., 2011a. THz monolithic integrated circuits using InP high electron mobility transistors. IEEE Trans. Terah. Sci. Technol., 1(1): 25–32. https://doi.org/10.1109/TTHZ.2011.2159539

Deal, W.R., Leong, K., Radisic, V., et al., 2011b. Low noise amplification at 0.67 THz using 30 nm InP HEMTs. IEEE Microw. Wirel. Compon. Lett., 21(7): 368–370. https://doi.org/10.1109/LMWC.2011.2143701

Deal, W.R., Leong, K., Zamora, A., et al., 2014. Recent progress in scaling InP HEMT TMIC technology to 850 GHz. IEEE MTT-S Int. Microwave Symp., p.1–3. https://doi.org/10.1109/MWSYM.2014.6848588

Leong, K., Mei, X.B., Yoshida, W., et al., 2015. A 0.85 THz low noise amplifier using InP HEMT transistors. IEEE Microw. Wirel. Compon. Lett., 25(6): 397–399. https://doi.org/10.1109/LMWC.2015.2421336

Mei, X.B., Yoshida, W., Lange, M., et al., 2015. First demonstration of amplification at 1 THz using 25-nm InP high electron mobility transistor process. IEEE Electr. Dev. Lett., 36(4): 327–329. https://doi.org/10.1109/LED.2015.2407193

Reck, T., Zemora, A., Schlecht, E., et al., 2016. A 230 GHz MMIC-based sideband separating receiver. IEEE Trans. Terah. Sci. Technol., 6(1): 141–147. https://doi.org/10.1109/TTHZ.2015.2506552

Rodwell, M.J.W., 2014. 50-500 GHz wireless: transistors, ICs, and system design. German Microwave Conf., p.1–4.

Varonen, M., Reeves, R., Kangaslahti, P., et al., 2016. An MMIC low-noise amplifier design technique. IEEE Trans. Microw. Theory Techn., 64(3): 826–835. https://doi.org/10.1109/TMTT.2016.2521650

Zhong, Y.H., Wang, X.T., Su, Y.B., et al., 2012a. Impact of the lateral width of the gate recess on the DC and RF characteristics of InAlAs/InGaAs HEMTs. J. Semicond., 33(5): 61–65. https://doi.org/10.1088/1674-4926/33/5/054007

Zhong, Y.H., Wang, X.T., Su, Y.B., et al., 2012b. An 88 nm gate-length In0.53Ga0.47As/In0.52Al0.48As InP-based HEMT with f max of 201 GHz. J. Semicond., 33(7): 39–42. https://doi.org/10.1088/1674-4926/33/7/074004

Zhong, Y.H., Li, K.K., Li, X.J., et al., 2015. A W-band high-gain and low-noise amplifier MMIC using InP-based HEMTs. J Infrar. Millim. Waves, 34(6): 668–672 (in Chinese). https://doi.org/10.11972/j.issn.1001-9014.2015.06.006

Acknowledgements

The authors would like to express heartfelt thanks to Yan-kui LI for tuning the measurement equipment and are very grateful for all the members in the Compound Semiconductor Device Department, Institute of Microelectronics, Chinese Academy of Sciences.

Author information

Authors and Affiliations

Corresponding author

Additional information

Project supported by the National Natural Science Foundation of China (Nos. 61404115 and 61434006), the Program for Innovative Research Team (in Science and Technology) in University of Henan Province, China (No. 18IRTSTHN016), and the Development Fund for Outstanding Young Teachers in Zhengzhou University, China (No. 1521317004)

Rights and permissions

About this article

Cite this article

Zhong, Yh., Sun, Sx., Wong, Wb. et al. Two-step gate-recess process combining selective wet-etching and digital wet-etching for InAlAs/InGaAs InP-based HEMTs. Frontiers Inf Technol Electronic Eng 18, 1180–1185 (2017). https://doi.org/10.1631/FITEE.1601121

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/FITEE.1601121