Abstract

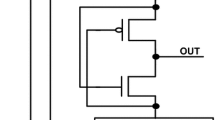

We propose a modeling methodology for both leakage power consumption and delay of basic CMOS digital gates in the presence of threshold voltage and mobility variations. The key parameters in determining the leakage and delay are OFF and ON currents, respectively, which are both affected by the variation of the threshold voltage. Additionally, the current is a strong function of mobility. The proposed methodology relies on a proper modeling of the threshold voltage and mobility variations, which may be induced by any source. Using this model, in the plane of threshold voltage and mobility, we determine regions for different combinations of performance (speed) and leakage. Based on these regions, we discuss the trade-off between leakage and delay where the leakage-delay-product is the optimization objective. To assess the accuracy of the proposed model, we compare its predictions with those of HSPICE simulations for both basic digital gates and ISCAS85 benchmark circuits in 45-, 65-, and 90-nm technologies.

Similar content being viewed by others

References

Agarwal, A., Dartu, F., Blaauw, D., 2004. Statistical Gate Delay Model Considering Multiple Input Switching. Proc. 41st Annual Design Automation Conf., p.658–663. [doi:10.1145/996566.996746]

Alpert, C.J., Devgan, A., Kashyap, C.V., 2001. RC delay metrics for performance optimization. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst., 20(5):571–582. [doi:10. 1109/43.920682]

Andrieu, F., Ernst, T., Lime, F., Rochette, F., Romanjek, K., Barraud, S., Ravit, C., Boeuf, F., Jurczak, M., Casse, M., et al., 2005. Experimental and Comparative Investigation of Low and High Field Transport in Substrate- and Process-Induced Strained Nanoscale MOSFETs. Symp. on VLSI Technology, Digest of Technical Papers, p.176–177. [doi:10.1109/.2005.1469257]

Arizona State University, 2006. Predictive Technology Models. Available from http://ptm.asu.edu/ [Accessed on Sept. 13, 2011].

Chen, H., Neely, S., Xiong, J., Zolotov, V., Visweswariah, C., 2008. Statistical modeling and analysis of static leakage and dynamic switching power. LNCS, 5349:178–187. [doi:10.1007/978-3-540-95948-9_18]

Chen, M., Yi, Y., Zhao, W., Ma, D., 2011. Variation-Aware Deep Nanometer Gate Performance Modeling: an Analytical Approach. Int. Symp. on VLSI Design, Automation, and Test, p.1–4. [doi:10.1109/VDAT.2011.5783560]

Cheng, L., Gupta, P., He, L., 2009. Efficient additive statistical leakage estimation. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst., 28(11):1777–1781. [doi:10.1109/TCAD. 2009.2030433]

Christian, S., 2007. Leakage Aware Digital Design Optimization for Minimal Total Power Consumption in Nanometer CMOS Technologies. PhD Thesis, University of Neuchâtel, Switzerland.

D’Agostino, C., le Coz, J., Flatresse, P., Beigne, E., Belleville, M., 2009. An Accurate Approach for Statistical Estimation of Leakage Current Considering Multi-parameter Process Variations in Nanometer CMOS Technologies. Proc. European Solid State Device Research Conf., p.427–430. [doi:10.1109/ESSDERC.2009.5331488]

da Silva, D.N., Reis, A.I., Ribas, R.P., 2009. CMOS logic gate performance variability related to transistor network arrangements. Microelectron. Reliab., 49(9–11):977–981. [doi:10.1016/j.microrel.2009.07.023]

Guerra, L., Phillips, J., Silveira, L.M., 2010. Effective corner-based techniques for variation-aware IC delay verification. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst., 29(1):157–162. [doi:10.1109/TCAD.2009.2034343]

Gupta, P., Jeong, K., Kahng, A.B., Park, C., 2008. Electrical metrics for lithographic line-end tapering. SPIE, 7028(2):70283A.1–70283A.12. [doi:10.1117/12.793117]

Hao, Z., Tan, S., Shi, G., 2011. An Efficient Statistical Chip-Level Total Power Estimation Method Considering Process Variations with Spatial Correlation. Int. Symp. on Quality Electronic Design, p.1–6. [doi:10.1109/ISQED. 2011.5770801]

Joshi, V., Agarwal, K., Sylvester, D., 2010. Simultaneous Extraction of Effective Gate Length and Low-Field Mobility in Non-uniform Devices. Int. Symp. on Quality Electronic Design, p.158–162. [doi:10.1109/ISQED.2010. 5450409]

Liu, Q., Sapatnekar, S., 2009. A framework for scalable postsilicon statistical delay prediction under process variations. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst., 28(8):1201–1212. [doi:10.1109/TCAD.2009.2021732]

Liu, Q., Sapatnekar, S., 2010. Capturing post-silicon variations using a representative critical path. IEEE Trans. Comput.-Aided Des. Integr. Circ. Syst., 29(2):211–222. [doi:10. 1109/TCAD.2009.2035552]

Ma, T., 2009. Improving Design Quality by Managing Process Variability. Int. Symp. on Quality Electronic Design (Presentation), p.18–23.

Miryala, S., Kaur, B., Anand, B., Manhas, S., 2011. Efficient Nanoscale VLSI Standard Cell Library Characterization Using a Novel Delay Model. Int. Symp. on Quality Electronic Design, p.1–6. [doi:10.1109/ISQED.2011.5770 767]

Mistry, K., Armstrong, M., Auth, C., Cea, S., Coan, T., Ghani, T., Hoffmann, T., Murthy, A., Sandford, J., Shaheed, R., et al., 2004. Delaying Forever: Uniaxial Strained Silicon Transistors in a 90nm CMOS Technology. Symp. on VLSI Technology, Digest of Technical Papers, p.50–51. [doi:10.1109/VLSIT.2004.1345387]

Morshed, T.H., 2009. BSIM4.6.4 MOSFET Model. User’s Manual. Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA.

Narendra, S., Blaauw, D., Devgan, A., Najm, F., 2003. Leakage Issues in IC Design: Trends, Estimation and Avoidance. Int. Conf. on Computer Aided Design (tutorial), p.11. [doi:10.1109/ICCAD.2003.145]

Okada, K., Yamaoka, K., Onodera, H., 2003. A Statistical Gate-Delay Model Considering Intra-Gate Variability. Int. Conf. on Computer Aided Design, p.908–913. [doi:10. 1109/ICCAD.2003.20]

Orshansky, M., Nassif, S.R., Boning, D., 2008. Design for Manufacturability and Statistical Design: a Constructive Approach. Springer, New York, NY.

Pramanik, D., Moroz, V., Lin, X.W., 2006. Process Induced Layout Variability for sub 90nm Technologies. Int. Conf. on Circuit Technology, p.1849–1852. [doi:10.1109/ICSICT. 2006.306464]

Ramalingam, A., Kodakara, S.V., Devgan, A., Pan, D., 2006. Robust Analytical Gate Delay Modeling for Low Voltage Circuits. Asia and South Pacific Design Automation Conf., p.61–66. [doi:10.1145/1118299.1118315]

Rao, R., Srivastava, A., Blaauw, D., Sylvester, D., 2004. Statistical analysis of subthreshold leakage current for VLSI circuits. IEEE Trans. VLSI Syst., 12(2):131–139. [doi:10. 1109/TVLSI.2003.821549]

Roy, S., Asenov, A., 2005. Where do the dopants go? Science, 309(5733):388–390. [doi:10.1126/science.1111104]

Sakurai, T., Newton, A.R., 1990. Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas. IEEE J. Sol.-State Circ., 25(2):584–594. [doi:10.1109/4.52187]

Scott, G., Lutze, J., Rubin, M., Nouri, F., Manley, M., 1999. NMOS Drive Current Reduction Caused by Transistor Layout and Trench Isolation Induced Stress. Int. Electron Device Meeting, p.827–830. [doi:10.1109/IEDM.1999.824277]

Singhal, R., Balijepalli, A., Subramaniam, A., Liu, F., Nassif, S., Cao, Y., 2007. Modeling and Analysis of Non-rectangular Gate for Post-Lithography Circuit Simulation. Proc. 44th Annual Design Automation Conf., p.823–828. [doi:10.1145/1278480.1278685]

Srivastava, A., Sylvester, D., Blaauw, D., 2005. Statistical Analysis and Optimization for VLSI: Delay and Power. Springer, New York, NY. Synopsys Corporation, 2008.

Synopsys HSPICE. Available from http://www.synopsys.com/Tools/Verification/AMSVerification/CircuitSimulation/HSPICE/Pages/default.aspx [Accessed on Sept. 13, 2011].

Sze, S.M., Ng, K.K., 2007. Physics of Semiconductor Devices. John Wiley & Sons, Hoboken, NJ.

Tsai, K.Y., You, M.F., Lu, Y.C., Ng, P.C.W., 2008. A New Method to Improve Accuracy of Leakage Current Estimation for Transistors with Non-rectangular Gates due to Sub-wavelength Lithography Effects. Int. Conf. on Computer-Aided Design, p.286–291. [doi:10.1109/ICCAD. 2008.4681587]

Xu, N., Wang, L., Neureuther, A., Liu, T., 2011. Physically based modeling of stress-induced variation in nanoscale transistor performance. IEEE Trans. Dev. Mater. Reliab., 11(3):378–386. [doi:10.1109/TDMR.2011.2144598]

Ye, Z., Yu, Z., 2009. An Efficient Algorithm for Modeling Spatially-Correlated Process Variation in Statistical Full-Chip Leakage Analysis. Proc. Int. Conf. on Computer-Aided Design, p.295–301. [doi:10.1145/1687399.1687455]

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Aghababa, H., Forouzandeh, B. & Afzali-Kusha, A. High-performance low-leakage regions of nano-scaled CMOS digital gates under variations of threshold voltage and mobility. J. Zhejiang Univ. - Sci. C 13, 460–471 (2012). https://doi.org/10.1631/jzus.C1100273

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1631/jzus.C1100273