### Analytical Exploration and Quantification of Nanowire-based Reconfigurable Digital Circuits

THESIS

to obtain the academic degree Doktoringenieur (Dr.-Ing.)

at the Faculty of Computer Science of the Technical University of Dresden submitted

by Michael Raitza born on the 23 October 1983 in Rostock, Germany

Promoter:

Prof. Dr. Akash Kumar Technical University of Dresden

Prof. Dr.-Ing. Thomas Mikolajick Technical University of Dresden

Date of defense:

20 October 2022

# Analytical Exploration and Quantification of Nanowire-based Reconfigurable Digital Circuits

Michael Raitza

### Abstract

Integrated circuit development is an industry-driven high-risk high-stakes environment. The time from the concept of a new transistor technology to the marketready product is measured in decades rather than months or years. This increases the risk for any company endeavouring on the journey of driving a new concept. Additionally to the return on investment being in the far future, it is only to be expected at all in high volume production, increasing the upfront investment. What makes the undertaking worthwhile are the exceptional gains that are to be expected, when the production reaches the market and enables better products. For these reasons, the adoption of new transistor technologies is usually based on small increments with foreseeable impact on the production process. Emerging semiconductor device development must be able to prove its value to its customers, the chip-producing industry, the earlier the better. With this thesis, I provide a new approach for early evaluation of emerging reconfigurable transistors in reconfigurable digital circuits. Reconfigurable transistors are a type of metal-oxide semiconductor field-effect transistor (MOSFET) that features a controllable conduction polarity, i. e. they can be configured by other input signals to work as PMOS or NMOS devices.

Early device and circuit characterisation poses some challenges that are currently largely neglected by the development community. Firstly, to drive transistor development into the right direction, early feedback is necessary, which requires a method that can provide quantitative and qualitative results over a variety of circuit designs and must run mostly automatic. It should also require as little expert knowledge as possible to enable early experimentation on the device and new circuit designs together. Secondly, to actually *run* early, its device model should need as little data as possible to provide meaningful results. The proposed approach of this thesis tackles both challenges and employs model checking, a formal method, to provide a framework for the automated quantitative and qualitative analysis. It pairs a simple transistor device model with a charge transport model of the electrical network.

In this thesis, I establish the notion of transistor-level reconfiguration and show the kinds of reconfigurable standard cell designs the device facilitates. Early investigation resulted in the discovery of certain modes of reconfiguration that the transistor features and their application to design reconfigurable standard cells. Experiments with device parameters and the design of improved combinational circuits that integrate new reconfigurable standard cells further highlight the need for a thorough investigation and quantification of the new devices and newly available standard cells. As their performance improvements are inconclusive when compared to established CMOS technology, a design space exploration of the possible reconfigurable standard cell variants and a context-aware quantitative analysis turns out to be required.

I show that a charge transport model of the analogue transistor circuit provides the necessary abstraction, precision and compatibility with an automated analysis. Formalised in a domain-specific language (DSL), it enables designers to freely characterise and combine parametrised transistor models, circuit descriptions that are device independent, and re-usable experiment setups that enable the analysis of large families of circuit variants. The language is paired with a design space exploration algorithm that explores all implementation variants of a Boolean function that employs various degrees and modes of reconfiguration. The precision of the device models and circuit performance calculations is validated against state-of-the-art finite element method (FEM) and SPICE simulations of production transistors.

Lastly, I show that the exploration and analysis can be done efficiently using two important Boolean functions. The analysis ranges from worst-case measures, like delay, power dissipation and energy consumption to the detection and quantification of output hazards and the verification of the functionality of a circuit implementation. It ends in presenting average performance results that depend on the statistical characterisation of application scenarios. This makes the approach particularly interesting for measures like energy consumption, where average results are more interesting, and for asynchronous circuit designs which highly depend on average delay performance. I perform the quantitative analysis under various input and output load conditions in over 900 fully automated experiments. It shows that the complexity of the results warrants an extension to electronic design automation flows to fully exploit the capabilities of reconfigurable standard cells. The high degree of automation enables a researcher to use as little as a Boolean function of interest, a transistor model and a set of experiment conditions and queries to perform a wide range quantitative analyses and acquire early results.

## Acknowledgements

This thesis has multiple fathers. I want to express my deepest thanks and respect to Hermann Härtig, who took me into his chair when my early aspirations to get promoted almost came to a complete halt after the departure of my first academic mentor Christian Hochberger to a more fruitful place to do research. Hermann and his colleague Marcus Völp, who became my first supervisor of this thesis, took it upon themselves to integrate a computer engineering researcher into the community of systems architecture research. To their effort and endurance with my very different approach to the research topic I owe the opportunity to write this thesis.

After it became apparent that I would remain a computer engineer, Hermann found a new academic home for me in the newly established Processor Design Chair of Akash Kumar, to continue my research under his guidance. With Akash as my doctoral supervisor, my thesis found its final direction. To him I also want to express my deepest thanks and my respect for his leadership.

This thesis is also the product of a willingness and openness to do interdisciplinary research that was facilitated by the Center for Advancing Electronics Dresden (cfaed). I especially would like to thank Thomas Mikolajick and Walter Weber from the semiconductor research community for their financial and scientific support. The cfaed brought me together with Jens Trommer, also from semiconductor research, to whom I owe my gratitude and most of my understanding (and all my FEM simulation data) of reconfigurable transistors. It also set me up with Steffen Märcker from the theoretical computer science community, which spun off a fruitful and intense collaboration that found its expression in the use of model checking in this thesis.

My biggest thanks go to my family who always support me and provide the protected room for development and thought. Dear Uwe, Barbara, dear Thomas, thank you for having you. Last but most importantly, I want to thank my wife Sara, the love of my life, for her love, active support and endurance with a scientist's odd work schedule. You provide the soil on which my creativity can grow its products.

## Contents

| 1 | Inti                                | oduction                                                                                                 | 1                                       |  |  |  |  |  |  |  |  |

|---|-------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|--|

|   | 1.1                                 | Emerging Reconfigurable Transistor Technology                                                            |                                         |  |  |  |  |  |  |  |  |

|   | 1.2                                 | Testing and Standard Cell Characterisation                                                               |                                         |  |  |  |  |  |  |  |  |

|   | 1.3                                 | Research Questions                                                                                       | 6                                       |  |  |  |  |  |  |  |  |

|   | 1.4                                 | Design Space Exploration and Quantitative Analysis                                                       | 7                                       |  |  |  |  |  |  |  |  |

|   | 1.5                                 | Contribution                                                                                             | 9                                       |  |  |  |  |  |  |  |  |

| 2 | Fundamental Reconfigurable Circuits |                                                                                                          |                                         |  |  |  |  |  |  |  |  |

|   | 2.1                                 | Reconfiguration Redefined                                                                                | <b>13</b><br>14                         |  |  |  |  |  |  |  |  |

|   |                                     | 2.1.1 Common Understanding of Reconfiguration                                                            | 14                                      |  |  |  |  |  |  |  |  |

|   |                                     | 2.1.2 Reconfiguration is Computation                                                                     | 18                                      |  |  |  |  |  |  |  |  |

|   | 2.2                                 | Reconfigurable Transistor                                                                                | 20                                      |  |  |  |  |  |  |  |  |

|   |                                     | 2.2.1 Device geometry                                                                                    | 20                                      |  |  |  |  |  |  |  |  |

|   |                                     | 2.2.2 Electrical properties                                                                              | 23                                      |  |  |  |  |  |  |  |  |

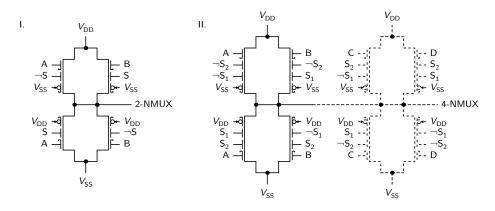

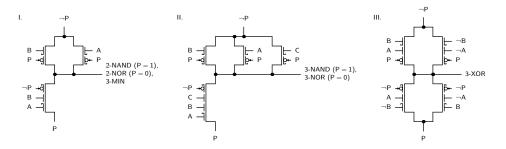

|   | 2.3                                 | Fundamental Circuits                                                                                     | $^{-3}_{28}$                            |  |  |  |  |  |  |  |  |

| 3 | Cor<br>3.1                          | nbinational Circuits and Higher-Order Functions         Programmable Logic Cells         Order Functions | <b>35</b><br>35                         |  |  |  |  |  |  |  |  |

|   |                                     | 3.1.1 Critical Path Delay Estimation using Logical Effort Method                                         | 36                                      |  |  |  |  |  |  |  |  |

|   |                                     | 3.1.2 Multi-Functional Circuits                                                                          | 40                                      |  |  |  |  |  |  |  |  |

|   | 3.2                                 | Improved Conditional Carry Adder                                                                         | 45                                      |  |  |  |  |  |  |  |  |

| 4 | Cor                                 | structive DSE for Standard Cells Using MC                                                                | 51                                      |  |  |  |  |  |  |  |  |

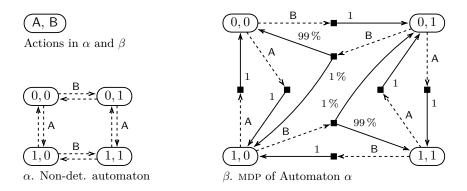

|   | 4.1                                 | Principle Operation of Model Checking                                                                    | 54                                      |  |  |  |  |  |  |  |  |

|   |                                     | 4.1.1 Model Types                                                                                        | 55                                      |  |  |  |  |  |  |  |  |

|   |                                     |                                                                                                          | ~                                       |  |  |  |  |  |  |  |  |

|   |                                     | 4.1.2 Query Types                                                                                        | 58                                      |  |  |  |  |  |  |  |  |

|   | 4.2                                 | 4.1.2 Query Types                                                                                        | $\frac{58}{59}$                         |  |  |  |  |  |  |  |  |

|   | 4.2                                 | Overview and Workflow                                                                                    |                                         |  |  |  |  |  |  |  |  |

|   | 4.2                                 | Overview and Workflow4.2.1Experiment setup4.2.2Quantitative Analysis and Results                         | 59                                      |  |  |  |  |  |  |  |  |

|   | 4.2<br>4.3                          | Overview and Workflow                                                                                    | $\begin{array}{c} 59 \\ 60 \end{array}$ |  |  |  |  |  |  |  |  |

|   | -                                   | Overview and Workflow4.2.1Experiment setup4.2.2Quantitative Analysis and Results                         | 59<br>60<br>64                          |  |  |  |  |  |  |  |  |

|                       |                                         | 4.3.3Transistor Model74.3.4Queries for Quantitative Analysis8 | 77<br>88 |  |  |  |  |  |  |  |  |  |

|-----------------------|-----------------------------------------|---------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|--|

|                       | $4 \cdot 4$                             | Circuit Variant Generation                                    | )1       |  |  |  |  |  |  |  |  |  |

|                       |                                         | 4.4.1 Function Expansion                                      | )2       |  |  |  |  |  |  |  |  |  |

| <b>5</b>              | Quantitative Analysis of Standard Cells |                                                               |          |  |  |  |  |  |  |  |  |  |

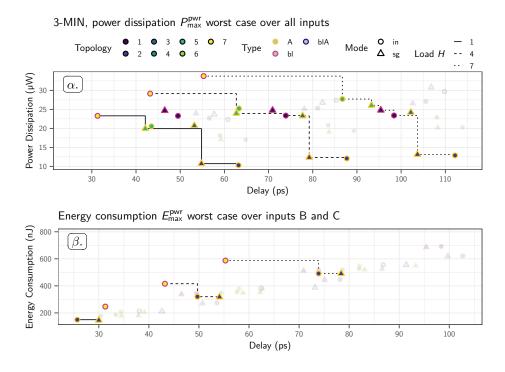

|                       | 5.1                                     | Analysis of 3-Input Minority Logic Gate                       |          |  |  |  |  |  |  |  |  |  |

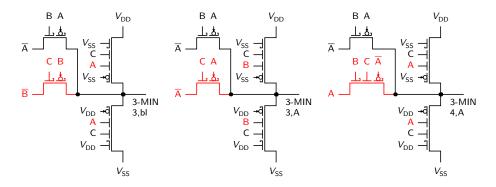

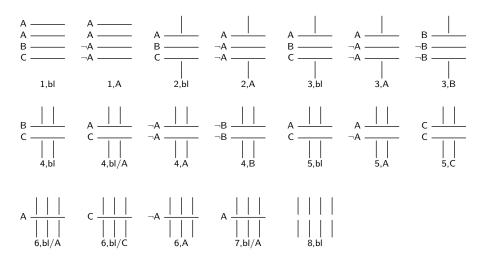

|                       |                                         | 5.1.1 Circuit Variants                                        |          |  |  |  |  |  |  |  |  |  |

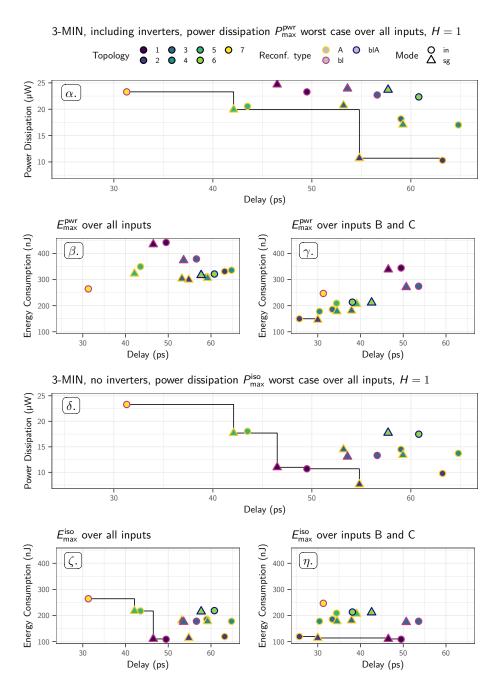

|                       |                                         | 5.1.2 Worst-Case Analysis                                     | 0        |  |  |  |  |  |  |  |  |  |

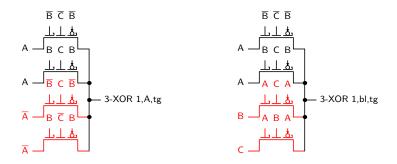

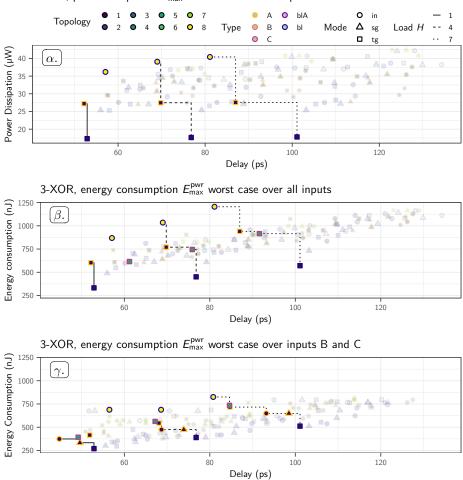

|                       | 5.2                                     | Analysis of 3-Input Exclusive OR Gate                         |          |  |  |  |  |  |  |  |  |  |

|                       |                                         | 5.2.1 Worst-Case Analysis                                     |          |  |  |  |  |  |  |  |  |  |

|                       |                                         | 5.2.2 Functional Verification                                 |          |  |  |  |  |  |  |  |  |  |

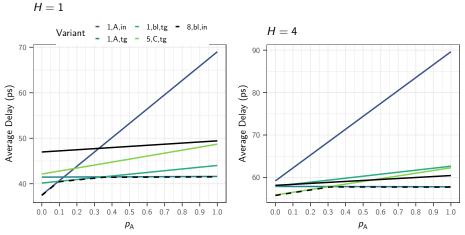

|                       |                                         | 5.2.3 Probabilistic Analysis                                  | 0        |  |  |  |  |  |  |  |  |  |

| 6                     | Conclusion and Future Work              |                                                               |          |  |  |  |  |  |  |  |  |  |

|                       | 6.1                                     | Future Work                                                   | 27       |  |  |  |  |  |  |  |  |  |

| Α                     | Not                                     | ational conventions 12                                        | 9        |  |  |  |  |  |  |  |  |  |

| в                     | pris                                    | m-gen Programming Interfaces 13                               | ;1       |  |  |  |  |  |  |  |  |  |

| Bibliography          |                                         |                                                               |          |  |  |  |  |  |  |  |  |  |

| Terms & Abbreviations |                                         |                                                               |          |  |  |  |  |  |  |  |  |  |

# Chapter 1 Introduction

The semiconductor industry is known to be a high-risk high-stakes environment. New production lines take a tremendous amount of money, time and effort to be established and to start returning their investment. The time scale is measured in decades rather than years or months, as the device that is used in this work a germanium nanowire reconfigurable Schottky junction field effect transistor with multiple independent control gates was first shown in 2006 in [62] and is yet to be picked up for production. As a consequence, production alterations are implemented with great caution and very conservatively, favouring small-step evolution over revolutionary technological jumps. Emerging devices must prove their worth before they can expect to be accepted by the industry.

This is where the current device and circuit characterisation techniques are not sufficient. Current methods expect a technology readiness level of 4-5 ([55]), which is about to be reached now for the mentioned germanium nanowire technology, before significant device models can be constructed, namely SPICE compact models. These models are needed in order to perform sufficiently precise logic circuit performance projections that garner interest of the producing industry or steer further device optimisation. Additionally, producing smaller device structures proves harder to yield enough functioning chips. Thus, the old rule that complexity and reliability are at odds with each other still holds true for chip manufacturing. So, either increasing the functionality per transistor and per standard cell or reducing the size and complexity of a fixed standard cell are still beneficial design goals for emerging technologies. This is what polaritycontrollable transistors and reconfigurable circuits are promising candidates for. A design space exploration and quantitative analysis method that works from an earlier technology readiness level would be a valuable contribution to these demands, especially if it focuses on high automation and a decent coverage of the possible circuit implementation variants.

Formal methods, like model checking and theorem proving, provide valuable properties that align especially well with the demands in hardware development, surveyed in [17] and exemplified in [19]. Both disciplines usually require exact and exhaustive answers to critical questions, which sets them apart from the best-effort computing domain. Both also struggle with the inevitable state space explosion problem which leads hardware development to accept suboptimal circuit design results in exchange for functional correctness guarantees. It also has led to the general acceptance of simulation methods in projecting and validating circuit performance characteristics. In this thesis, I present a design space exploration and quantitative analysis approach that is tailored to probabilistic model checking, a formal method and suitable to investigate logic gates of the size of standard cells. It builds on the model checker PRISM and provides its own input language that is tailored to describe transistors, standard cells and experiment setups to characterise them. Model checking [3] provides the formal framework to exactly model and compute the analogue transistor network and also provides the query language(s), based on temporal logics such as computation tree logic (CTL) and linear time logic (LTL), to ask for interesting quantitative and qualitative circuit properties. It enables the direct computation of extremal values without the need for particular knowledge about the circuit under test. So, instead of needing expert knowledge to provide the right set of simulation input stimuli, the model checker can be directly asked for the worst-case delay or power dissipation for an arbitrary logic gate. After delivering the output, model checking also provides the state transitions as witnesses that allow a close inspection of the circuit behaviour in interesting situations after the fact. What is very valuable, though, for future integration, is that probabilistic model checking is able to determine the long-run average performance characteristics of a circuit. Obviously, the average performance is what is exhibited most of the time by a circuit and, thus, is where optimisations lead to the highest benefits. Especially for measures like energy consumption, that can easily tolerate short but large deviations, optimising for the average may be much more beneficial than optimising for the worst-case. Results, such as the long-run average, can also be computed as rational functions in variables that abstract model characteristics as probabilities, such as the switching frequency of an input.

#### 1.1 Emerging Reconfigurable Transistor Technology

The analysis method that I am going to lay out in this thesis has been conceived to solve the problem of early device characterisation especially for reconfigurable transistor technology that itself is founded in the ambipolar behaviour of each device. Ambipolarity describes the property of a semiconductor to conduct both charge carriers, electrons  $(e^-)$  and holes  $(h^+)$ . This is usually a property that designers seek to avoid, because it leads to undesirable short-circuit currents in digital circuits that increase the energy consumption or conflict with the circuit function altogether. In reconfigurable transistors, engineers have found ways to control the ambipolar device behaviour electrostatically as shown in Figure 1.1.

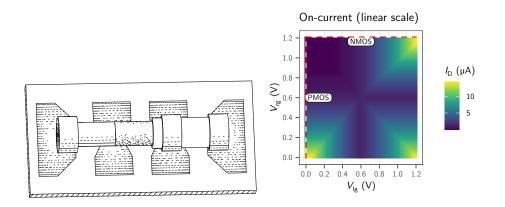

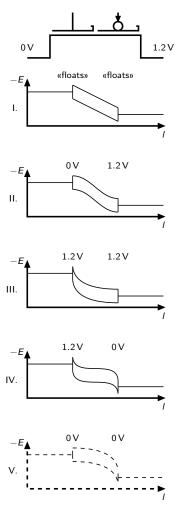

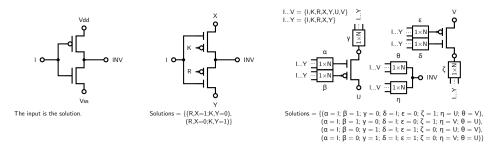

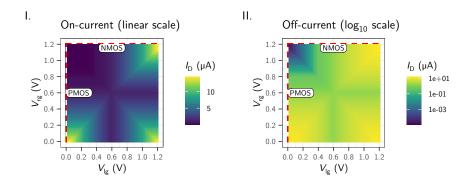

Figure 1.1: Drawing and I–V heat map diagram of a single germanium nanowire RFET from a formal model. 24 nm feature size, comparable to Figure 2.6 on page 26.

The transistor now possesses two gates instead of one. The gates-all-around structure positions each transistor gate at the interface between the metallic wire (dashed), reaching in from the outer contacts, and the semiconductor (stippled). The device can be configured to act as a p-channel field-effect transistor (PFET) or an n-channel field-effect transistor (NFET). By adding another control input, the device polarity can be controlled, in situ, without the need of implanting ions that govern channel polarity like in common CMOS transistors. That is why in this thesis, electrostatically controllable transistors will be referred to as *polarity*controllable transistors. Transistor polarity control is not completely independent of the rest of the device functionality, which means that it only works if all device terminals are charged to certain voltages relative to each other. Voltage changes to the polarity control gate also change whether the channel opens or closes, unless the second control gate is worked in unison with the first. Additionally, some combinations of transistor contact voltages may leave the device in an uncontrolled ambipolar state. Thus, care must be taken to avoid these states or to let a circuit switch as quickly as possible. The heat map in Figure 1.1 shows the drain current for all possible gate voltages and highlights the normal operation modes. While they touch three corners of the diagram, the fourth corner (lower right) shows a fully-developed ambipolar device. A detailed description of the device's functionality is given in Section 2.2.2, pp. 23 ff.

A single device is used to implement both necessary transistor types that make a complementary circuit, and it can change its polarity through an additional input signal. This gives rise to a type of *reconfigurable circuits* that are founded in Shannon decomposition of Boolean functions. These kinds of circuits are complementary and, thus, consist of a pull-up network and a complementary pull-down network of transistors. What makes them special is that they have a working and

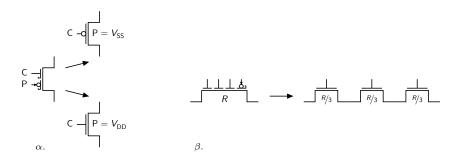

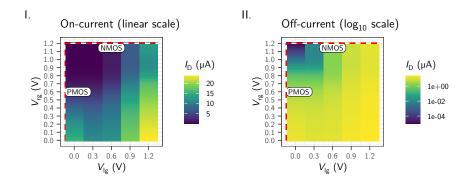

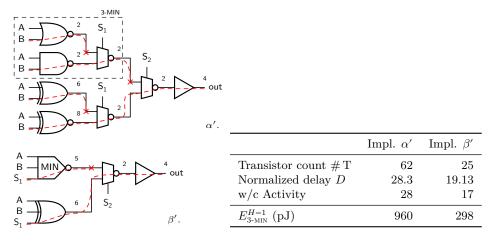

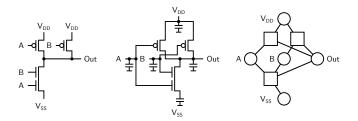

Figure 1.2:  $\alpha$ . Polarity control via second transistor gate.  $\beta$ . Reduced virtual channel resistance compared to a series of CMOS devices by using multiple independent gate FETs.

meaningful implementation regardless of which of the transistor networks functions as the pull-up or pull-down network, as long as they are configured to each others opposite.

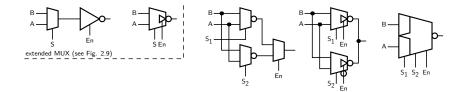

The technology that I dominantly use in this thesis was first shown in [62], expanded into full reconfigurable FETs in [23] and extended with multiple independent control gates in [56] as shown in Figure 1.2  $\alpha$  and  $\beta$ . It is that of a symmetric nanowire polarity-controllable FET, with emphasis put on its p- and n-channel with (nearly) equal conductance properties. While other concepts of circuit reconfiguration work on an architectural level that sits on top of readymade CMOS standard cells, transistor-level reconfiguration acts on the single device inside reconfigurable standard cells. This means, its effect is not only on the logic level but on the analogue electrical level, as well. It is a well-known fact that due to technological limits and architectural choices, PFETs and NFETs are typically individually sized according to their electrical contribution inside a logic gate. Most famous is the delay performance discrepancy of the NAND and NOR standard cells of older CMOS technology nodes. It gives preference to the NAND circuit, because designing the pull-up and the pull-down networks such that they output the same currents results in a structurally and actually smaller and faster design than a balanced NOR circuit of the same technology. Although this is not unanimously true anymore, it serves as the guiding principle that underlines the importance of a symmetric channel conductance in polarity-controllable devices that are used to implement the reconfigurable circuits that are the subject of this thesis. In addition to this observation, reconfigurable standard cell design relies heavily on a property called *reduced virtual channel resistance* that comes with multiple-independent gate devices in small feature sizes (see Figure 1.2  $\beta$ ). The property enables the implementation of wired-AND or series paths that have the same channel current as a single device. They are the second ingredient that ensures that reconfigurable standard cells can develop their full potential.

The polarity-controllable FETs are based on germanium nanowire heterostructures in a gate-all-around design and implement Schottky junction devices that are both controllable and polarity-controllable in the same voltage domain. Thus, an output of one logic gate can serve as either an input or a reconfiguration signal of the next logic gate. This is the third important device property, that enables reconfigurable standard cells to work with in-band reconfiguration signals. It sets them apart from similar transistor technology like floating-gate devices used in non-volatile memory or single-transistor sensors that must usually work with separate voltage domains for distinct operations, i. e. reading/writing or excitation/detection.

Chapter 2 establishes the detailed operation of the polarity-controllable transistor and its relation to reconfigurable circuit design. All of these observations and conclusions are results from early experiments on this subject and while we have seen more reconfigurable transistor device design in the last years, these three properties do not receive special attention from semiconductor research. I suppose, in part, this is due to a lack of feedback from the circuit design community. These devices cannot be easily tested without proper models, that are hard to come by in the early design stages, especially because device modelling is usually a complicated process that needs a lot of data (which is not available in the early stages). So, the lack of device data leads to a lack of testing and experimentation which, in turn, leads to a lack of feedback into the device community. This was one motivation to devise the automated design space exploration and quantitative analysis method that I propose in this thesis.

#### 1.2 Testing and Standard Cell Characterisation

Standard cell characterisation for a new device technology is usually conducted by waiting until the development reaches technology readiness level 4 and a SPICE compact model is created. It can then be used by current tool chains to quantify known standard cell implementations, and new standard cell designs can be drafted and tested in tight loops. Considering early device characterisation, recent works, like [50], extract the important device characteristics directly from FEM simulations and apply curve fitting to increase the accuracy. This results in a table model which is, then, compared to and validated against known technology nodes of comparable sizes. A change in device characteristics requires the construction of a new table model, which requires a lengthy series of FEM simulations. In addition, the table model is usually restricted to a limited set of parameters which represents the "normal conditions" the device is used in. Although the device parameters were extracted from single-device simulations, the whole process works on the abstraction level of standard cells rather than transistor circuits. This means that some intricacies of the transient switching behaviour that can have a major impact on circuit performance may get lost due to abstraction. Additionally, this level of abstraction does not cover the numerous circuit implementation variants that reconfigurable standard cells exhibit and that are shown to have significantly diverging quantitative and qualitative characteristics.

Standard cell characterisation methods that are based on simulations also require a lot of expert knowledge to deliver correct and meaningful results. As with all testing schemes, they can only validate known answers or contradict wrong assumptions. Finding the slowest transient of a standard cell requires the tester to ask for the specific input stimulus that exhibits the transient in question. The system cannot be asked for the slowest transient directly and, thus, cannot qualify a given transient as the slowest.

Formal methods can deliver stronger answers and they have been successfully applied to hardware verification on various levels of abstraction on whole systems [29, 31], in logic synthesis [20] and also on the register transfer level (RTL) by augmenting hardware description languages [7, 19]. Static timing analysis on the logic gate level and the verification of RTL designs using probabilistic model checking [30] or with timed automata [1] have proven the general applicability and tractability of formulating hardware verification problems as formal models. Probabilistic model checking [3] in particular provided the necessary tools to successfully apply formal methods to the research problems in this thesis. By describing the standard cells as, basically, analogue circuits that operate on voltages and currents, I could formulate the necessary queries as independent entities that are able to capture the transient switching behaviour of arbitrary logic gates. Queries are formalisations of measures and properties which can be automatically computed and verified by a model checker. This means that I can ask for quantities like worst-case delay, maximum power dissipation, or Boolean properties like the existence of spurious output hazards directly and get an answer as a numerical result or Boolean with a witness/counterexample. It also means that the query to ask for the worst-case delay is independent of the particular circuit under test. Any circuit of a particular size can be checked against it and the model checker identifies the correct transition and quantifies the result automatically.

#### 1.3 Research Questions

Emerging reconfigurable nanotechnology provides exciting new features and is host to a new kind of reconfigurable standard cell design. Yet, the technology still awaits adoption by both the circuit community, which needs assurance that the technology is ready to be produced and the semiconductor producers that need assurance that there are applications for the new technology. Based on this observation, I aim to address the following overall research goal:

Explore the design of transistor-level reconfigurable standard cells and their effects in combinational circuits. Create an automated approach for early technology evaluation to explore the design space of reconfigurable standard cells and to provide quantitative and qualitative results on key metrics.

Today's circuit and technology evaluation tools are centred around the gradual

evolution of CMOS technology that does not aim to provide early feedback to semiconductor research but that accepts new device parameters as a given and optimises standard cell designs around them. With emerging devices, this becomes a relevant aspect which needs to be addressed in the characterisation workflow. Hence, the overall research goal can be broken down into the following individual questions:

- 1. What is the design space of transistor-level reconfigurable circuits and what kinds of circuit structures and Boolean functions do they support?

- 2. How do reconfigurable standard cells perform in larger circuit designs? How does their performance change with their surrounding circuitry?

- 3. Are simple formal device and circuit models feasible and precise enough to allow for both an automated evaluation and valuable early results?

- 4. Can an automatic quantitative analysis of formal standard cell models be formulated as a tractable problem?

- 5. Can formal modelling and quantitative characterisation be abstracted in such a way that the needed expert knowledge outside electronic circuit design is minimal?

By these research questions, the centre of this thesis revolves around the question whether a formal analysis can provide the expected answers while maintaining enough precision despite its limited scalability that comes with uncontrollable model state space growth.

#### 1.4 Design Space Exploration and Quantitative Analysis

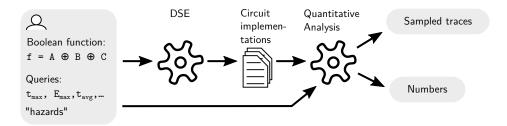

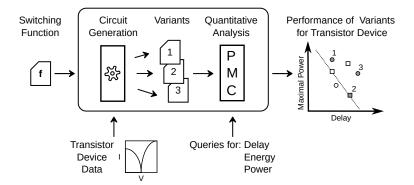

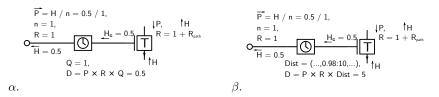

In this thesis, I develop and present the workflow shown in Figure 1.3. Starting with a Boolean function, a set of queries and a set of experiment conditions on the left, the design space exploration algorithm generates all circuit implementations that adhere to certain criteria that are laid out in Section 4.4.1. These implementations are minimal in the number of transistors, which is why the exploration tool is named minimal-circuits. All implementations are generated in the netlist-like language prism-gen, that I developed for this thesis. It addresses three concerns and represents them in a single domain-specific language (DSL), a) the parametrisation of transistor devices, b) the description of transistor circuits in a netlist and c) the description and parametrisation of a test fixture. Chapter 4 goes into the depth of describing the inner workings of the DSL. Its main purpose is to provide useful interfaces between the three concerns such that the circuits under test can be constructed independent from the exact transistor being employed. Also, the test fixtures, which are bound to the queries that shall be answered with them, are usually the same for all circuit implementations of

Figure 1.3: Design space exploration and analysis workflow for reconfigurable standard cells.

a single reconfigurable standard cell. So, they too should be independent of the particular circuit implementation. Thus, **prism-gen** enables a designer to analyse multiple circuits in different test fixtures using various transistor devices without the need to rewriting undue amounts of code. The transistor device models are independent of the circuits and are delivered as library elements. Yet, they are still accessible in **prism-gen** such that they can be scaled or even parametrised (e. g. see the drain current imbalance analysis in Figure 2.3 on page 22).

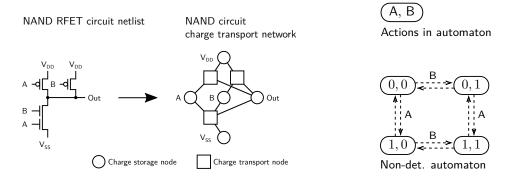

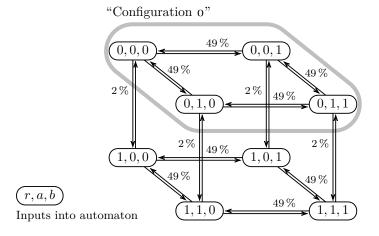

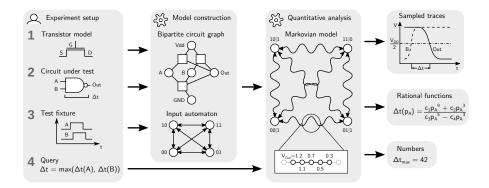

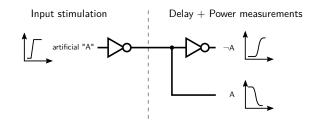

The output of the prism-gen compiler is a formal model, more precisely a Markovian model, of the whole experiment that can be processed by the model checker PRISM. The formal model encodes the electrical network as a bipartite graph as can be seen in Figure 1.4 in the example of a NAND circuit that is transformed from the netlist description into a charge transport model. The graph contains the circuit structure and transistors (as charge transport nodes) as well as an input automaton which limits the time and value relations of the circuit input stimuli. One example of an input automaton is shown at the right of Figure 1.4. This automaton describes all possible state transitions of the circuit inputs and contains additional restrictions as to when the next set of transitions is allowed to occur. It usually ensures that the circuit output has stabilised before the next input stimulus is triggered. So, by describing a rule by which the input stimuli may develop, instead of a fixed trace of input stimuli at fixed intervals, the model checker is able to explore all relevant input transitions by itself. Queries that assess worst-case properties work on non-deterministic automata while queries that implement statistical application behaviour work on probabilistic automata. This is reflected in two separate test fixtures with two different input automata.

The last input into the DSE and analysis workflow are the queries, which correlate with their experiment models. They are also largely independent of the circuits in question and usually only depend on the number of inputs into and outputs out of the experiment. Both the DSE and the quantitative analysis run completely automatic, delivering different kinds of output, depending on the query. Most queries deliver direct numeric results, but for some analyses, it might be worthwhile to look at the transient behaviour of the circuit under test. This is delivered as witness states by the model checker which can be used to generate the

Figure 1.4: Left Conversion of a netlist circuit description into the formal model by prism-gen. Right A typical non-deterministic input automaton with inputs A and B that is compatible to the circuit.

sampled traces in question. Lastly, the model checker is able to return a rational function that can generate the numeric results of a family of input parameters. So, instead of re-running the costly quantitative analysis for a new set of input parameters, the problem can be reduced to computing a simple rational function.

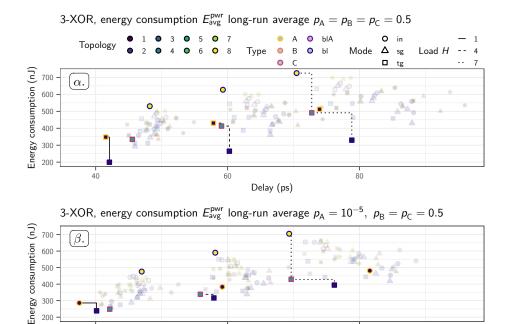

One of my contributions is, that I use this automated workflow to perform a mass analysis of two reconfigurable standard cells which, together, have more than 60 implementations. More than 900 experiments deliver all interesting quantitative and qualitative results that are shown in Chapter 5.

#### 1.5 Contribution

The collaboration with semiconductor research uncovered a demand for early circuit characterisation and device performance projections in standard cells. One additional aspect was to have a device model that is easy enough to be altered when more beneficial characteristics are determined from experiments or when the device production work flow would change the final device characteristics, which make reevaluation necessary. As the semiconductor producing industry is very conservative, strong predictions regarding viable circuit architectures were also sought for as a convincing tool to pick up the new transistor devices.

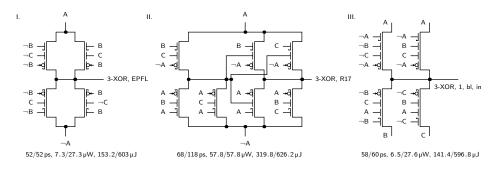

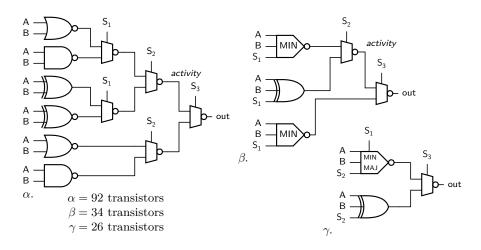

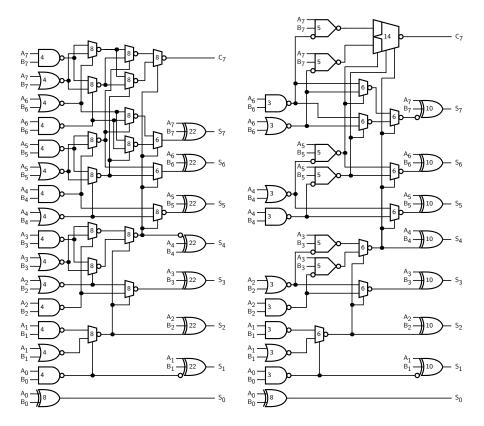

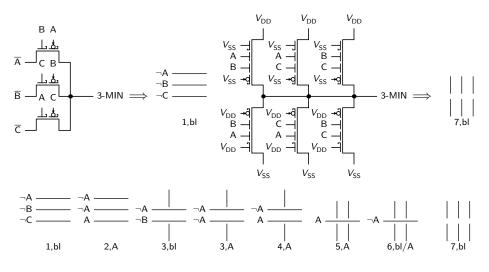

The contributions of this thesis are the research of fundamental reconfigurable logic gates to show the conceptional foundation of transistor-level reconfiguration and the several reconfiguration types that exist and reconfiguration modes that can be used to drive the circuits. This thesis also shows the feasibility of reconfigurable standard cells in larger combinational circuit designs and their usefulness in implementing higher-order functions, their contribution to the reduction of circuit complexity and performance improvements. Its main contribution is a comprehensive design space exploration and analysis method for reconfigurable digital circuits that is built on formal methods. It is used to show the automated exploration and comparative analysis of the 3-MIN and 3-XOR functions and their various reconfigurable implementations. Multiple measures are covered in the quantitative analysis for a range of experiment conditions.

Fundamental reconfigurable circuits Reconfigurable circuits that are based on polarity-controllable transistors, like germanium nanowire devices [56], implement a certain kind of reconfiguration that exploits Shannon decomposition of Boolean functions. In Chapter 2, I investigate fundamental circuit implementations and how they make use of polarity-control and the reduced series resistance of multiple-independent gate transistors. Device geometry, functional and performance symmetries turn out to play a major rôle in the effectiveness of the device for a well-performing reconfigurable circuit. I infer three device reconfiguration modes and their influence on circuit design possibilities.

Combinational circuits Reconfigurable implementations of logic gates have to prove their efficiency in larger circuit designs. In Chapter 3, I compare the reconfigurable implementations of basic logic gates to their standard CMOS counterparts implemented in a state-of-the-art device node. Their structural differences are shown by comparing their logical efforts (see [53]) in addition to absolute delay values. Strong variability of results motivate the later analysis of the whole spectrum of reconfigurable implementations of a certain logic gate, as neither the logical effort nor the delay are sufficient to judge the trade-offs between circuit structure and performance. In that chapter, I also show the improvements that reconfigurable standard cells can bring to computation-oriented circuits, by implementing an ALU with higher delay performance and less energy consumption. A complex conditional sum adder serves as the example for how reconfigurable standard cells can improve circuit characteristics if their reconfigurability is not a user-visible function but remains embedded to compress a fixed circuit functionality into a smaller circuit design.

Constructive circuit exploration and analysis The initial studies show that a comprehensive analysis of reconfigurable circuit implementations is necessary to determine their actual performance range and their suitability in the design of combinational circuits. Additionally, reevaluation, performance projections and adaptation to modified transistor characteristics are a main goal for the methodology and tool set that I present in Chapter 4. While hand-picked implementations could show the feasibility, the comparison between the technologies also showed that the actual performance depends on intricate details of the circuit structure and the individual transistor device. Thus, the methodology must allow a researcher to perform an automated exploration and analysis of the reconfigurable implementations of a certain Boolean function. In this thesis, I devise a charge transport network model that operates on simple analytical transistor de-

#### 1. INTRODUCTION

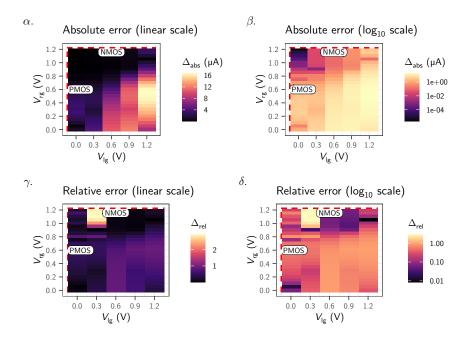

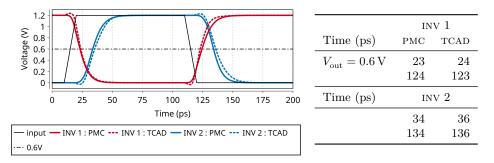

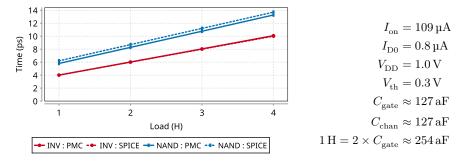

vice models. It is precise enough to capture the analogue device behaviour and is, yet, simple enough that it can be implemented as a formal model. This model is built and analysed by the probabilistic model checker PRISM which checks deviceand circuit-independent queries against it. They can directly answer questions for extremal values like worst-case delay and power dissipation as well as support the detection and enumeration of spurious output hazards and the verification of circuit functionality. The models and the experiment descriptions are implemented in the domain-specific language prism-gen that abstracts the model details into a netlist-like description language that enables the composition of complex circuits from simpler ones while maintaining detailed access to single transistor or experiment properties if necessary. To show the validity of the proposed method, I compare the germanium nanowire model against TCAD simulation data from [58, 56]. Additionally, I also implement the CMOS production device from [41] and compare the performance of standard cells implemented in the proposed method against commercially available SPICE models to show the precision of network and device model at a circuit level. The design space exploration of reconfigurable circuit implementations is constructive such that in a given set of constraints, all implementations are considered and are guaranteed to be functionally correct. I also show why timed automata are not a suitable implementation technique despite being an established method and successfully used in hardware verification on the register-transfer level.

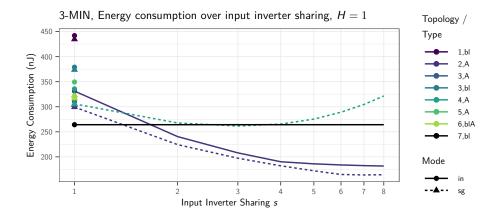

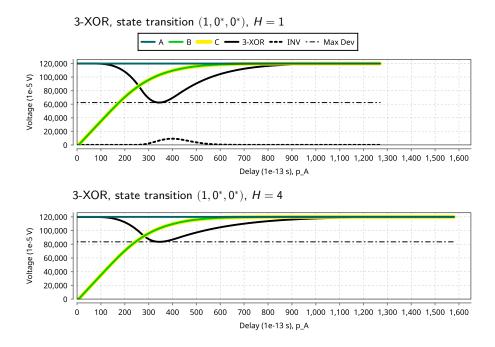

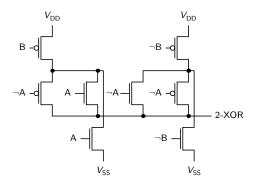

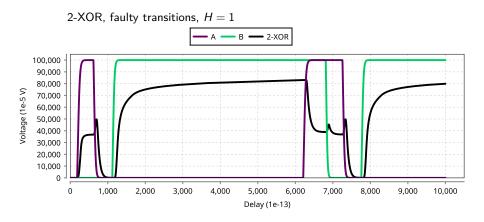

Automated quantitative analysis To put the proposed method to the test, I present a comprehensive evaluation of two significant Boolean functions, which shows its range and abilities. In Chapter 5, I show a worst-case analysis of all reconfigurable 3-input minority circuit variants in comparison to each other and the static implementation. The analysis reveals that both input inverter sharing and output load sensitivity must also be considered to get a complete picture of the performance properties of individual implementations as worst-case analyses prove to be too simplistic to capture all realistic use cases. To address computation-intensive scenarios, I also investigate the 3-input exclusive-OR function. This analysis includes hazard detection and shows that the direct access to extremal values uncovers the worst-case states for different measures like delay and energy may deviate from each other, underlining that each measure warrants an independent analysis that is easily achievable with the proposed method. Future technological improvements will have to concentrate on improving the average performance case, because this is where the most optimisation potential lies for best-effort computing. This is especially true for measures like energy consumption, in which short extreme outliers can be easily tolerated. These measures are hard to come by with simulation techniques but become accessible with probabilistic model checking. I show longrun average results for the 3-XOR circuits and parametric delay calculations whose results are directly usable in future EDA tools.

### Chapter 2

# Fundamental Reconfigurable Circuits

Reconfiguration and reconfigurable hardware has settled in a prominent niche in both research and application since the 1990's when it became powerful enough to serve as an implementation basis for real-world applications. It has become a fixed go-to implementation vehicle for certain high-bandwidth software-defined communications and filtering applications with ever-varying degrees of reconfigurability. Its success hinges on its ability to strike a balance between the system architect's (or user's) uncertainty of the exact computation that the target system needs to perform and strong requirements regarding computational efficiency. Uncertainty requires some degree of programmability which directly conflicts computational efficiency, which is either dictated by necessity in cyber-physical systems or has monetary reasons in best-effort computing applications (faster = more money). Additionally, programmable systems are, at least somewhat, adaptable to new conditions and repairable in the field.

There has been numerous preliminary work on reconfigurable hardware design and architecture. Principle work and how the approach in this thesis differs from it is introduced in Section 2.1.1. The concept of *reconfiguration*, as explained in the next section, is closely tied to the fundamental transistor device that enables the digital circuitry in the first place. It is no architectural concept that sits on top of regular CMOS standard cells. Numerous transistors have been proposed that would be suitable as implementation vehicles for the kind of reconfiguration described in this thesis. Silicon and germanium nanowire transistors that use Schottky junctions are one class of devices and are shown in [62, 23, 56, 51, 11]. They also serve as the implementation devices to showcase the quantitative standard cell characterisations in this thesis, because their development already produced sufficient research data to not only model the devices but to also validate the models against independent simulations. Dual metal-gate planar FETs are proposed in [28], but carbon nanoribbon devices ([16]) and other 2-D material devices ([44]) also show promising characteristics regarding polarity controllability. For instance, heterostructures from carbon nanotubes and the 2-D material  $MoS_2$  that form a reconfigurable tunnelling transistor are shown in [33].

#### 2.1 Reconfiguration Redefined

The term *reconfiguration* will be used often throughout this thesis and, thus, warrants an explanation of what is understood as reconfiguration and how it is different from common usage throughout the field. Reconfiguration, in this work, is bound to a technological ability of the primary active component, the transistor. The transistors we consider in this work, and which will be detailed in Section 2.2, all have the ability to have their channel polarity electrically controlled. Thus, they can conduct either positive charge carriers or negative charge carriers, controlled by an additional input. In combination with certain circuit topologies, introduced in Section 2.3, polarity control enables us to perform different Boolean functions depending on the *configuration* of the polarity-control inputs of the transistors. The circuit is said to be *reconfigured* from one Boolean function to another.

#### 2.1.1 Common Understanding of Reconfiguration

Circuit design always has been an industry-driven field of research. This means that terms do not always have their foundation in science but may stem from product marketing. When looking closely at the use of the term *reconfiguration* it becomes apparent that it is used more colloquially than in a precise narrow meaning. Programmable array logics (PALS), programmable logic arrays (PLAS) and field-programmable logic arrays (FPGAS), for instance, are clearly considered reconfigurable circuits but are called *programmable*. Their implementations also differ a lot from each other.

The PAL was first described in [5] as an array of programmable fuses. Each input signal is driving two columns of the array, one as direct value and one inverted. Programmable fuses allow the designer to connect each column to select rows, which then connect to (4-input) AND gates. Two AND gates are pair-wise connected to a final OR gate, whose output signal can be used directly or inverted. This means, all logic must be expressed in product terms under consideration of the limitations introduced by the AND and OR logic after the array. Routing and the construction of sequential logic must be done off chip by connecting an output to another input. Configuration strictly considers the description of product terms and output signal inversion. Reconfiguration is not possible in these devices so they are, strictly speaking, not reconfigurable. Nevertheless, they introduce the important concept of a semiconductor fabric whose connections are done in late

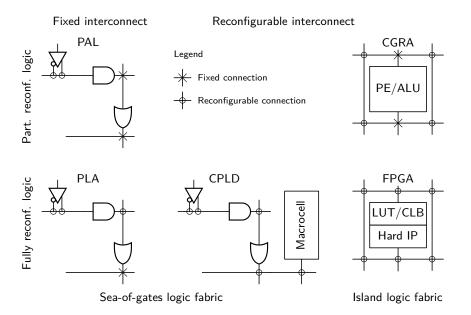

Figure 2.1: Comparison of common reconfigurable architectures along three axes: reconfigurability of the logic fabric, reconfigurability of the interconnect, and the design of the logic fabric.

production depending on the intended application.

The PLA extends this concept, as described in [22], by introducing a second matrix between the AND gates and the OR gates. Again, each AND gate drives two rows, directly and inverted, which can be connected to select columns via fuses. A number of columns, usually eight, drives a single OR gate. This design does not change the fundamental expressivity of its reconfiguration nor does it change the level of architecture it is applied on, but it enables a better compression of the logic functions by enabling the expression of logic in configurable sum-of-products terms. Most notable, product terms that are far away from each other or use radically different inputs can now be shared between several OR gates as these no longer only connect to neighbouring AND gates. The architecture also features internal feedback paths, leading to a more reliable sequential logic, as their impact on signal propagation and latency can now be depended upon.

The deciding technological step forward comes by the use of erasable fuses to implement the configurable connections which are introduced in programmable logic devices (PLDs) and complex programmable logic devices (CPLDs). Though their fundamental fabric design is similar to PLAs, they can be reconfigured in the field. Architecture-wise, CPLDs contribute macrocells (hard macros or hard intellectual property cores (IP cores) in modern terms) in addition to the seaof-gates logic fabric and the programmable interconnect, which can multiplex between multiple instance of logic fabric and macrocells. The interconnect allows for deeper logic and carrying inner state by providing internal feedback paths and defined ways to construct flip flops.

FPGAs were introduced in [8] and make an important step forward to the, now common, understanding of reconfiguration by introducing several new reconfiguration primitives. They introduce the 2-dimensional array architecture of programmable logic elements surrounded by programmable routing, which was pioneered in a fixed form by contemporary fabricated gate arrays. They are also the first devices to use static random access memory (SRAM) to capture the device program instead of PROMS or fuses. Although at the time of its inception it was still two decades away from its realisation, this gave rise to the idea of dynamic hardware; hardware that can be reconfigured not only in the field but even in operation, so, while the surrounding hardware still performs its function. Today, this concept is subsumed under the name of dynamic partial reconfiguration or dynamic function exchange. Another important architectural contribution is the use of lookup tables (LUTs) for Boolean function implementation instead of a sea-of-gates design. Implementing the full truth table of a function, which looks excessive on paper, turns out to be the driving factor for a flexible, synthesisable and routable logic design, as it simplifies the natural entanglement of logic placement and routing by featuring constant-delay Boolean functions, as long as they fit into a single LUT. Finally, replacing crossbars with chains of pass transistors enables a flexible 2-dimensional routing. FPGAs introduce reconfiguration on another architectural level, the interconnect. Starting with CPLDs, the programmable interconnect inside an FPGA is highly structured into local connection, longer uninterrupted connections and long lines that can reach across the chip. In addition, FPGAs feature a separate, low-skew clock network with the ability to cross signals from and to either network to achieve maximum flexibility and highest performance. Switch boxes form the programmable part of the interconnect and allow for efficient XY routing across the FPGA's surface. This 2-dimensional network of routes with islands of hard macros and configurable logic blocks in between result in the most powerful and versatile reconfigurable architecture to date, with a 14 times larger market size of 6 billion US dollars [61], than CPLDS, with a market size of 421 million US dollars [49] in 2021.

All this flexibility comes at a high price, though. Computing the logic placement and the routing between the placed logic are both interdependent and NPhard problems in themselves. Computing even simple designs needs several orders of magnitude more powerful machines than for the next class of reconfigurable architectures, the coarse-grain reconfigurable architecture (CGRA).

CGRAS can be regarded as a set of arithmetic logical units (ALUS) connected by a network on chip (NoC). This means, they can be considered distributed processing systems but are called (coarse-grain) *reconfigurable*. Their strength lies in the focus on efficiently connecting common-case processing elements and can be considered a case of the principle *Convention over Configuration*. By having a convention that defines the interface between the processing elements, i. e. a 64-bit bus, request-acknowledge signals or a common clock, routing between numerous processing elements becomes a more constrained and, thus, easier task. It also reduces the size of the device program by several orders of magnitude, enabling successive reconfiguration while in operation. Reconfiguration works completely on a high architectural level, specifying the abstract connections between complex processing elements.

This shows that reconfiguration can neither be pinned to a specific mechanism nor a specific architectural level, nor a specific algorithm. Figure 2.1 shows the evolution from PALs to CPLDs, the revolutionary change in architecture in FPGAs and the simplification back to partially reconfigurable logic to gain speed and run-time reconfigurability in CGRAS.

In very general terms, reconfiguration can be described as a mechanism, that allows a designer to modify the functionality of an integrated circuit. The access to this mechanism and the resources it acts upon inside the integrated circuit are not part of the regular logic that integrated circuit uses to drive the target application. So, a reconfigurable circuit always uses some extra resources to govern the interaction between and functionality of the user-visible logic resources.

It is important to note that any implementation of an algorithm conceptually consists of at least three parts, a data path leading from the input to the output, a reducer component destroying entropy (thus, performing a computation), and a control path that steers the behaviour of sub-components. These are the same parts that constitute a Turing machine, the way of data from the band through the head, the head as the mechanism performing mechanical work and the rules that describe what actions the head can perform. While the band is regarded part of the Turing machine, data memory is normally not regarded as being part of an algorithm. Circuits cannot be an exception to this observation.

So, using this mental model to approach reconfiguration of circuits, we arrive at the same concept we traditionally use in computer science, programmability. The control path is the implementation of our program and can, in general, be fed by input on the data path. Like in central processing units (CPUs), the behaviour of the reducer components depends on the input. When an ALU is either computing, say, addition or subtraction, the circuit is (re-)configured to perform either computation. One could argue, that the difference between these two is, that the ALU is always performing both operations and we merely control the propagation of the results or, even if we halt execution of unused units, we still need to have them physically implemented. Whereby in a reconfigurable circuit, the unused logic is not even there. Well, for reconfiguration I will be talking about later in this work, this is not true. There will be no unused logic sitting dark as a consequence of reconfiguration. Also, to be truthful, one must accept that reconfigurable circuits must also keep unused resources around. If we could build a reconfigurable circuit precisely with the amount of logic that we needed for our application, it would not need to be reconfigurable at all but would already be the final application-specific integrated circuit (ASIC). So, neither of the two are valid arguments to treat reconfiguration in FPGAs any different from programming circuits like CPUs.

So, while it might be useful to distinguish reconfiguration from programming, this distinction has no solid scientific foundation. It is rather a social distinction like differentiating between scripting (as in JavaScript) and programming (as by programming in C). At least, its usefulness highly depends on how narrow the communication context is in which reconfiguration needs to be set apart from computation.

#### 2.1.2 Reconfiguration is Computation

In this thesis, I will use reconfiguration in a restricted meaning that is defined by the polarity-control feature of the transistors that I use. Used in complementary logic circuit designs, it can be captured by the mathematical formalism of self-dual Boolean functions.

Using polarity-controllable transistors, a complementary circuit is reconfigured by changing the sensitivity of a particular transistor towards its inputs, which is equivalent to changing its channel polarity from NMOS to PMOS or vice versa. That is why I call this mode of reconfiguration transistor-level reconfiguration. Mapped to a whole complementary logic circuit, this means that parts or all of the PMOS network is reconfigured to an NMOS network and, at the same time, its complementary part is reconfigured in reverse. For complementary logic circuits, this mode of reconfiguration completely stays in the Boolean domain or the Boolean domain is closed under reconfiguration. The difference to reconfigurable LUTs is that transistors can be individually reconfigured, giving transistor-level reconfiguration greater power to also perform non-Boolean reconfiguration. With few exceptions, which are expressly mentioned when they appear, this work concentrates on constructing, evaluating and showcasing logic circuits that make use of purely Boolean transistor-level reconfiguration.

Now, the mathematical foundation to Boolean transistor-level reconfiguration lies in self-dual Boolean functions.

**Definition 1** A neutral function is a Boolean function that has equal number of min terms and max terms.

Additionally, self-dual functions must not have mutually exclusive terms because otherwise they could not have a dual term for each other term.

**Definition 2** Two Boolean terms, which are both either conjunctions or disjunctions, are called mutually exclusive iff.

- 1. they use the same variables,

- 2. all their variables are complementary to each other and

- 3. they evaluate to the same output.

| a | b | Out | Term                               | Self-dual term                   | Expected Out (by $n$ 'th row) | Mutually<br>exclusive term       |  |  |

|---|---|-----|------------------------------------|----------------------------------|-------------------------------|----------------------------------|--|--|

| 0 | 0 | 1   | $\overline{a} \wedge \overline{b}$ | $a \lor b$                       | 0 (by 4)                      | $a \wedge b$                     |  |  |

| 0 | 1 | 0   | $\overline{a} \vee b$              | $a \wedge \overline{b}$          | 1 (by 3)                      | $a \lor \overline{b}$            |  |  |

| 1 | 0 | 0   | $a \lor \overline{b}$              | $\overline{a} \wedge b$          | 1 (by 2)                      | $\overline{a} \lor b$            |  |  |

| 1 | 1 | 1   | $a \wedge b$                       | $\overline{a} \vee \overline{b}$ | 0 (by 1)                      | $\overline{a}\wedge\overline{b}$ |  |  |

TABLE 2.1: EXAMPLE OF A BOOLEAN FUNCTION THAT IS NEUTRAL BUT NOT SELF DUAL. EACH TERM AND ITS DUAL TERM IS DESCRIBED AS IS THE EXPECTED OUTPUT TO MAKE A PARTICULAR ROW SELF-DUAL TO ITS DUAL ROW.

**Definition 3** The dual term B' of a Boolean term B is defined as the term that is constructed from B by replacing all binary and unary mappings with their inverses (e. g.  $\lor \leftrightarrow \land$ ,  $\circ \leftrightarrow \overline{\circ}$ ) and exchanging the neutral elements (e. g.  $0 \leftrightarrow 1$ ).

Let us consider Boolean terms over three variables a, b and c. The mutually exclusive term to  $\overline{a \wedge b \wedge c}$ , which is  $a \wedge b \wedge c$ , cannot be equal to the dual term, which is  $a \vee b \vee c$ . If that would be the case, it would mean that the output of the function that uses these terms does not depend on the three variables, at all.

**Definition 4** A self-dual Boolean function is a Boolean function equal to its own dual, i. e. each of its Boolean terms is replaced by its dual. A Boolean function over n variables is called partially self-dual when it contains a self-dual Boolean function over k variables with k < n.

An in-depth explanation of self-dual functions and their properties can be found in [4].

The Truth table 2.1 for the function over two variables has  $2^2 = 4$  lines, some of them minterms some maxterms depending on the function value. And each one is mutually exclusive to one and only one other term as shown in the column Remark. The table also lists the term, its accompanying dual term and, given the dual term's output from the truth table, the expected output to make both terms dual. Only when the output and the expected output match for each line, is the function self dual.

The smallest non-trivial self-dual Boolean function is over three variables and is shown in Table 2.2. While the left half of Table 2.2 lists all possibly self-dual functions over two variables. Closer inspection reveals, though, that none of them depends on both variables. This concludes that there are no self-dual Boolean functions over two variables. It is the 3-input minority function, which has the added benefit of covering the complete Boolean algebra, due to it being usable as an inverter. This function is self-dual in every variable. So, each variable can be used to select between a term and its dual, and it does so for all terms of the function. This property can be directly translated into a mechanism that provides Boolean transistor-level reconfiguration.

TABLE 2.2: LEFT: ALL POSSIBLY SELF-DUAL DYADIC BOOLEAN FUNCTIONS. NONE AC-TUALLY DEPEND ON BOTH VARIABLES, PROVING THAT THERE ARE NO SELF-DUAL DYADIC FUNCTIONS. RIGHT: EXAMPLE OF THE SMALLEST NON-TRIVIAL SELF-DUAL FUNCTION WHICH ALSO COVERS THE COMPLETE BOOLEAN ALGEBRA, THE 3-INPUT MINORITY.

| a | b |                |   |                | l dyadic<br>nctions |  | a | b | c | 3-mi |

|---|---|----------------|---|----------------|---------------------|--|---|---|---|------|

| 0 | 0 | 1              | 0 | 0              | 1                   |  | 0 | 0 | 0 | 0    |

| 0 | 1 | 1              | 0 | 1              | 0                   |  | 0 | 0 | 1 | 1    |

| 1 | 0 | 0              | 1 | 0              | 1                   |  | 0 | 1 | 0 | 1    |

| 1 | 1 | 0              | 1 | 1              | 0                   |  | 0 | 1 | 1 | 0    |

|   | f | $\overline{a}$ | a | $\overline{b}$ | b                   |  | 1 | 0 | 0 | 1    |

|   |   |                |   |                |                     |  | 1 | 0 | 1 | 0    |

|   |   |                |   |                |                     |  | 1 | 1 | 0 | 0    |

|   |   |                |   |                |                     |  | 1 | 1 | 1 | 1    |

**Definition 5** Given a self-dual function f over n variables and the variables be partitioned into a set of reconfiguration variables R and a set of static input variables S. Boolean transistor-level reconfiguration maps reconfiguration variables to the polarity-control inputs and source inputs of transistors such that the resulting logic circuit implements the set of dual terms, switching between either the term or its dual depending on the values of the reconfiguration variables.

This is the definition of reconfiguration that will be used throughout the remainder of this document unless noted otherwise.

#### 2.2 Reconfigurable Transistor

Self-dual Boolean functions and their relation to reconfigurability are directly reflected in the electrical behaviour of the transistors I am going to use in this thesis. The devices used in the remainder of this thesis are nanowire transistors built in a silicon or germanium technology. They were conceived with their basic electrical characteristic in mind, which sets them apart from off-the-shelf MOSFET devices—their ability to change the conductance of their channel between  $e^-$  carrier conductance to  $h^+$  carrier conductance with the help of an extra transistor gate. As it turns out, when implementing static CMOS logic gates, this property coincides with Boolean self-duality.

#### 2.2.1 Device geometry

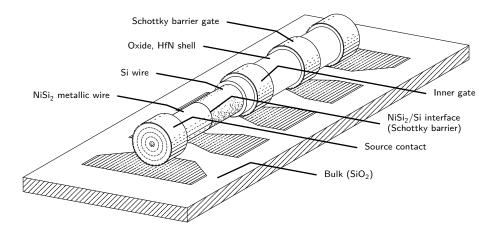

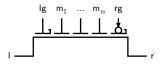

Industrially manufactured nanowire transistors are etched out of the bulk material in a top-down process, comparable to standard CMOS devices. The drawing of an ideal silicon nanowire (SINW) transistor in Figure 2.2 shows a grown device which

Figure 2.2: Idealised drawing of a grown silicon nanowire transistor. At its core, the silicon wire and metallic  $NiSi_2$  wires form a heterostructure with two Schottky barriers. All-around gates over the barriers control the channel polarity and conductivity. Additional inner gates add a wired-AND functionality to the device without impacting device performance.

is functionally the same but whose components are easier to identify and explain. It's proportions were chosen for instructive purposes and are not to scale. All hatched components in Figure 2.2, like the contact surfaces, depict metallic parts, white surfaces are oxides, and stippled objects are semiconductors.

In production, the wire is grown under a gold particle or etched from the bulk material. After formation, the wire is metallised from its ends by intrusion of nickel, forming nickel silicide ( $NiSi_2$ ). Nickel silicide keeps a sharp interface to the silicon wire and its intrusion depth can be controlled by keeping a precisely timed temperature profile or by depositing exact amounts of nickel onto the source and drain contacts and run the intrusion until all material is depleted.

It is important that the NiSi<sub>2</sub>/Si interface forms directly under either of the outer gate contacts for maximum control over the Schottky barrier and, thus, good device performance (cf. [56] pp. 18). The Schottky barriers form an energy barrier for either types of charge carriers which cannot be overcome by the voltage difference between the source and drain contact. Each Schottky barrier gate can deform the conduction band along the semiconducting middle wire section and depending on the material, the gates need about 0.6 V(Si) or 0.3 V(Ge) difference to the source to allow charge carriers to tunnel through the barrier (the device-intrinsic threshold voltages). For reasonable wire lengths (up to a few hundred nanometres), charge transport inside the semiconducting section is ballistic, which is the reason that the inner gate shown in Figure 2.2 does not increase the channels intrinsic resistance and, thus, does not negatively affect device performance. Inner gates show different performance characteristics than Schottky barrier gates which

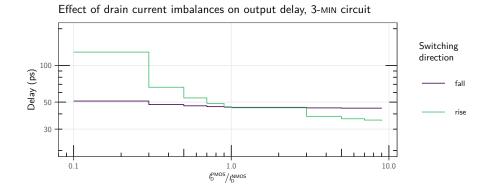

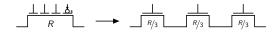

Figure 2.3: Modeling of the effects of an imbalance of drain currents between PMOS and NMOS configurations of germanium MIGFETS. 3-MIN circuit variant 1,bl,sg, output load H = 1, worst-case delay.

relate to the physical structure of the device. As they do not influence a Schottky barrier, inner gates have a smaller threshold voltage, thus, need less energy and usually switch faster than their Schottky barrier siblings. It is also possible to have multiple inner gates on a single nanowire and reconfigurable circuits will make use of them.

The geometry of SINW transistors has another benefit that becomes important for building reconfigurable circuits. The amount of material in the hafnium nitride (HfN) shell can be used to parametrise the on-current through the wire. Changing the thickness of the shell changes the pressure on the wire, which influences charge carrier mobility differently for  $h^+$  carriers than  $e^-$  carriers. This way, apart from unavoidable production variations, the PMOS and NMOS on-currents can be balanced out enabling the design of CMOS logic gates without severe performance imbalances.

Figure 2.3 shows the effects of drain current imbalances on circuit performance. The graph depicts the worst-case delay of a fully reconfigurable 3-MIN circuit, specificly the variant 1, bl, sg, which is similar to the one shown in Figure 2.10 I, over the quotient  $I_{\rm D}^{\rm PMOS}/I_{\rm D}^{\rm NMOS}$ . The nomenclature of circuit variants will be explained further in Chapter 5, but the signifier *bl* stands for a distribution of the reconfigurable signals over all input signals and the *sg* describes the reconfiguration mode the transistors are used in and is explained Table 2.3.

The results were retrieved by the model checking approach that is also explained in full detail in Chapter 4, but they are not measurements or simulation results but exact numbers (within the precision of the model). The curves show the rise and fall delay separately, to distinguish PMOS-driven switching events from NMOS-driven events. As can be seen from Figure 2.3, for this particular circuit, there is a zone between 0.8 and 3 in which the imbalance as almost no effect on the worst-case output delay. This is well within range of fabrication tolerances, such that current imbalances, although being a factor to consider are not a show stopper to transistor-level reconfiguration.

As shown in Figure 2.2, the device is completely symmetric around its middle point. This is also true for the produced device, thus, all names, such as source and drain contact or program and control gate, can be given to any suitable point of the device and only bear meaning in direct relation to each other or the surroundings of the device but not to physical points of the fabricated transistor. This means that the contact points in Figure 2.2 could be named in reverse.

The example shown in Figure 2.2 features silicon as an example technology mainly, because this was the most advanced nanowire technology available during the research for this thesis. Nonetheless, germanium nickel-based nanowires have been shown in [56] and various other 2-D materials have been demonstrated that follow the same basic concept and have similar properties. So, although, the example may come across as being limited to a particular technology, it was chosen for its simplicity and availability of research data, which was most important for developing circuits and models on top the device itself. I will use silicon and germanium devices, concepts and data, based on the theses of André Heinzig [23] and Jens Trommer [56] interchangeably and where it fits the purpose of proper display. As long as some basic electrical properties are retained, the actual device is not of importance to the applicability of the approaches demonstrated in this thesis. I refer the reader to above theses for an extensive read on the construction of nanowire transistors.

#### 2.2.2 Electrical properties

To make it easier to grasp the transistor characteristics, we will use the following conventions to name the device terminals. In logic gates, the *source contact* will be placed on the input side or on the outer edge of the circuit, where the input signals and voltage supply is connected; the *drain contact* will always point to the output or the middle of the logic gate. This placement is used for both NMOS and PMOS transistors and is unlike the conventional terminology used in CMOS logic gates. These conventions will become important in later chapters concerning the abstraction of the transistor device into a probabilistic model.

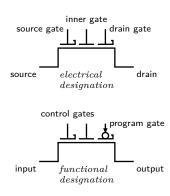

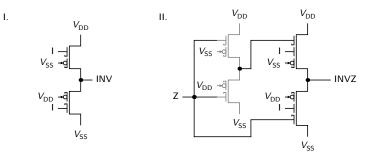

The top circuit symbol in Figure 2.4 directly corresponds to the geometrical layout shown in Figure 2.2. Following the drawing style of Schottky devices, the Schottky barrier (SB) gates are drawn with hooks. Unlike other Schottky device symbols, the hooks are only drawn towards the drain side of the device and, following above conventions, will point to the middle axis of a CMOS logic gate. The naming of gates and contacts is no longer arbitrary and the gate with the hook facing towards the contact is always the drain-side gate, which is also the output side. By using these drawing conventions, each transistor gate can be assigned a fixed function out of two.

The bottom drawing in Figure 2.2 shows that the program gate, which is

responsible for controlling the channel polarity and thus the PMOS or NMOS characteristic, sits at the drain side. It is always a Schottky barrier gate. The inversion circle marks this gate as being connected to the device's polarity, and the arrow towards it shows that the transistor's polarity is controllable via a voltage applied to the gate. All other transistor gates are called *control gates*, as either can steer the channel open or close, but they do not affect the channel polarity. Control gates never carry an inversion circle to mark PMOS channel polarity, which must be deduced solely from the program gate input.

The term RFET is used for the whole class of reconfigurable transistors and, generally, I will make no distinction between RFETs that employ exactly two transistor gates and three independent gate fieldeffect transistors (TIGFETs) or MIGFETs. In addition, I will not discriminate polarity-controllable transistors shown in works of the École polytechnique fédérale de Lausanne (EPFL), in which the two outer gates are electrically connected and work in unison. In the circuit drawings throughout this document, transistors may have two or more gates which work independent unless explicitly connected, and whose characteristics are according to the following paragraphs unless mentioned otherwise.

Figure 2.4: RFET terminal