# Picosecond-Precision Clock Synchronized Radio Access Networks using Optical Clock Distribution and Clock Phase Caching

Kari A. Clark, Zichuan Zhou, Zhixin Liu

Optical Networks Group, Department of Electronic and Electrical Engineering, UCL, Gower Street, London, WC1E 6BT, United Kingdom kari.clark.14@ucl.ac.uk

**Abstract:** We show 0.98-ps precision clock synchronization for radio access networks, in a real-time field-trial demonstration on 37.6-km dark fiber, with optical clock frequency synchronization and clock phase caching operating using 25.6-Gb/s commercial transceivers. © 2022 The Author(s)

#### 1. Introduction

Emerging time-critical applications such as augmented reality devices, connected car fleets and precise co-ordination of industrial equipment require time synchronization to at least sub-nanosecond accuracy for sub-meter positioning, using, e.g., trilateration [1,2]. Although satellite-based global navigation satellite systems (GNSS) (e.g. the Global Positioning System (GPS) and BeiDou) are currently used for sub-nanosecond time synchronization and sub-meter positioning [3], enabling these services through fiber radio access networks (RANs) would enable sub-meter positioning in locations that are difficult or impossible to reach using GNSS: underground (e.g. on subways), in buildings and in urban canyons [4]. Fiber network time synchronization is also crucial for ensuring critical national infrastructure resilience during GNSS interruptions [5] (e.g. caused by solar flares, volcanic eruptions, cyberattacks).

Current time dissemination in RANs combines the precision time protocol (PTP) [6] with synchronous ethernet (Sync-E) [7], where PTP performs time stamping and Sync-E clock frequency synchronizes the clock of remote radio units (RUs) to the distributed unit (DU) at a central office or data centre. However, low frequency wander (clock sampling position noise of frequency <10 Hz) of jitter attenuators required in Sync-E limits the clock phase synchronization precision and correspondingly the time synchronization precision to  $\pm 10$ ns, which limits the achievable positioning error to  $\pm 3$  metres [7]. White Rabbit, which does achieve picosecond precision clock synchronization, uses only a 1 Gb/s data transmission rate and is not compatible with time division multiplexed RANs (TDM-RANs), due to random clock phase jumps between packets originating from different TDM optical sources [8].

A new approach to clock synchronization in RANs is required that enables picosecond precision while also being compatible with ≥25 Gb/s data rates, TDM-RANs and commercially available transceivers. In this paper, we demonstrate a picosecond-precision RAN clock phase synchronization approach with 37.6-km field-deployed dark fiber in the UK National Dark Fibre Facility (NDFF). In our approach, we distribute an optical clock to remove the need for a jitter attenuator, removing the 10-ns low-frequency wander inherent to Sync-E, reducing the primary limiter of clock synchronization precision to be from the change in fiber delay (e.g. from environmental temperature fluctuation). To compensate for the fibre delay change, we combine optical clock synchronization with clock phase caching, operating on off-the-shelf commercial electronic transceivers (which we previously explored to enable <625 ps clock and data recovery (CDR) time in data center optical switches [9,10]). We demonstrate picosecond clock phase synchronization precision, while simultaneously demonstrating sub-nanosecond CDR locking time for TDM-RANs. Our approach also provides fiber delay data that could be used for fiber sensing applications [11,12].

# 2. Operational principle

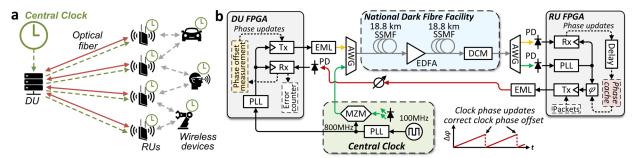

In our approach, as illustrated in Fig. 1a, all RUs are clock frequency synchronized by an optical clock distributed from the DU, instead of distributing data-embedded clocks (e.g. in Sync-E) from a DU to its connected RUs. Our approach directly frequency synchronizes the RUs using an optical clock, removing the requirement to clean the clock with a jitter attenuator, avoiding introducing clock wander. The main limiter of synchronization precision is then the variation in the optical fiber delay (e.g. from temperature variation). In standard single-mode optical fiber (SSMF), the thermal delay coefficient is ≈40 ps/(km·°C) [13]. This causes large fiber delay changes: e.g. a 20 km optical fiber subjected to a 10 °C temperature change experiences an 8 ns change in delay. This change in fiber delay must be compensated to enable picosecond clock synchronization precision, which we achieve using clock phase caching [9,10]. In this demonstration, a clock phase value is stored at the DU corresponding to each RU that the DU communicates with. Each RU has a clock phase interpolator (PI) that shifts the clock phase of outgoing packets sent to the DU. When the DU receives a packet from an RU, the phase offset of the incoming packet is measured and sent back to the RU. The RU then corrects the clock phase offset of outgoing packets to compensate for clock phase drift since the last clock phase update. This process is repeated at the phase update rate to maintain synchronization.

Fig. 1: a) Clock synchronized radio access network concept; DU, distributed unit; RU, radio unit, b) Optical clock synchronized, clock phase cached RAN experiment. Tx, transmitter; Rx, receiver; EML, externally modulated laser; MZM, Mach-Zehnder modulator; PLL, phase locked loop;  $\varphi$ , phase interpolator; AWG, arrayed waveguide grating; PD, photodiode, DCM, dispersion compensation module;  $\Delta \varphi$ , clock phase offset.

#### 3. Methodology

As shown in Fig. 1b, an RU and a DU, emulated on Xilinx VCU118 field programmable gate arrays (FPGAs), were clock frequency synchronized from a 100-MHz reference oscillator multiplied to 800 MHz using a phase locked loop (PLL). The DU was frequency synchronized electronically from the 800 MHz clock via an FPGA-integrated PLL. To generate a clock to frequency synchronize the RU, the 800-MHz square wave output of the PLL modulated a 1552.53 nm continuous wave (CW) optical carrier with a Mach-Zehnder Modulator (MZM) biased at quadrature. To send clock phase updates from the DU to the RU, 25.6 Gb/s non-return-to-zero on-off-keyed (NRZ-OOK) 60-ns data packets separated by 5 ns gaps modulated a 1550.92 nm CW with an electro absorption modulator (EAM). The optical clock and data signals were then frequency division multiplexed by a 200-GHz-spacing arrayed waveguide grating (AWG). The AWG output then entered the field-deployed dark fiber at our National Dark Fiber Network (NDFF) terminal. After propagating through 18.8-km dark SSMF, the clock and data signals were amplified by 21 dB at an NDFF interconnection point by an erbium doped fiber amplifier (EDFA). The output of the EDFA then propagated back to our NDFF terminal through a different 18.8 km of dark SSFM. The signals then passed through a dispersion compensation module (DCM) (-672 ps/nm) in the NDFF fiber link and followed by demultiplexing using a 200-GHzspacing AWG. The received optical clock power was reduced to -10.2 dBm and the data power reduced to -10.5 dBm with variable optical attenuators (VOAs) before reception by 17-GHz PIN photodiodes with transimpedance amplifiers (TIAs). The clock passed via an FPGA-integrated PLL to frequency synchronize the RU.

The RU FPGA stores a clock phase value, which was updated by average clock phase offset measurements made at a 500 Hz rate at the DU and sent through the DU to RU link. Each DU-performed phase measurement used the DU receiver phase interpolator (PI)-based clock and data recovery circuit (CDR) to find the mean clock phase of 2<sup>8</sup> data packets. The RU used a PI with these phase values to shift the clock phase of RU-transmitted packets to target arrival of packets at the DU with a 0-symbol clock phase offset. The RU transmitted real-time clock phase shifted 25.6-Gb/s NRZ-OOK data packets, modulated onto a 1554.14 nm carrier with an EAM. These packets were optically transmitted back-to-back to the DU, followed by optical attenuation with a VOA to -11.1dBm to emulate fiber attenuation, before reception by a 17-GHz PIN with TIA. To measure clock synchronization precision and stability, CDR phase offset values were output at 400 MHz from the DU CDR with 0.61 ps resolution. The mean of every 2<sup>15</sup> clock phase values was calculated at 12 kHz, then output to FPGA external memory. We interpolated the clock phase updates and applied them to the CDR clock phase offsets to find the clock phase offset variation with only optical clock synchronization.

To measure data transmission performance, the DU measured BER and CDR locking time for incoming data packets in real time, with CDR locking time defined as the time since the start of packets at which BER fell to <10<sup>-10</sup>. To emulate DU CDR locking in a TDM-RAN, the DU CDR was reset to 0 symbols between each successive data packet to force the DU CDR to reacquire the optimal clock phase for each successive data packet. The combination of back-to-back RU to DU transmission with 37.6 km DU to RU transmission was chosen as bidirectional transmission within a single fiber is not possible using NDFF due to the unidirectionality of the NDFF optical switches. Our topology emulates the clock phase change that would occur in a system with 18.8 km optical fiber in each direction between the DU and RU (i.e. 37.6 km of fiber contributes to the overall clock phase change at the DU).

## 4. Results and Discussion

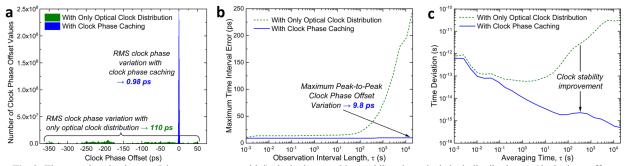

In Fig. 2a, we show the histogram of clock phase offset values output from the DU over 24.5 hours, with i) clock phase caching and optical clock distribution to phase and frequency synchronize the RU, and ii) with only frequency synchronization of the RU using optical clock distribution. By calculating the root-mean-square (RMS) clock phase offset from Fig. 2a, we calculate the precision of our clock phase caching approach to be 0.98 ps, a 100× improvement

vs our measured 110 ps RMS precision for only optical clock distribution and a 4 orders of magnitude improvement on Sync-E. In Fig. 2b, we show the maximum time interval error (MTIE), a metric quantifying peak-to-peak clock phase error against observation window length [14], which was bounded by our clock phase caching approach to be a maximum of 9.8 ps over  $2 \times 10^4$  s. Fig. 2c shows time deviation (TDEV) [14], a metric quantifying clock phase stability against averaging time, comparing the reference clock input of the DU with the embedded clock in the data received by the DU from the RU. The data-embedded clock from the RU is subjected to clock phase shift from fibre delay variation in the 37.6 km NDFF SSMF link. Fig. 2a-c together show that our approach of combining optical clock synchronization and clock phase caching compensates for the clock phase instability caused by fiber delay variation.

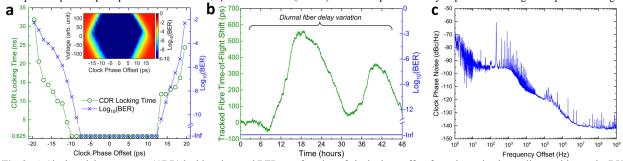

In Fig. 3a, we show the BER and CDR locking time degradation of data received at the DU that occurs from significant clock phase offsets between the DU and RU clocks. Fig. 3b then shows the 48-hour long-term stability of our approach. The precision of our approach constrains the clock phase of data packets arriving at the DU to the error-free, <625ps CDR locking time area of Fig. 3a. Our approach could be used to enable <625 ps locking time in TDM-RANs by constraining the clock phase of packets from multiple RUs to this area. With clock phase caching running, we measured no errors (BER  $<3.7\times10^{-16}$ , CDR locking time <625ps) and show the fiber delay change, calculated from the clock phase updates. Lastly, Fig. 3c shows the 800 MHz optical clock phase noise after 37.6 km dark fiber.

Fig. 2: Time synchronization precision measurement with i) clock phase caching and ii) only optical clock distribution a) Clock phase offset histogram, showing 0.98-ps RMS synchronization precision with clock phase caching, b) Maximum time interval error (MTIE) with 9.8 ps max. peak-to-peak phase offset variation, c) Time deviation (TDEV) with clock phase stability improvement using clock phase caching.

Fig. 3: a) Clock and data recovery (CDR) locking time and BER as a function of clock phase offset from the optimal sampling position at the DU receiver (inset: BER vs clock phase offset and voltage with clock phase caching running), b) Long-term 48-hour tracked fiber phase change with error-free data transmission, c) Clock phase noise of the 800 MHz optical clock after transmission through 37.6 km of dark fiber in NDFF.

#### 3. Conclusion

We combine optical clock frequency distribution and clock phase caching to achieve 0.98-ps RMS precision clock synchronization for RANs, 4 orders of magnitude better than the 10-ns precision of Sync-E and 100× better than using only optical clock frequency synchronization. Our clock synchronization approach uses off-the-shelf commercial transceivers, is compatible with TDM-RANs and can enable sub-625-ps CDR locking time for TDM applications.

Acknowledgements We thank the Royal Academy of Engineering, UKRI NTC and EPSRC EP/R035342/1 for funding this research.

### References

- [1] M. Harders et al., IEEE Trans. Vis. Comput. Graphics 15, 138-149 (2008). [2] D. Sam et al., Vehicular Comms. 6, 17-28 (2016).

- [3] L. Xingxing et al., J. Geodesy, 89, 607-635 (2015). [4] C. Ma et al., Pro

- [4] C. Ma et al., Proc. ION GPS 2001, 882-893 (2021).

- [5] Telecoms Diversification Taskforce: findings and report, UK Gov. (2021). [6] 1588-2019 Standard, IEEE (2020).

- [7] G.8262 Standard, ITU-T (2019).

[8] P. Moreira et al., Proc. ISPCS 2009, 1-5 (2009).

[9] K. Clark et al., Nat. Electron. 3, 426-433 (2020).

[10] K. Clark, PhD Thesis, UCL (2021).

[11] G. Marra et al., Science 376, 874-879 (2022).

[12] G.A. Wellbrock et al., Proc. OFC 2021, 1-3 (2021).

[13] R. Slavík et al., Sci. Rep. 5, 15447 (2015).

[14] W.J. Riley, Handbook of Frequency Stability Analysis (2008).