# A 3.2mW SAR-assisted CT D ADC with 77.5dB SNDR and 40MHz BW in 28nm CMOS

Cenci, P.; Bolatkale, M.; Rutten, R.; Ganzerli, M.; Lassche, G.; Makinwa, K.; Breems, Lucien

DOI 10.23919/VLSIC.2019.8778176

**Publication date** 2019 **Document Version** Final published version

Published in 2019 Symposium on VLSI Circuits

## Citation (APA)

Cenci, P., Bolatkale, M., Rutten, R., Ganzerli, M., Lassche, G., Makinwa, K., & Breems, L. (2019). A 3.2mW SAR-assisted CTΔΣ ADC with 77.5dB SNDR and 40MHz BW in 28nm CMOS. In *2019 Symposium on VLSI Circuits: Digest of technical papers* (pp. C230-C231). Article 8778176 IEEE. https://doi.org/10.23919/VLSIC.2019.8778176

## Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Takedown policy Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# Green Open Access added to TU Delft Institutional Repository

# 'You share, we take care!' - Taverne project

https://www.openaccess.nl/en/you-share-we-take-care

Otherwise as indicated in the copyright section: the publisher is the copyright holder of this work and the author uses the Dutch legislation to make this work public.

## A 3.2mW SAR-assisted CTΔΣ ADC with 77.5dB SNDR and 40MHz BW in 28nm CMOS

P. Cenci<sup>1</sup>, M. Bolatkale<sup>1,2</sup>, R. Rutten<sup>2</sup>, M. Ganzerli<sup>2</sup>, G. Lassche<sup>3</sup>, K. Makinwa<sup>1</sup>, L. Breems<sup>2</sup>

<sup>1</sup>Delft University of Technology, Delft, the Netherlands, <sup>2</sup>NXP Semiconductors, Eindhoven, the Netherlands,

<sup>3</sup>Catena Microelectronics, Delft, the Netherlands

## Abstract

This paper presents a SAR-assisted Continuous-time Delta-Sigma (CT $\Delta\Sigma$ ) ADC, which combines the energy efficiency of SAR ADCs with the relaxed driving requirements of CT $\Delta\Sigma$  ADCs, as well as similar anti-alias filtering. When clocked at 2.4GHz, the ADC achieves 77.5dB SNDR in 40MHz BW. It consumes 3.2mW, resulting in a state-of-the-art Walden FoM of 6.5fJ/cs and a Schreier FOM of 178.5dB.

## Introduction

Multi-standard receivers for BLE and WIFI require energy efficient (<10fJ/cs) ADCs with > 40MHz BW, and > 70dB DR to maintain linearity in the presence of strong blockers. Although a SAR-assisted pipeline ADC can convert such BWs with excellent energy efficiency [1], a power-hungry anti-alias filter (AAF) is then required to drive its 4pF sampling capacitors with sufficient linearity [1]. Moreover, to relax the AAF requirements, oversampling is often used at the expense of higher power dissipation. In comparison, CT $\Delta\Sigma$  ADCs have relaxed driving requirements and inherent anti-alias filtering, but are less energy efficient [2-3]. This paper presents an ADC that combines the best of both worlds. It achieves 77.5dB SNDR in a 40MHz BW, >40dB anti-alias filtering, consumes 3.2mW, and has an input capacitance of only 21fF.

## SAR-Assisted CT $\Delta\Sigma$ ADC Architecture

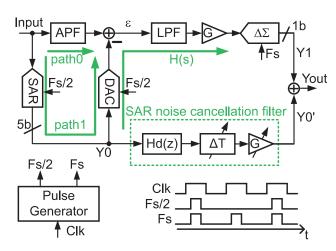

Fig. 1 shows the block diagram of the SAR-assisted CT $\Delta\Sigma$  ADC. The first stage is built around a coarse 5b-SAR ADC. A 5b-DAC converts its digital output (Y0) to the analog domain, where it is subtracted from a delayed version of the input signal to generate a residue ( $\epsilon$ ). An all-pass filter (APF) implements the delay, which is designed to match the 1.5\*T<sub>CLK</sub> latency of the 5b SAR-DAC path [4]. The residue (SAR ADC quantization noise, non-linearity and sampling images) is then filtered (LPF), amplified (inter-stage gain G), and digitized by a CT $\Delta\Sigma$  ADC. The final output (Yout) is obtained by combining Y1 and Y0 in a digital compensation filter Hd(z). This models the combined transfer function H(s) of LPF, G and the signal transfer function (STF) of the  $\Delta\Sigma$  ADC. After summing Y1 and Y0', aliasing components and SAR ADC related errors are cancelled.

Any mismatch between H(s) and Hd(z) will allow some of the residue to "leak" into Yout. To minimize this, Hd(z) can be trimmed via a digitally-programmable delay ( $\Delta T$ ) and gain (G). This suppresses the residue by > 42dB, pushing it below the overall ADC's thermal-noise floor. To minimize first stage latency (path1), the SAR ADC employs a non-interleaved architecture and processes 1b per conv.-cycle to avoid the extra delay incurred by look-up tables or decoders. By clocking the SAR ADC at half the sampling rate (fs) of the  $\Delta\Sigma$  ADC, overall ADC's rail-to-rail capability maximizes the overall ADC's input dynamic range [5], while the use of half-LSB dither mitigates its tonal behavior.

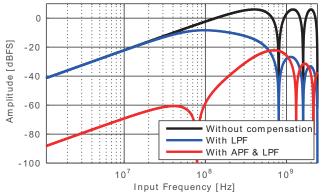

The inter-stage gain (G) reduces the  $\Delta\Sigma$  ADC's input-referred noise contribution. To minimize overall ADC power, G should be greater than ~7.5V/V. However, if G is too high, the  $\Delta\Sigma$ modulator will become unstable in the presence of full-scale (FS) out-of-band blockers. The frequency response from the input of the ADC to the input of G is shown in Fig. 2, assuming an ideal SAR ADC. Depending on their relative phases, the outputs of the APF (path0) and the SAR-DAC (path1) will either cancel or complement each other, resulting in either a frequency response notch or a 6dB peak. The latter is attenuated by the LPF ( $f_{3dB} \sim 65$ MHz), making the system robust to out-of-band blockers. To match the SAR ADC delay, the APF adds two 338MHz RHP zeros and one 338MHz pole. The APF/LPF combination ensures that the  $\Delta\Sigma$ M remains stable for G <11V/V, even for a worst-case FS 700MHz blocker. The aliased residue components caused by higher frequency (> 800MHz) blockers, can then be suppressed by incorporating a simple 1<sup>st</sup> order LPF (70MHz) into a preceding stage.

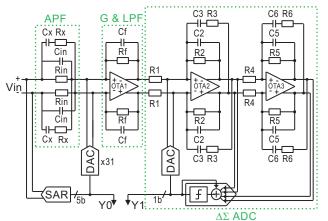

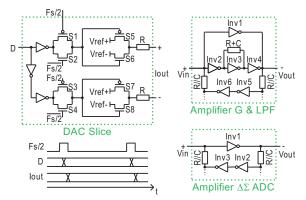

Fig. 3 shows a detailed block diagram of the ADC. A single amplifier realizes the APF, LPF and the inter-stage gain. Its input RC network defines the APF, while its RC feedback network defines the LPF and the inter-stage gain. An inverter-based amplifier is used for low power and low noise (Fig. 4). Since it only processes the SAR ADCs errors, its linearity requirements are relaxed. The 5b-DAC employs resistors, which sink/source current from the supply (0.9V) and ground. It consists of 31 slices (Fig. 4) directly connected to the output of the SAR through 5 D-FFs. The data (Y0) is available at the start of the SAR's sampling phase (SP). During SP, the switches (S1-S4) are open, ensuring that the DAC settles by the end of SP without introducing further delay in path1. The SAR ADC, DAC and  $\Delta \Sigma M$  are driven by 100ps pulses derived by a pulse generator from an external 2.4GHz clock. As a result, the ADC's operation is robust to PVT and duty-cycle variation.

The  $\Delta\Sigma M$  (Fig. 3) consists of a 4<sup>th</sup>-order feed-forward (FF) loop filter, a 1-bit quantizer and a R-DAC (Fig. 4). To reduce its power dissipation, the loop filter consists of two single-opamp biquad stages, whose coefficients have been optimized for the low gain (<25dB) inverter-based amplifiers (Fig. 4). The FF and ELD coefficients are implemented by splitting the input pair of a StrongArm comparator [5]. The comparator is triggered at the end of the SAR sampling phase (SP). When its output becomes valid, a decision detector starts the reset phase and updates the ELD signal through a D-FF. The data for the  $\Delta\Sigma M$ 's DAC, like that of the 5-bit DAC, is then also available during SP.

## **Measurement Results**

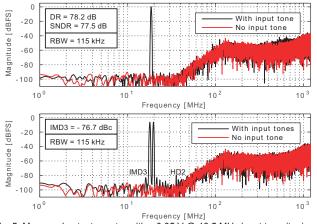

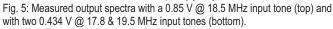

The ADC occupies  $0.025 \text{mm}^2$  in 28nm CMOS (Fig. 6) and dissipates 3.2mW from a 0.9V supply (708µW SAR, 777µW DAC, 585µW Amplifier, 697µW  $\Delta\Sigma$ M, 414µW pulse gen.). To compensate for PVT variation, the supply voltage of the amplifiers and the capacitors used in the  $\Delta\Sigma$ M/APF/LPF (5-bit arrays) are calibrated at start-up. As in [7], Hd(z) is foreground-calibrated by adjusting its delay and gain in ~20ps (2.4%\*T<sub>CLK</sub>) and ~0.4% steps, respectively. Fig. 5 (top) shows the measured spectra with and without a -0.13dBFS 18.5MHz input tone. Fig. 5 (bottom) shows the measured spectra with two -6.2dBFS 17.8 MHz and 19.6MHz tones. The ADC then exhibits a peak SNDR of 77.5 dB at -0.13dBFS and an IM<sub>3</sub> of -76.7dBc. Fig. 6 shows the measured SNDR versus input amplitude, which corresponds

to a DR of 78.2dB. Table I summarizes the ADC's performance and compares them to the state of the art. Although its energy efficiency is similar to that of a state-of-the-art SAR ADC [1], its CT implementation ensures easier drivability and superior antialias filtering, similar to that of CT $\Delta\Sigma$  ADCs.

### References

[1] Y. Lim et al., VLSI 2017 [2] S. Loeda et al., JSSC 2016

[3] Y. S. Shu et al., ISSCC 2013 [4] H. Shibata et al., JSSC 2017

[5] P. Cenci et al., ESSCIRC, 2017 [6] Y. Dong et al., JSSC 2014

[7] R. Rutten et al, ESSCIRC, 2006.

Fig. 1: Block diagram of the SAR-Assisted CT $\Delta\Sigma$  ADC with timing diagram.

Fig. 2: Frequency response from the input of the ADC to the input of the gain stage with full scale (0.9V) input signal and ideal SAR ADC @ 1.2GS/s.

Fig. 3: Schematic of the SAR-Assisted CT $\Delta\Sigma$  ADC with APF delay compensation, G&LPF stage, and 4<sup>th</sup> order  $\Delta\Sigma$ M with feed-forward and ELD coefficients integrated in the quantizer.

Fig. 4: Schematic of the R-DAC with timing diagram(left). Half-circuit schematic of the amplifiers (G&LPF on top-right,  $\Delta\Sigma$  on bottom-right).

Fig. 6: Measured SNDR vs. Input amplitude (Left). Micrograph of the SAR-Assisted CT $\Delta\Sigma$  ADC in 28 nm CMOS (Right).

| Table I. Comparis | on with state-of- | the-art ADCs with | n similar BW | and resolution. |

|-------------------|-------------------|-------------------|--------------|-----------------|

|                   |                   |                   |              |                 |

|                              | This work                      | [1]          | [2]    | [3]   | [5]        | [6]         |

|------------------------------|--------------------------------|--------------|--------|-------|------------|-------------|

| ADC Architecture             | SAR-Assisted CT $\Delta\Sigma$ | SAR-Assisted | CΤΔΣ   | CΤΔΣ  | 0-3 MASH   | CT pipeline |

| Technology [nm]              | 28                             | 40           | 40     | 28    | 28         | 28          |

| Active Area [mm2]            | 0.025                          | 0.068        | 0.0194 | 0.08  | 0.9        | 5.1         |

| Supply Voltage [V]           | 0.9                            | 1.1          | -      | -     | 0.9/1.8/-1 | -           |

| Sampling Rate [GHz]          | 2.4                            | 0.1          | 2.4    | 0.64  | 3.2        | 9           |

| Power [mW]                   | 3.2                            | 2.3          | 5.25   | 3.9   | 235        | 2330        |

| OSR                          | 30                             | 1            | 30     | 17.7  | 30         | 4           |

| Bandwidth [MHz]              | 40                             | 50           | 40     | 18    | 53.3       | 1125        |

| Sampling Cap. [fF]           | 21                             | 4000         | -      | -     | -          | -           |

| Anti-aliasing filtering [dB] | 42                             | Х            | -      | -     | -          | -           |

| DR [dB]                      | 78.2                           | -            | 67.8   | 78.1  | 88         | 73          |

| SNR [dB]                     | -                              | 73.3         | -      | -     | 83.1       | 64          |

| SNDR [dB]                    | 77.5                           | 73.2         | 66.9   | 73.6  | 71.4       | 63          |

| ENOB [bits]                  | 12.58                          | 11.9         | 10.8   | 11.9  | 11.6       | 10.17       |

| FOMS [dB]                    | 178.5                          | 176.6        | 162.7  | 170.2 | 155.5      | 153.3       |