Abstract

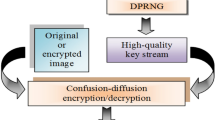

Aiming at the problems of small key space and low anti deciphering strength of one-dimensional single chaotic image encryption algorithm, an improved encryption algorithm based on LDPC code and double Logistic chaotic system is proposed, which can expand the key space and enhance the security and anti-interference ability of the system. The digital image encryption test system based on FPGA and Nios II soft core is designed, including the overall design of hardware/software, Nios II soft core design, VGA module design, etc. The algorithm is applied to practice, and the test results are shown by VGA to verify the feasibility, reliability, and practicability of the algorithm.

Similar content being viewed by others

REFERENCES

Muthu, J.S. and Murali, P., Comment on “An image encryption algorithm based on modified logistic chaotic map,” Optik, 2019, vol. 207, p. 163843. https://doi.org/10.1016/j.ijleo.2019.163843

Sha, K. and Wang, Z., Research on image encryption algorithm based on chaos, Electroacoustic Technol., 2019, vol. 43, no. 1, pp. 64–67.

Marrocco, C. and Tortorella, F., Exploiting coding theory for classification: An LDPC-based strategy for multiclass-to-binary decomposition, Inf. Sci.,2016, vol. 357, pp. 88–107. https://doi.org/10.1016/j.ins.2016.02.039

Sha, H., Wang, Z., Wei, L., Zhankai, B., and Fei, X., Image encryption based on LDPC code and chaos, Electron. Des. Eng., 2020, vol. 28, no. 3, pp. 178–182.

Kabakulak, B., Caner Taşkın, Z., and Pusane, A.E., Optimization-based decoding algorithms for LDPC convolutional codes in communication systems, IISE Trans., 2019, vol. 51, no. 10, pp. 1061–1074. https://doi.org/10.1080/24725854.2018.1550692

Mackay, D.J.C., Wilson, S.T., and Davey, M.C., Comparison of constructions of irregular Gallager codes, IEEE Trans. Commun., 1999, vol. 47, no. 10, pp. 1449–1454. https://doi.org/10.1109/26.795809

Gallager R. G., Low-Density Parity Check Codes, Cambridge, Mass.: MIT Press, 1963.

Elgendy, F., Sarhan, A.M., Eltobely, T.E., El-Zoghdy, S.F., El-Sayed, H.S., and Faragallah, O.S., Chaos-based model for encryption and decryption of digital images, Multimedia Tools Appl., 2016, vol. 75, no. 18, pp. 11529–11553. https://doi.org/10.1007/s11042-015-2883-z

Chen, S. and Tang, Y., RGB color image three reset chaos algorithm based on chaos system, J. Chongqing Univ. Posts Telecommun. (Nat. Sci. Ed.), 2018, vol. 30, no. 6, pp. 812–818.

Sułek, W., Non-binary LDPC decoders design for maximizing throughput of an FPGA implementation, Circuits, Syst., Signal Process., 2016, vol. 35, no. 11, pp. 4060–4080. https://doi.org/10.1007/s00034-015-0235-x

Gao, L. and Cheng, L., Research on integrated circuit design specialty and curriculum based on FPGA, J. Shenzhen Polytech., 2011, vol. 10, no. 5, pp. 38–40.

Cheng, K., Shen, Q., Liao, S., and Peng, C., Implementation of encoder and decoder for LDPC codes based on FPGA, J. Syst. Eng. Electron., 2019, vol. 30, no. 4, pp. 642–650. https://doi.org/10.21629/JSEE.2019.04.02

Straus, P. and Kolka, Z., Simulation and implementation of LDPC code in FPGA, in 23rd Int. Conf. Radioelektronika (RADIOELEKTRONIKA), Pardubice, Czech Republic, 2013, IEEE, 2013, pp. 346–349. https://doi.org/10.1109/RadioElek.2013.6530944

Shen, Q., Technical research on NIOS-II soft core embedded in FPGA, PhD Thesis, Nanchang, Jiangxi: East China Univ. of Technology, 2015.

Ma, Y., Research on SOPC image processing system architecture based on Nios II and hardware accelerated core, PhD Thesis, Shanghai: Shanghai Ocean Univ., 2018.

Geng, J., Design and implementation of image encryption system based on FPGA, PhD Thesis, Nanchang, Jiangxi: Nanchang Univ., 2014.

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

The authors declare that they have no conflict of interest.

About this article

Cite this article

Zhong-xun Wang, Sha, Ky. & Gao, Xl. Digital Image Encryption Test System Based on FPGA and Nios II Soft Core. Aut. Control Comp. Sci. 55, 490–499 (2021). https://doi.org/10.3103/S0146411621050072

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.3103/S0146411621050072