Phạm Quốc Cường

1

1

## HYBRID INTERCONNECT DESIGN FOR HETEROGENEOUS HARDWARE ACCELERATORS

\_ I

\_ I

## HYBRID INTERCONNECT DESIGN FOR HETEROGENEOUS HARDWARE ACCELERATORS

## Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. ir. K. C. A. M. Luyben, voorzitter van het College voor Promoties, in het openbaar te verdedigen op dinsdag 14 April 2015 om 12:30 uur

door

#### **Cuong PHAM-QUOC**

Master of Engineering in Computer Science Ho Chi Minh City University of Technology - HCMUT, Vietnam geboren te Tien Giang, Vietnam. This dissertation has been approved by the

Promotor: Prof.dr. K.L.M Bertels Copromotor: Dr.ir. Z. Al-Ars

Composition of the doctoral committee:

| Rector Magnificus           | voorzitter                                     |  |

|-----------------------------|------------------------------------------------|--|

| Prof.dr. K.L.M Bertels      | Technische Universiteit Delft, promotor        |  |

| Dr.ir. Z. Al-Ars            | Technische Universiteit Delft, copromotor      |  |

|                             |                                                |  |

| Independent members:        |                                                |  |

| Prof.dr. E. Charbon         | Technische Universiteit Delft                  |  |

| Prof.dring. J. Becker       | Karlsruhe Institute of Technology              |  |

| Prof.dr. A.V. Dinh-Duc      | Vietnam National University - Ho Chi Minh City |  |

| Prof.dr. Luigi Carro        | Universidade Federal do Rio Grande do Sul      |  |

| Dr. F. Silla                | Universitat Politècnica de València            |  |

| Prof.dr.ir. AJ van der Veen | Technische Universiteit Delft, reservelid      |  |

*Keywords:* Hybrid interconnect, hardware accelerators, data communication, quantitative data usage, automated design.

Copyright © 2015 by Cuong Pham-Quoc

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without permission of the author.

ISBN 978-94-6186-448-2

Cover design: Cuong Pham-Quoc Printed in The Netherlands

To my wife and my son

۱\_\_

\_ I

\_ I

## ABSTRACT

Heterogeneous multicore systems are becoming increasingly important as the need for computation power grows, especially when we are entering into the big data era. As one of the main trends in heterogeneous multicore, hardware accelerator systems provide application specific hardware circuits and are thus more energy efficient and have higher performance than general purpose processors, while still providing a large degree of flexibility. However, system performance dose not scale when increasing the number of processing cores due to the communication overhead which increases greatly with the increasing number of cores. Although data communication is a primary anticipated bottleneck for system performance, the interconnect design for data communication among the accelerator kernels has not been well addressed in hardware accelerator systems. A simple bus or shared memory is usually used for data communication between the accelerator kernels. In this dissertation, we address the issue of interconnect design for heterogeneous hardware accelerator systems.

Evidently, there are dependencies among computations, since data produced by one kernel may be needed by another kernel. Data communication patterns can be specific for each application and could lead to different types of interconnect. In this dissertation, we use detailed data communication profiling to design an optimized hybrid interconnect that provides the most appropriate support for the communication pattern inside an application while keeping the hardware resource usage for the interconnect minimal. Firstly, we propose a heuristicbased approach that takes application data communication profiling into account to design a hardware accelerator system with a custom interconnect. A number of solutions are considered including crossbar-based shared local memory, direct memory access (DMA) supporting parallel processing, local buffers, and hardware duplication. This approach is mainly useful for embedded system where the hardware resources are limited. Secondly, we propose an automated hybrid interconnect design using data communication profiling to define an optimized interconnect for accelerator kernels of a generic hardware accelerator system. The hybrid interconnect consists of a network-on-chip (NoC),

shared local memory, or both. To minimize hardware resource usage for the hybrid interconnect, we also propose an adaptive mapping algorithm to connect the computing kernels and their local memories to the proposed hybrid interconnect. Thirdly, we propose a hardware accelerator architecture to support streaming image processing. In all presented approaches, we implement the approach using a number of benchmarks on relevant reconfigurable platforms to show their effectiveness. The experimental results show that our approaches not only improve system performance but also reduce overall energy consumption compared to the baseline systems.

## ACKNOWLEDGMENTS

It is not easy to write this last part of the dissertation, but this is an exciting period because it lets me take a careful look at the whole last four years, starting from 2011. First, I would like to thank the Vietnam International Education Development (VIED) for their funding. Without this funding, I would not have been in the Netherlands.

I would like to express special appreciation and thanks to my promoter, Prof. Dr. Koen Bertels, who had a difficult decision, but a successful one, when accepting me as his Ph.D. student in 2011. At that time, my spoken English was not very good but he tried very hard to understand our Skype-based discussion. During my time at the Computer Engineering Lab, he has introduced me to so many great ideas and has given me freedom to do my research. Koen, without you, I would have had no chance to write this dissertation. Another significant appreciation and thanks are given to my daily supervisor, but he always says that I am his friend, Dr.Ir. Zaid Al-Ars, who has guided me a lot not only in doing research but also in writing a paper. Zaid, I can never forget the many hours you have spent correcting my papers. Without you, I would have no publication and, of course, no dissertation. Besides these two great persons, I would like to say thank you to Veronique from Valorisation Center - TUDelft, Lidwina - CE secretary, and Eef and Erik - CE system administrators, for their support. I would like to thank my colleagues, Razvan, for your DWARV compiler and, Vlad, for the Molen platform upon which I have conducted the experiments. Thank you, Ernst, for your time translating my abstract and my proposition into Dutch.

I need to say thank you to Prof. Dr. Anh-Vu Dinh-Duc. This is the third time I have written his name in my thesis. The first and the second times were as my supervisor while this time is as a committee member. He has been there at many steps of my learning journey. I also appreciate all the committee members' time and the remarks they gave me.

Life is not only doing research. Without relaxing time and parties, we have no energy and no ideas. So, thank you to the ANCB group, a group of Vietnamese students, for the very enjoyable parties. Those parties and relaxing time helped me refresh my mind after the tiring working days. I am sure that I cannot say thank you to everybody who has supported me during the last four years because it would take a hundred pages, but I am also sure that I will never forget. Let me keep your kindness in my mind.

I am extremely grateful for my family and my wife's family, especially my father in law and my mother in law who have helped me to take care of my son when I could not be at home. Without you, I would not have had the peace of mind to do my work.

Last but most importantly, I would like to say thank you so much my wife and my son. You raise me up, and you make me stronger. Without your love and your support, I cannot do anything. Our family is going to reunite in the next couple of months after a long period of connecting together through a "hybrid interconnect" - a combination of video-calls, telephone calls, emails, social networks, and traveling.

> Phạm Quốc Cường Delft, April 2015

## **CONTENTS**

۱\_\_

| Ał | ostrac  |                                                        |   | vii |  |

|----|---------|--------------------------------------------------------|---|-----|--|

| Ac | knov    | edgments                                               |   | ix  |  |

| Li | st of ] | gures                                                  |   | xv  |  |

| Li | st of ' | ıbles                                                  |   | xix |  |

| 1  | Intr    | troduction                                             |   |     |  |

|    | 1.1     | Problem Overview                                       | • | 4   |  |

|    | 1.2     | Dissertation Challenges                                | • | 5   |  |

|    | 1.3     | Contributions                                          | • | 7   |  |

|    | 1.4     | Dissertation Organization                              | • | 8   |  |

| 2  | Bac     | ground and Related Work                                |   | 11  |  |

|    | 2.1     | On-chip Interconnect                                   | • | 11  |  |

|    | 2.2     | System-level Hybrid Interconnect                       | • | 17  |  |

|    |         | 2.2.1 Mixed topologies hybrid interconnect             | • | 17  |  |

|    |         | 2.2.2 Mixed architectures hybrid interconnect          | • | 22  |  |

|    | 2.3     | nterconnect in Hardware Accelerator Systems            | • | 27  |  |

|    | 2.4     | Data Communication Optimization Technique              | • | 30  |  |

|    |         | 2.4.1 Software level optimization                      | • | 30  |  |

|    |         | 2.4.2 Hardware level optimization                      | • | 30  |  |

| 3  | Con     | nunication Driven Hybrid Interconnect Design           |   | 33  |  |

|    | 3.1     | Overview Hybrid Interconnect Design                    |   | 33  |  |

|    |         | <b>3.1.1</b> Terminology                               |   | 34  |  |

|    |         | <b>3.1.2</b> Our approach                              |   | 34  |  |

|    | 3.2     | Data Communication Driven Quantitative Execution Model |   | 38  |  |

|    |         | 3.2.1 Baseline execution model                         | • | 38  |  |

|    |         | 3.2.2 Ideal execution model                            | • | 39  |  |

|    |         | <b>3.2.3</b> Parallelizing kernel processing           |   | 41  |  |

|   | 3.3                      | Sumn                                                                        | nary                                                                                                                                                                                           | 42                                                                                                         |  |  |

|---|--------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| 4 | Bus                      | s-based Interconnect with Extensions 45                                     |                                                                                                                                                                                                |                                                                                                            |  |  |

|   | 4.1                      | I Introduction                                                              |                                                                                                                                                                                                |                                                                                                            |  |  |

|   | 4.2                      | Relate                                                                      | ed Work                                                                                                                                                                                        | 46                                                                                                         |  |  |

|   |                          | 4.2.1                                                                       | Interconnect techniques                                                                                                                                                                        | 46                                                                                                         |  |  |

|   |                          | 4.2.2                                                                       | 5                                                                                                                                                                                              | 47                                                                                                         |  |  |

|   | 4.3                      | B Different Interconnect Solutions                                          |                                                                                                                                                                                                |                                                                                                            |  |  |

|   |                          | 4.3.1                                                                       | Assumptions and definitions                                                                                                                                                                    | 49                                                                                                         |  |  |

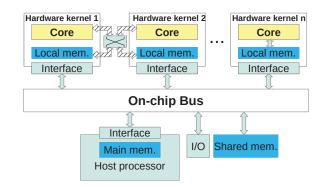

|   |                          | 4.3.2                                                                       | Bus-based interconnect                                                                                                                                                                         | 50                                                                                                         |  |  |

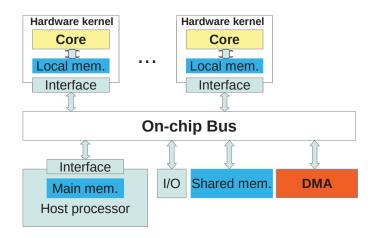

|   |                          | 4.3.3                                                                       | Bus-based with a consolidation of a DMA                                                                                                                                                        | 51                                                                                                         |  |  |

|   |                          | 4.3.4                                                                       | Bus-based with a consolidation of a crossbar                                                                                                                                                   | 52                                                                                                         |  |  |

|   |                          | 4.3.5                                                                       | Bus-based with both a DMA and a crossbar                                                                                                                                                       | 54                                                                                                         |  |  |

|   |                          | 4.3.6                                                                       | NoC-based interconnect                                                                                                                                                                         | 55                                                                                                         |  |  |

|   | 4.4                      | Exper                                                                       | iments                                                                                                                                                                                         | 56                                                                                                         |  |  |

|   |                          | 4.4.1                                                                       | Experimental setup                                                                                                                                                                             | 56                                                                                                         |  |  |

|   |                          | 4.4.2                                                                       | Experimental results                                                                                                                                                                           | 58                                                                                                         |  |  |

|   | 4.5                      | Discu                                                                       | ssion                                                                                                                                                                                          | 61                                                                                                         |  |  |

|   | 4.6                      | Sumn                                                                        | nary                                                                                                                                                                                           | 62                                                                                                         |  |  |

| 5 | Heu                      | ristic (                                                                    | Communication-aware Hardware Optimization                                                                                                                                                      | 63                                                                                                         |  |  |

|   | 5.1                      | Intro                                                                       | luction                                                                                                                                                                                        | 63                                                                                                         |  |  |

|   | 5.2                      | Custo                                                                       | m Interconnect and System Design                                                                                                                                                               | 65                                                                                                         |  |  |

|   |                          | 5.2.1                                                                       | Overview                                                                                                                                                                                       | 65                                                                                                         |  |  |

|   |                          |                                                                             |                                                                                                                                                                                                |                                                                                                            |  |  |

|   |                          | 5.2.2                                                                       | Different solutions                                                                                                                                                                            | 65                                                                                                         |  |  |

|   |                          |                                                                             | Different solutionsHeuristic-based algorithm                                                                                                                                                   |                                                                                                            |  |  |

|   | 5.3                      | 5.2.3                                                                       |                                                                                                                                                                                                | 70                                                                                                         |  |  |

|   | 5.3                      | 5.2.3                                                                       | Heuristic-based algorithm                                                                                                                                                                      | 70<br>71                                                                                                   |  |  |

|   | 5.3                      | 5.2.3<br>Exper                                                              | Heuristic-based algorithm                                                                                                                                                                      | 70<br>71<br>72                                                                                             |  |  |

|   | 5.3                      | 5.2.3<br>Exper<br>5.3.1                                                     | Heuristic-based algorithm                                                                                                                                                                      | 70<br>71<br>72<br>72                                                                                       |  |  |

|   | 5.3<br>5.4               | 5.2.3<br>Exper<br>5.3.1<br>5.3.2<br>5.3.3                                   | Heuristic-based algorithmimentsExperimental setupCase study                                                                                                                                    | 70<br>71<br>72<br>72<br>75                                                                                 |  |  |

| 6 | 5.4                      | 5.2.3<br>Exper<br>5.3.1<br>5.3.2<br>5.3.3<br>Summ                           | Heuristic-based algorithm                                                                                                                                                                      | 70<br>71<br>72<br>72<br>75                                                                                 |  |  |

| 6 | 5.4                      | 5.2.3<br>Exper<br>5.3.1<br>5.3.2<br>5.3.3<br>Summ                           | Heuristic-based algorithm                                                                                                                                                                      | 70<br>71<br>72<br>72<br>75<br>78                                                                           |  |  |

| 6 | 5.4<br>Auto              | 5.2.3<br>Exper<br>5.3.1<br>5.3.2<br>5.3.3<br>Summ<br>omate<br>Introd        | Heuristic-based algorithm                                                                                                                                                                      | 70<br>71<br>72<br>72<br>75<br>78<br><b>81</b>                                                              |  |  |

| 6 | 5.4<br><b>Aut</b><br>6.1 | 5.2.3<br>Exper<br>5.3.1<br>5.3.2<br>5.3.3<br>Summ<br>omate<br>Introd        | Heuristic-based algorithm   timents   Experimental setup   Case study   Experimental results   mary                                                                                            | 70<br>71<br>72<br>75<br>78<br><b>81</b>                                                                    |  |  |

| 6 | 5.4<br><b>Aut</b><br>6.1 | 5.2.3<br>Exper<br>5.3.1<br>5.3.2<br>5.3.3<br>Summ<br><b>omate</b><br>Introo | Heuristic-based algorithm   timents   Experimental setup   Case study   Case study   Experimental results   mary     d Hybrid Interconnect Design   duction   mated Hybrid Interconnect Design | <ul> <li>70</li> <li>71</li> <li>72</li> <li>72</li> <li>75</li> <li>78</li> <li>81</li> <li>82</li> </ul> |  |  |

\_ |

- <sub>1</sub>

|     | 6.3     | Experimental Results                                                | 91 |

|-----|---------|---------------------------------------------------------------------|----|

|     |         | 6.3.1 Embedded system results                                       | 91 |

|     |         | 6.3.2 High performance computing results                            | 95 |

|     |         | 6.3.3 Model comparison                                              | 00 |

|     | 6.4     | Summary                                                             | 03 |

| 7   | Acce    | elerator Architecture for Stream Processing 1                       | 05 |

|     | 7.1     | Introduction                                                        | 05 |

|     | 7.2     | Background and Related Work1                                        | 07 |

|     |         | 7.2.1 Streaming image processing with hardware acceleration 1       | 07 |

|     |         | 7.2.2 Canny edge detection algorithm                                | 08 |

|     | 7.3     | Architecture                                                        | 09 |

|     |         | 7.3.1 Hardware-software streaming model                             | 09 |

|     |         | 7.3.2 System architecture                                           | 11 |

|     |         | 7.3.3 Multiple clock domains                                        | 12 |

|     | 7.4     | Case Study: Canny Edge Detection                                    | 13 |

|     | 7.5     | $\mbox{Experimental Result} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 15 |

|     | 7.6     | Summary                                                             | 17 |

| 8   | Con     | clusions and Future Work 1                                          | 19 |

|     | 8.1     | Summary                                                             | 19 |

|     | 8.2     | Contributions                                                       | 21 |

|     | 8.3     | Future Work                                                         | 22 |

| Bi  | bliog   | raphy 1                                                             | 25 |

| Lis | st of I | Publications 1                                                      | 43 |

| Cu  | ırricı  | ılum Vitæ 1                                                         | 45 |

|\_\_\_

\_ I

\_ I

## **LIST OF FIGURES**

۱\_\_

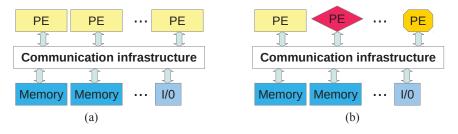

| 1.1 | (a) Homogeneous multicore; (b) Heterogeneous multicore                | 2  |

|-----|-----------------------------------------------------------------------|----|

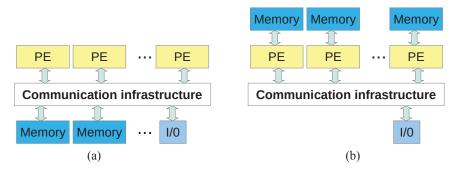

| 1.2 | (a) Shared memory; (b) Distributed memory                             | 3  |

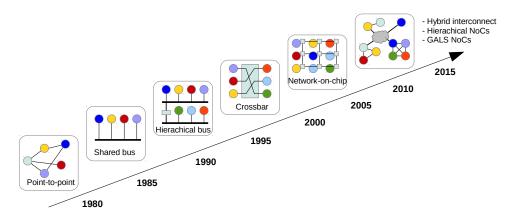

| 2.1 | The evolution of the on-chip interconnects                            | 12 |

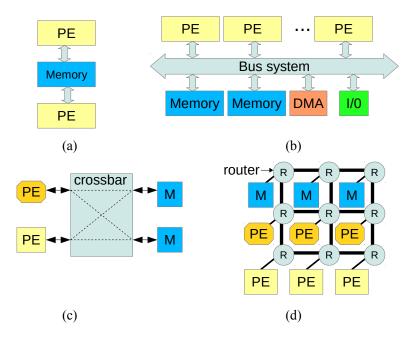

| 2.2 | (a) Directly shared local memory; (b) Bus; (c) Crossbar; (d) Network- |    |

|     | on-Chip                                                               | 15 |

| 2.3 | Interconnects comparison.                                             | 16 |

| 2.4 | Examples of NoC topologies: (a) 2D-mesh; (b) ring; (c) hypercube;     |    |

|     | (d) tree; and (e) star.                                               | 18 |

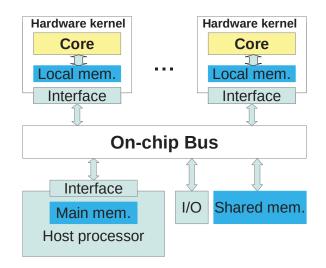

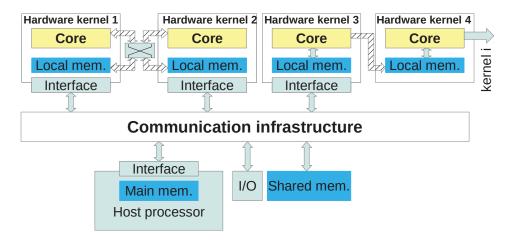

| 2.5 | A generic hardware accelerator architecture                           | 28 |

| 3.1 | (a) The generic FPGA-based accelerator architecture; (b) The generic  |    |

|     | FPGA-based accelerator system with our hybrid interconnect            | 34 |

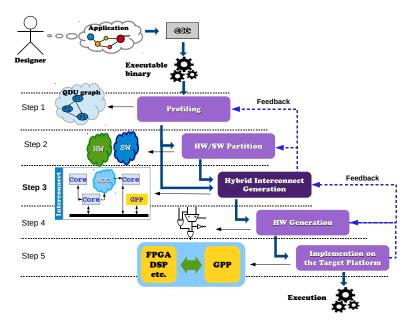

| 3.2 | Hybrid interconnect design steps                                      | 35 |

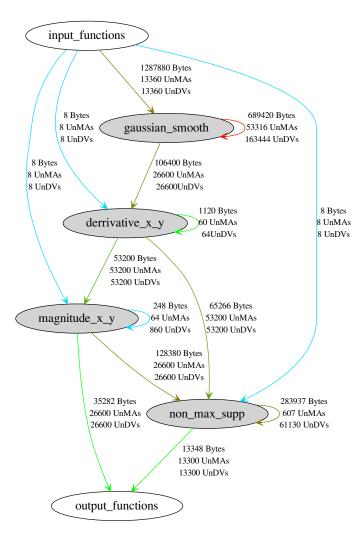

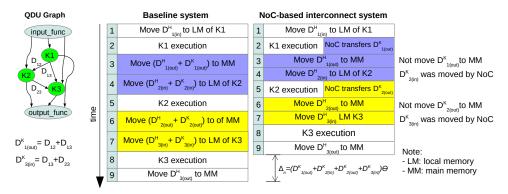

| 3.3 | Example of a QDU graph                                                | 37 |

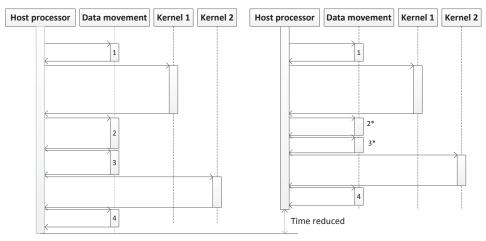

| 3.4 | The sequential diagrams for the baseline (left) and ideal execution   |    |

|     | model (right)                                                         | 40 |

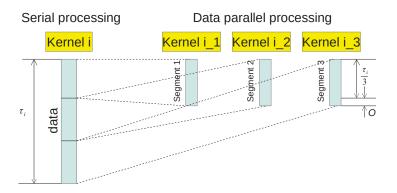

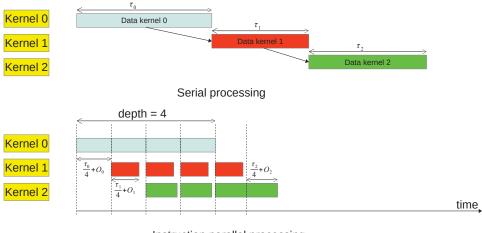

| 3.5 | An example of data parallelism processing compared to serial pro-     |    |

|     | cessing                                                               | 41 |

| 3.6 | An example of instruction parallelism processing compared to se-      |    |

|     | rial processing                                                       | 43 |

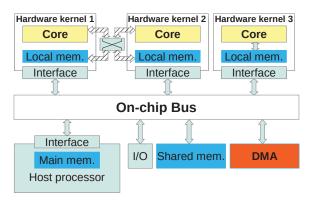

| 4.1 | The bus is used as interconnect                                       | 50 |

| 4.2 | The DMA is used as a consolidation to the bus                         | 52 |

| 4.3 | The crossbar is used as a consolidation to the bus                    | 53 |

| 4.4 | The DMA and the crossbar are used as consolidations to the bus        | 54 |

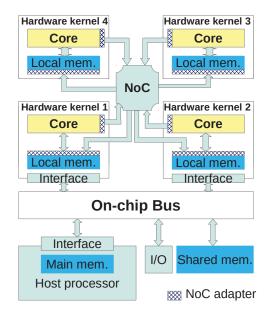

| 4.5 | The NoC is used as interconnect of the hardware accelerators          | 55 |

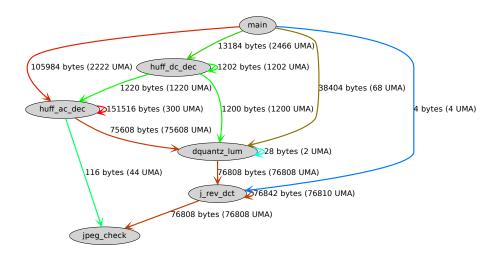

| 4.6 | The communication profiling graph generated by QUAD tool for          |    |

|     | the jpeg application                                                  | 57 |

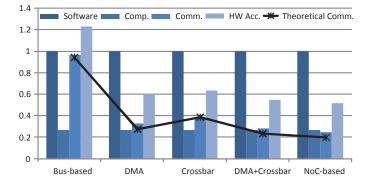

| 4.7 | Comparison between computation (Comp.), communication (Comm<br>hardware accelerator execution (HW Acc.), and theoretical com- | .), |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

|     | munication (Theoretical Comm.) times normalized to software time                                                              | 59  |

| 4.8 | Speed-up of hardware accelerators with respect to software and                                                                |     |

|     | bus-based model                                                                                                               | 60  |

| 4.9 | Comparison of resource utilization and energy consumption nor-                                                                |     |

|     | malized to bus-based model                                                                                                    | 60  |

| 5.1 | (a) $HW_1$ and $HW_2$ share their memories using a crossbar; (b) Struc-                                                       |     |

|     | ture of the crossbar for the Molen architecture                                                                               | 66  |

| 5.2 | Local buffer at $HW_2$                                                                                                        | 69  |

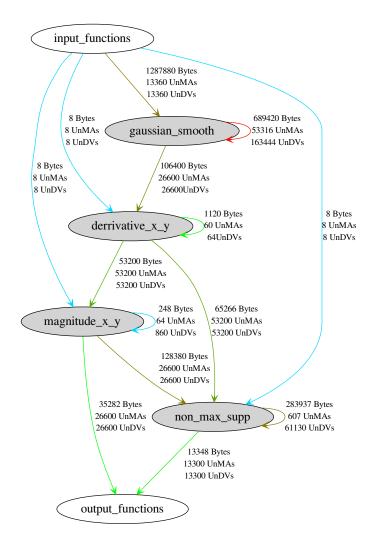

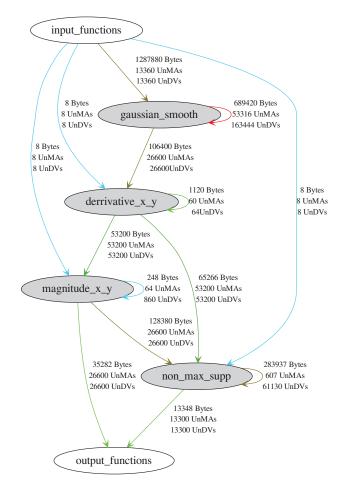

| 5.3 | QUAD graph for the Canny edge detection application                                                                           | 74  |

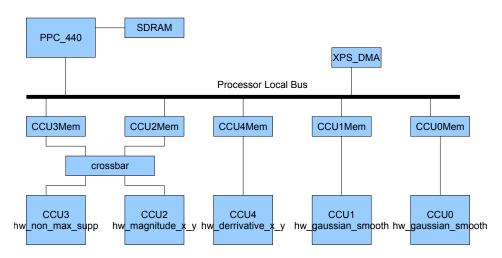

| 5.4 | Final system for Canny based on the Molen architecture and pro-                                                               |     |

|     | posed solutions                                                                                                               | 75  |

| 5.5 | Speed-up (w.r.t software) of hardware accelerators using Molen plat-                                                          |     |

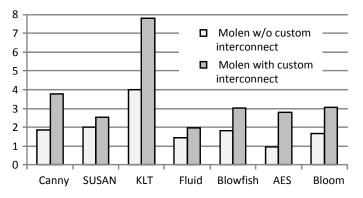

| 5.0 | form with and without using custom interconnect                                                                               | 77  |

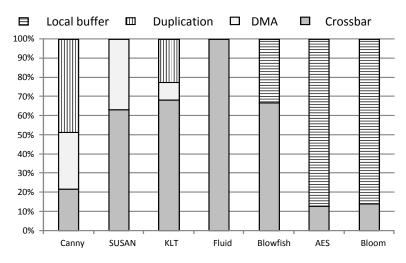

| 5.6 | The contribution of each solution to the speed-up                                                                             | 78  |

| 6.1 | Shared local memory with and without crossbar in a hardware ac-                                                               |     |

|     | celerator system.                                                                                                             | 84  |

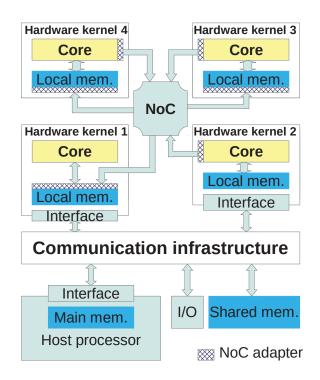

| 6.2 | The NoC is used as interconnect of the kernels in a hardware accel-                                                           |     |

|     | erator system.                                                                                                                | 85  |

| 6.3 | Illustrated NoC-based interconnect data communication for a hard-                                                             |     |

|     | ware accelerator system.                                                                                                      | 86  |

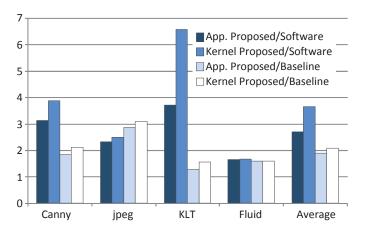

| 6.4 | The speed-up of the baseline system compared to the software                                                                  | 92  |

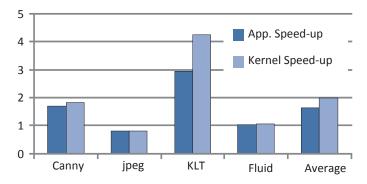

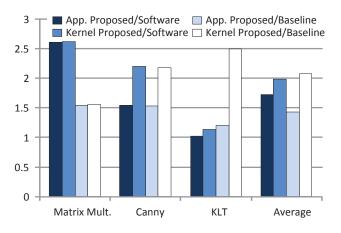

| 6.5 | The overall application and the kernels speed-up of the proposed                                                              |     |

|     | system compared to the software and baseline system                                                                           | 93  |

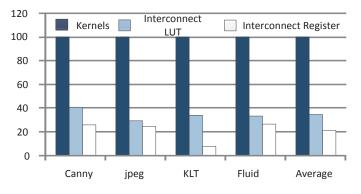

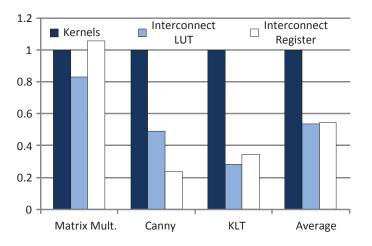

| 6.6 | Interconnect resource usage normalized to the resource usage for                                                              |     |

|     | the kernels                                                                                                                   | 94  |

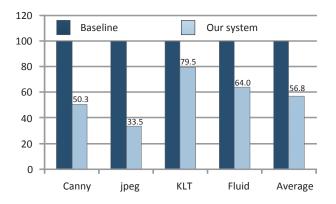

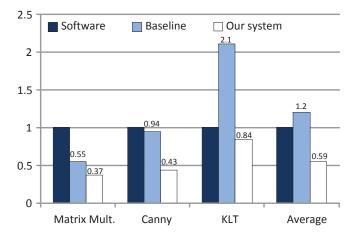

| 6.7 | Energy consumption comparison between the baseline system and                                                                 |     |

|     | the system using custom interconnect with NoC normalized to the                                                               | ~-  |

|     | baseline system.                                                                                                              | 95  |

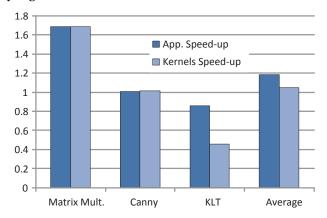

| 6.8 | The speed-up of the baseline high performance computing system                                                                | 0.0 |

| 0.0 | w.r.t software.                                                                                                               | 96  |

| 6.9 | The overall application and the kernels speed-up of the proposed                                                              | 07  |

|     | system compared to the software and baseline system                                                                           | 97  |

\_ |

- <sub>1</sub>

| 6.10 | Interconnect resource usage normalized to the resource usage for             |     |

|------|------------------------------------------------------------------------------|-----|

|      | the kernels                                                                  | 99  |

| 6.11 | Energy consumption comparison between the baseline system and                |     |

|      | the system using custom interconnect with NoC normalized to the              |     |

|      | host processor energy consumption                                            | 99  |

| 6.12 | QDU graph for the canny application on the embedded platform.                | 101 |

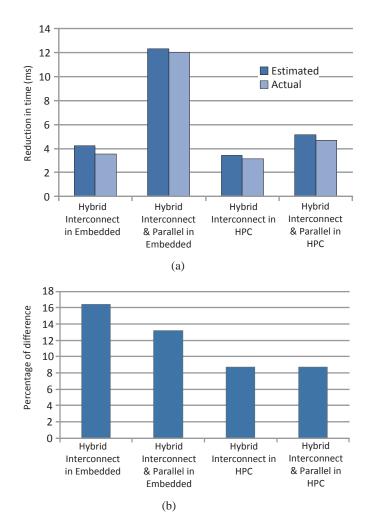

| 6.13 | The Comparison between estimated reduction in time and actual                |     |

|      | reduction time (a) in millisecond; (b) in percentage                         | 102 |

|      |                                                                              |     |

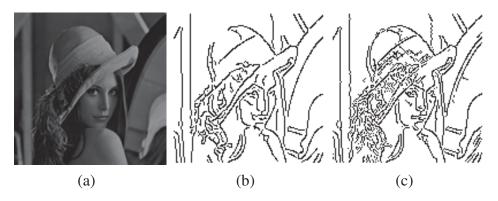

| 7.1  | (a) Original; (b) $6 \times 6$ filter matrix; (c) $3 \times 3$ filter matrix |     |

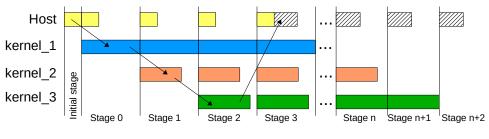

| 7.2  | The streaming model                                                          | 109 |

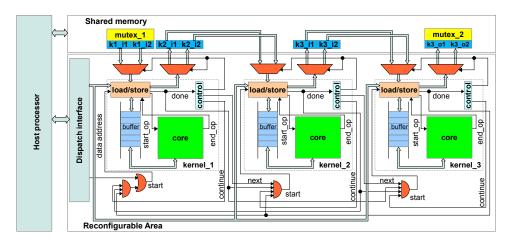

| 7.3  | The system architecture supporting pipeline for streaming applica-           |     |

|      | tions                                                                        | 111 |

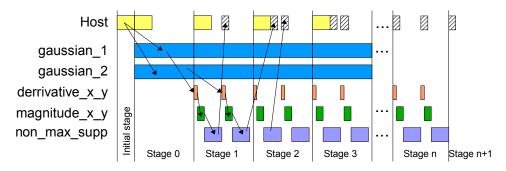

| 7.4  | The execution model and data dependency between kernels for the              |     |

|      | Canny algorithm                                                              | 114 |

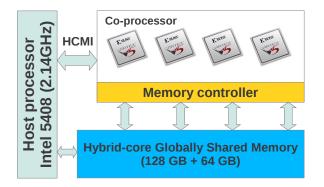

| 7.5  | The Convey hybrid computing system                                           | 114 |

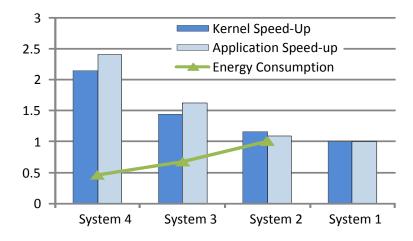

| 7.6  | The speed-up and energy consumption comparison between the                   |     |

|      | systems                                                                      | 116 |

|      |                                                                              |     |

| 8.1  | Interconnects comparison.                                                    | 121 |

۱\_\_\_

\_ I

\_ I

## **LIST OF TABLES**

۱\_\_

| 2.1 | Interconnect classifications overview                                                                   | 16  |

|-----|---------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Mixed topology hybrid interconnect summary                                                              | 23  |

| 2.3 | Mixed architecture hybrid interconnect summary                                                          | 27  |

| 4.1 | Hardware resource utilization (#LUTs/#Registers) for each intercon-                                     |     |

| 4.2 | nect component and the frequency                                                                        | 58  |

|     | ware accelerators                                                                                       | 59  |

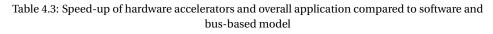

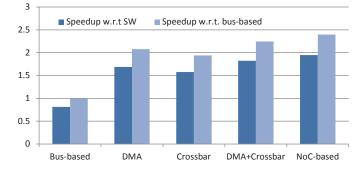

| 4.3 | Speed-up of hardware accelerators and overall application com-<br>pared to software and bus-based model | 60  |

| 4.4 | Hardware resource utilization (#LUTs/#Registers)                                                        | 60  |

| 5.1 | Resource usage and maximum frequency of hardware modules                                                | 75  |

| 5.2 | Execution times of accelerated functions and speed-up compared to software                              | 76  |

| 5.3 | Interconnect techniques and hardware resource usage of applica-                                         | 70  |

| 5.5 | tions                                                                                                   | 76  |

| 5.4 | Application and kernel speed-ups with and without the custom in-                                        |     |

|     | terconnect w.r.t. software                                                                              | 77  |

| 6.1 | Adaptive mapping function                                                                               | 90  |

| 6.2 | Speed-up of the proposed system compared to software and the baseline system                            | 92  |

| 6.3 | Hardware resource utilization comparison and the solution in the                                        | 02  |

|     | embedded system                                                                                         | 94  |

| 6.4 | High performance computing system results                                                               | 97  |

| 6.5 | Hardware resource utilization comparison and the solution in the                                        |     |

|     | high performance system                                                                                 | 98  |

| 7.1 | Application execution time and speed-up of different systems                                            | 116 |

| 7.2 | 7.2 The resource usage for each kernel and the whole streaming system |     |  |  |

|-----|-----------------------------------------------------------------------|-----|--|--|

|     | with multiple clock domains                                           | 117 |  |  |

| 7.3 | Power consumption (W) and resource usage of the systems               | 118 |  |  |

\_ |

-I

# L

## INTRODUCTION

W<sup>ITH</sup> the rapid development of technology, more and more transistors are integrated on a single chip. Today, it is possible to integrate more than 20 billion transistors [Leibson, 2014] into one system (announced by Xilinx in May 2014). However, the more transistors are integrated into a system; the more challenges need to be addressed such as power consumption, thermal emission and memory access bottleneck. Homogeneous and heterogeneous multicore systems were introduced to utilize such large numbers of transistor efficiently.

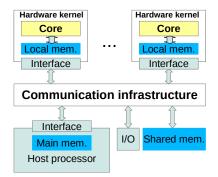

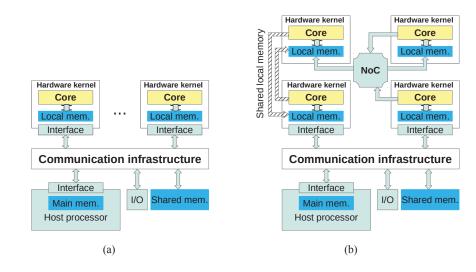

A generic multicore architecture can be seen as a multiprocessor system in which multiple processing elements (PEs) (also called computational cores) and a memory system are tightly connected together through a communication infrastructure (interconnect). Besides these three main components (PEs, memory system and communication infrastructure), a multicore architecture typically contains other components such as I/O, timer, etc.

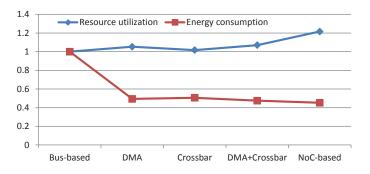

Processing elements: In a multicore system, PEs have various types ranging from general purpose processors to *Intellectual Property* (IP) cores. PEs may support either software tasks or hardware tasks. Software tasks can be performed in instruction set processors such as PowerPC, ARM, etc; while hardware tasks can be executed in hardware cores such as reconfigurable logic or dedicated IP cores. Based on the type of PEs, multicore architectures are classified into two classes called homogeneous and heterogeneous architecture. In the homogeneous multicore architecture (Figure 1.1(a)), all PEs are identical. PEs in the heterogeneous multicore architecture (Figure 1.1(b)) are different types such as general purpose processors, hardware accelerators, dedicated IP cores, etc. Each PE can efficiently and effectively process specific application tasks.

- Memory system: Like other systems, memory in a multicore system contains application data as well as instruction data for instruction set processors. Based on the hierarchy of the memory modules, there are two types of memory systems: shared memory and distributed memory. In shared memory multicore systems, all PEs share the same memory resource (Figure 1.2(a)); therefore, any change made by one PE is visible for all other PEs in the system. In distributed memory multicore systems, each PE has its own memory resource (Figure 1.2(b)); therefore, one PE cannot directly read or write the memory of another PE. Some systems have a hybrid memory architecture of both shared and distributed memory. This type of memory architecture is referred to as heterogeneous memory.

- *Communication infrastructure*: The communication infrastructure component in a multicore system (also called interconnect) is a predefined backbone upon which other components are connected together. The communication infrastructure provides a medium for data exchange among PEs as well as between PEs and memory modules in multicore architectures. In modern digital system design, the communication infrastructure is a primary limitation in performance of the whole system [Dally and Towles, 2007]. Therefore, interconnect is a key factor in the digital system design.

Figure 1.1: (a) Homogeneous multicore; (b) Heterogeneous multicore

Compared to homogeneous multicore systems, heterogeneous multicore systems offer more computation power and efficient energy consumption [Kumar

et al., 2005] because of the efficiency of specialized cores for specific tasks. In the past years, a trend towards heterogeneous on chip platforms can be observed. Intel's Atom E6x5C Processor [Intel, 2010] uses multiple RISC cores in combination with an FPGA fabric provided by Altera. Another widely known heterogeneous system is IBM Cell Broadband Engine which contains one PowerPC processor and eight Synergistic Processor Elements [IBM, 2009]. Modern mobile devices are also based on heterogeneous system-on-chips (SoCs) combining CPUs, GPUs and specialized accelerators on a single chip.

As one of the main trends in heterogeneous multicore, hardware accelerator systems provide application specific hardware circuits and are thus more energy efficient and have higher performance than general purpose processors while still providing a significant degree of flexibility. Hardware accelerator systems have been considered as a main approach to continue performance improvement in the future [Borkar and Chien, 2011; Esmaeilzadeh et al., 2011]. They are increasingly popular both in the embedded system domain as well as in high performance computing. This technology has been popular for quite a while in academia [Vassiliadis et al., 2004; Voros et al., 2013] and more and more in the industry championed by companies such as Maxeler [Pell and Mencer, 2011], Convey [Convey Computer, 2012], IBM Power 8 [Stuecheli, 2013], Microsoft Catapult [Putnam et al., 2014], etc. In such systems, there is often one general purpose processor that functions as a host processor and one or more hardware accelerators that function as co-processors to speed-up the processing of special kernels of the application running on the host. Examples of application domains using such accelerators are image processing [Acasandrei and Barriga, 2013; Cong and Zou, 2009; Hung et al., 1999], video-based driver assistance [Claus and Stechele, 2010; Liu et al., 2011], bio-informatics applications [Heideman et al.,

Figure 1.2: (a) Shared memory; (b) Distributed memory

2012; Ishikawa et al., 2012; Sarkar et al., 2010], SAT problem solver [Yuan et al., 2012], etc. However, the main problem of those systems is the communication and data movement overhead they impose [Nilakantan et al., 2013].

## **1.1. PROBLEM OVERVIEW**

The need for computation power grows especially when we are entering into the big data era, where the amount of data grows faster than the capabilities of processing technology. One solution is to increase the number of processing cores especially hardware accelerator kernels for computationally intensive functions. However, the system performance does not scale in this approach due to the communication overhead which increases greatly with the increasing number of cores [Diamond et al., 2011]. In this dissertation, we address the issue of inter-connect design for the heterogeneous multicore systems while mainly focusing on hardware accelerator systems.

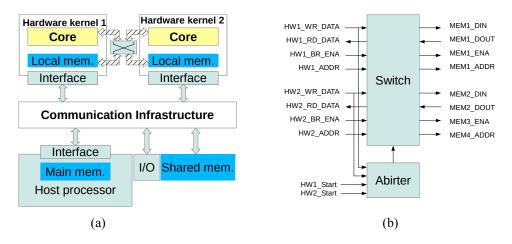

Interconnect in a multicore system plays an important role because data is exchanged between all components, typically between PEs and memory modules, using the interconnect. Interconnect design is one of the two open issues along with programming model in multicore system design [Rutzig, 2013]. Although data communication is a primary anticipated bottleneck for system performance [Dally and Towles, 2007; Kavadias et al., 2010; Orduña et al., 2004], the interconnect design for data communication among the accelerator kernels has not been well addressed in hardware accelerator systems. A simple bus or shared memory is usually used for data communication between the host and the kernels<sup>1</sup> as well as among the kernels. Although buses have some certain advantages such as low cost and simplicity, they become inefficient when the number of cores rises [Guerrier and Greiner, 2000]. Crossbars have been used to connect the PEs in some systems such as in [Cong and Xiao, 2013; Johnson and Nawathe, 2007]. Despite the high performance, crossbars suffer from high area cost and poor scalability [Rutzig, 2013]. Networks on Chips (NoCs) [Benini and De Micheli, 2002] have been proposed as an efficient communication infrastructure in large systems to allow parallel communication and to increase the scalability compared to buses. However, the major drawbacks of NoCs are the increased latency and implementation costs [Guerrier and Greiner, 2000]. Shared memory also has its own disadvantages such as restricted access due to the finite

<sup>&</sup>lt;sup>1</sup>In this work, we use the terminology *kernel* to refer to a dedicated hardware module/circuit that accelerates the processing of a computationally intensive software function.

number of memory ports.

An important challenge in hardware accelerator systems is to get the data to the computing core that needs it. Hiding data communication delay is needed to improve performance of the systems. In order to do this effectively, the resource allocation decision requires detailed and accurate information on the amount of data that is needed as input, and what will be produced as output. Evidently, there are dependencies among computations, since data produced by one kernel may be needed by another kernel. In order to have an efficient allocation scheme where the communication delays can be hidden as much as possible, a detailed profile of the data communication patterns is necessary for which the most appropriate interconnect infrastructure can be generated. Such communication patterns can be specific for each application and could lead to different types of interconnect. In this dissertation, we address the problem of automated generation of an optimized hybrid interconnect for a specific application.

#### **1.2.** DISSERTATION CHALLENGES

In state-of-the-art execution models of hardware accelerator systems in the literature, data input required for kernel computation is fetched to its local memory (buffers) when the kernel is invoked as described in [Cong and Zou, 2009] and [Canis et al., 2013]. This delays the start-up of kernel calculations until the whole data is available. Although there are some specific solutions to improve this communication behavior (presented in Section 2.4), those solutions are adhoc approaches for specific architectures or specific platforms. Moreover, those approaches have not taken the data communication pattern of the application into consideration. In contrast, we aim to provide a more generic solution and take the data communication pattern of the application into account.

In this work, we are targeting a generic heterogeneous hardware accelerator system containing general purpose processors and hardware accelerator kernels. The hardware accelerator kernels can be implemented by hardware fabrics such as FPGA, ASIC and GPU, etc. However, GPU interconnect is not reconfigurable in current day technology. Therefore, our discussion is mainly based on reconfigurable computing platforms.

Data communication in a hardware accelerator system can be optimized at both software and hardware levels (presented in Section 2.4). In this thesis we focus on the hardware level optimization. We therefore explore the following research questions:

**Question 1** How can data produced by an accelerator kernel be transferred to the consuming kernels as soon as it becomes available in order to reduce the delay of kernel calculation?

As we presented above, most hardware accelerator systems transfer input data required for kernel computation to the local memory of the kernel whenever it is invoked and copy back output data when it is finished. This forces the kernel computing to wait for data movement to complete. In this work, we try to answer this question using a generic approach to improve the system performance.

**Question 2** Does it pay off to build a dedicated and hybrid interconnect that provides the most appropriate support for the communication patterns inside an application?

Interconnect plays an important role in a multicore system. It not only contributes to system performance but also incurs hardware overhead. Therefore, we try to define a dedicated and hybrid interconnect that takes the data communication patterns inside an application into account; and try to see how efficient the hybrid interconnect is when compared to standard interconnect.

## **Question 3** *How can we achieve the most optimized system performance while keeping the hardware resource usage for the hybrid interconnect minimal?*

Building a hybrid interconnect that takes the communication patterns of an application into consideration to improve the system performance while keeping the hardware resource usage minimal is one of the main criteria. The reason for this requirement is that the more hardware resources are used, the more challenges are faced, such as power consumption or thermal emission. Therefore, we try to answer this question to achieve an optimized hybrid interconnect in term of system performance and hardware resource usage.

**Question 4** Can the reduction of energy consumption achieved by system performance improvement compensate for the increased energy consumption caused by more hardware resource usage for the hybrid interconnect?

A multicore system has a defined energy budget. Designing a new hybrid interconnect to improve system performance can lead to an increase in power consumption due to more hardware resource required for the interconnect. This, in turn, will lead to increasing overall energy consumption. Therefore, we try to answer this question to clarify the power utilization of the hybrid interconnect.

## **Question 5** Is the hybrid interconnect able to produce system performance improvement in both embedded and high performance computing systems?

Embedded and high performance computing accelerator systems are different. While most embedded accelerator platforms implement both the host and the accelerator kernels on the same chip, high performance computing platforms build them on different chips. The host processor in high performance computing platform usually works at a much higher frequency than the host in the embedded computing platform. Moreover, the communication infrastructure bandwidth in the high performance computing platforms is larger than in the embedded ones. Therefore, we explore whether the hybrid interconnect pays off in both types of systems or not.

## **1.3.** CONTRIBUTIONS

Based on the research questions presented in the previous section, we have been working on the interconnect of the multicore architecture, especially hardware accelerator systems, to solve those research challenges. The main contributions of the dissertation can be summarized as follows:

• We introduce an efficient execution model for a heterogeneous hardware accelerator system.

Based on a detailed and quantitative data communication profiling, a kernel knows exactly which kernels consume its output. Therefore, it can deliver the output directly to the consuming kernels rather than sending it back to the host. Consequently, this reduces the delay of the start-up of kernel calculation. This delivery process is supported by the hybrid interconnect dedicated for each application. The transfer process can be done in parallel with kernel execution.

• We propose a heuristic communication-aware approach to design a hardware accelerator system with a custom interconnect.

Given the fact that many hardware accelerator systems are implemented using embedded platforms where the hardware resource is limited, embedded hardware accelerator systems usually use a bus as the communication infrastructure. Therefore, we propose a heuristic approach that takes the data communication pattern inside an application into account to design a hardware accelerator system with an optimized custom interconnect. The approach is mainly useful for

embedded systems. A number of solutions are considered consisting of crossbarbased shared local memory, direct memory access (DMA), local buffer, and hardware duplication. An analytical model to predict system performance improvement is also introduced.

• We propose an automated approach using a detailed and quantitative communication profiling information to define a hybrid interconnect for each specific application, resulting in the most optimized performance with a low hardware resource usage and energy consumption.

Evidently, kernels and their communication behaviors are different from one application to the other. Therefore, a specific application should have a specific hybrid interconnect to get data efficiently to the kernels that need it. We call it hybrid interconnect as ultimately the entire interconnect will consist of not only a NoC but also uni- or bidirectional communication channels or locally shared buffers for data exchange. Although in our current experiments we statically define the hybrid interconnect for each application, the ultimate goal is to have a dynamically changing infrastructure in function of the specific communication needs of the application. The design approach results in an optimized hybrid interconnect while keeping the hardware resources usage for the interconnect minimal.

• We demonstrate our proposed hybrid interconnect in both an embedded platform and a high performance computing platform to verify the benefit of the hybrid interconnect.

Two heterogeneous multicore platforms are used to validate our automated hybrid interconnect design approach and the proposed execution model. Those are the Molen architecture implemented on a Xilinx ML510 board [Xilinx, 2009] and the Convey high performance computing system [Convey Computer, 2012]. Experimental results in both these platforms show the benefits of the hybrid interconnect in terms of system performance and energy consumption compared to the systems without our hybrid interconnect.

## **1.4.** DISSERTATION ORGANIZATION

The work in this dissertation is organized in 8 chapters. Chapter 2 gives a summary on standard on-chip interconnect techniques in the literature and analyzes

their advantages and disadvantages. Many taxonomies to classify the on-chip interconnects are presented. A survey on the hybrid interconnect architectures in the literature is also shown. This chapter also presents the state-of-the-art hardware accelerator systems and we zoom in on their interconnect aspects. Data communication optimization techniques in the literature for such systems are also summarized in the chapter.

Chapter 3 discusses an overview of our approach to design a hybrid interconnect for a specific application using quantitative data communication profiling information. The data communication-driven quantitative execution model is also presented. To further improve the system performance, parallelizing kernel processing is also analyzed in this chapter.

Chapter 4 analyzes different alternative interconnect solutions to improve the system performance of a bus-based hardware accelerator system. A number of solution are presented: DMA, crossbar, NoC, as well as combinations of these. This chapter also proposes the analytical models to predict the performance for these solutions and implements them in practice. We profile the application to extract the data input for the analytical models.

Chapter 5 presents a heuristic-based approach to design an application specific hardware accelerator system with a custom<sup>2</sup> interconnect using quantitative data communication profiling information. A number of solutions are considered in this chapter. Those are crossbar-based shared local memory, DMA support parallel processing, local buffer, and hardware duplication. Experimental results with different applications are done to validate the proposed heuristic approach. We also analyze the contribution of each solution to system performance improvement.

Chapter 6 introduces an automated interconnect design strategy to create an efficient custom interconnect for kernels in a hardware accelerator system to accelerate their communication behavior. Our custom interconnect includes a NoC, shared local memory solution, or both. Depending on the quantitative communication profiling of the application, the interconnect is built using our proposed custom interconnect design algorithm. An adaptive data communication-based mapping for the hardware accelerators is proposed to obtain a low overhead and latency interconnect. Experiments on both an embedded platform and a high performance computing platform are performed to validate the

<sup>&</sup>lt;sup>2</sup>In this work, we use two terminology *hybrid interconnect* and *custom interconnect* interchangeably.

proposed design strategy.

In Chapter 7, we present a case study of a heterogeneous hardware accelerator architecture to support streaming image processing. Each image in a dataset is preprocessed on a host processor and sent to hardware kernels. The host processor and the hardware kernels process a stream of images in parallel. The Convey hybrid computing system is used to develop our proposed architecture. The Canny edge detection application is used as our case study.

Finally, we summarize the list of our contribution and conclude this dissertation in Chapter 8. We also propose open questions and future research in this chapter.

## **BACKGROUND AND RELATED** WORK

I N this chapter, we give a summary of state-of-the-art standard on-chip interconnects. Many taxonomies to classify the on-chip interconnects are presented. A survey on the hybrid interconnect architectures is discussed. Hardware accelerator systems in the literature are also presented where we zoom in on their communication infrastructures. We also give an overview on the data communication optimization techniques in the literature for hardware accelerator systems.

## **2.1. ON-CHIP INTERCONNECT**

In modern digital systems, particularly in multicore systems, processing elements (PEs) are not isolated. They cooperate to process data. Therefore, the interconnection network (communication infrastructure) plays an important role to exchange data among the PEs as well as between the PEs and the memory modules. Choosing a suitable interconnection network has a strong impact on system performance. There are three main factors affecting the choice of an appropriate interconnection network for an underlying system. Those are performance, scalability and cost [Duato et al., 2002].

Interconnection networks connect components at different levels. Therefore, they can be classified into different groups [Dubois et al., 2014].

• On-chip interconnects connect PEs together and PEs to memory modules.

- I/O interconnects connect various I/O devices to the system communication infrastructure.

- Inter-system interconnects connect separated systems together. They include system area networks (SANs - connecting systems at a very short distances), local area networks (LANs - connecting systems within an organization or a building) and wide area networks (WANs - connecting multiple LANs at long distances).

- Internet is also a global and worldwide interconnect.

As a subset of a broader class - the interconnection network, on-chip interconnect transfers data between communicating nodes<sup>1</sup> in a system-on-chip (SoC). During the last decades, many on-chip interconnects have been proposed, along with the rising number of PEs in the systems. Figure 2.1 (adapted from [Matos et al., 2013]) summarizes the evolution of on-chip interconnects.

Figure 2.1: The evolution of the on-chip interconnects

There are many different ways to classify on-chip interconnects. Here, we list the five different well-known taxonomies.

#### Taxonomy 1 Mechanism-based classification.

Based on the mechanism upon which the processing elements communicate together, on-chip interconnects can be divided into two groups: shared memory and message passing [Pham et al., 2011].

<sup>&</sup>lt;sup>1</sup>a node is any component that connects to the network such as a processing element or a memory module

- *Shared memory*: the idea of shared memory is that the system consists of shared memories that are accessed by the communicating processing elements. The producing PEs write data to the shared memory modules while the consuming PEs read data from those shared memories. Examples of this interconnect type are bus systems, directly shared local memory, and crossbars.

- *Message passing*: in this interconnect type, communication among PEs is carried out by explicit messages. Data from the source PE is encoded to interconnect packets and sent to the destination PEs through the interconnect. Examples of this interconnect type are Network-on-Chips (NoCs).

#### Taxonomy 2 Connection-based classification.

Based on the connection of the PEs, interconnects can be categorized into four major classes: shared medium networks, direct networks, indirect networks and hybrid networks [Duato et al., 2002].

- *Shared medium networks*: in this type, the transmission medium is shared by all the communicating nodes. Examples for this type of interconnect are buses, and directly shared local memory.

- *Direct networks*: in this scheme, each communicating node has a router, and there are point-to-point links to connect one communicating node to a subset of other communicating nodes in the network. Examples of this category are NoCs.

- *Indirect networks*: networks belonging to this category have nodes connected together by one or more switches. Examples of this interconnect types are crossbars.

- *Hybrid network*: in general, the hybrid networks combine shared medium and direct or indirect networks to alleviate the disadvantages of one type by the advantages of the other type such as increasing bandwidth with respect to shared medium networks and decreasing the distance between nodes in direct and indirect networks.

#### Taxonomy 3 Communication link-based classification.

Based on how to connect a PE and a memory module to other PEs and memory modules, interconnects can be categorized into two categories: static and dynamic networks [Grama et al., 2002].

- *Static networks*: A static network consists of dedicated communication links established among the communicating nodes to form a fixed network. Examples of this type of networks are NoCs and directly shared local memory.

- *Dynamic networks*: A dynamic network consists of switches and communication links. The links are connected together dynamically through the switches to establish paths among communicating nodes. Examples for this type of networks are buses and crossbars.

#### Taxonomy 4 Switching technique-based classification.

Based on the switching techniques, the mechanisms for forwarding message from the source nodes to the destination nodes, of the interconnects, they can be classified into two classes: circuit switching and packet switching [El-Rewini and Abd-El-Barr, 2005].

- *Circuit switching networks*: In this group of networks, a physical path is established between the source and the destination before data is transmitted through the network. This established path exists during the whole data communication period; no other source and destination pair can share this path. Examples of this interconnect network group are buses, crossbar, and directly shared local memory.

- *Packet switching networks*: The networks in this group partition communication data into small fixed-length packets. Each packet is individually transferred from the source to the destination through the network. Examples of this group are NoCs, which may use either wormhole or virtual cut-through switching mechanisms.

#### **Taxonomy 5** Architecture-based classification.

Based on the interconnect architecture, interconnects can be classified into many different groups [Gebali, 2011; Kogel et al., 2006]. Here, we list only four well-known interconnects that are widely used in most hardware accelerator systems. Those are: directly shared local memory, bus, crossbar, and NoC.

- *Directly shared local memory*: In this interconnect scheme, PEs connect directly to memory modules through the memory ports as illustrated in Figure 2.2(a). Communication among the PEs is carried out through read and write operations.

- *Bus*: The bus is the simplest and most well-known interconnect. All the communicating nodes are connected to the bus as shown in Figure 2.2(b). Communication among the nodes follows a bus-protocol [Pasricha and Dutt, 2008].

- *Crossbar*: A crossbar is defined as a switch with *n* inputs and *m* outputs. Figure 2.2(c) depicts a 2 × 2 crossbar. A crossbar can connect any input to any free output. It is usually used to establish an interconnect for *n* processors and *m* memory modules.

- *NoC*: A NoC consists of routers or switches connected together by links. The connection pattern of these routers or switches forms a network topology. Examples of well-known network topologies are ring, 2D-mesh, torus or tree. Figure 2.2(d) illustrates a 2D-mesh NoC.

Figure 2.2: (a) Directly shared local memory; (b) Bus; (c) Crossbar; (d) Network-on-Chip

| Taxonomy   | <b>DSLM</b> <sup>a</sup> | Bus       | Crossbar  | NoC       |

|------------|--------------------------|-----------|-----------|-----------|

| Taxonomy 1 | shared                   | shared    | shared    | message   |

|            | memory                   | memory    | memory    | passing   |

| Taxonomy 2 | shared                   | shared    | indirect  | direct    |

|            | medium                   | medium    | network   | network   |

| Taxonomy 3 | dynamic                  | dynamic   | dynamic   | static    |

|            | network                  | network   | network   | network   |

| Taxonomy 4 | circuit                  | circuit   | circuit   | packet    |

|            | switching                | switching | switching | switching |

| Table 2.1: | Interconnect | classifications | overview |

|------------|--------------|-----------------|----------|

|            |              |                 |          |

<sup>a</sup>: Directly Shared Local Memory

Figure 2.3: Interconnects comparison.

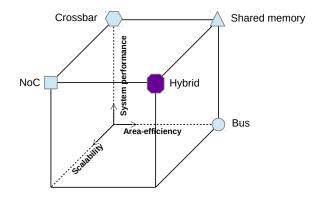

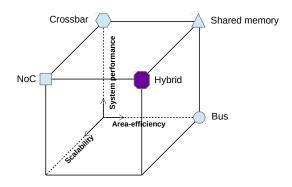

Table 2.1 shows the relationship between the taxonomies. Figure 2.3 illustrates the advantages and disadvantages of different interconnect types. While buses are simple and area-efficient, they suffer from low performance and scalability problems compared to the others because of the serialized communication [Sanchez et al., 2010]. A crossbar outperforms a bus in term of system performance because it offers separate paths from sources to destinations [Hur, 2011]. However, it has limited scalability because the area cost increases quadratically when the number of ports increases. While shared local memory can offer an area-efficient solution, its scalability is limited by the finite number of memory ports. Although NoCs have their certain advantages such as high performance and scalability, they suffer from a high area cost [Guerrier and Greiner, 2000]. Therefore, a hybrid interconnect with high performance, area-efficiency and high scalability is an essential demand.

## **2.2.** System-level Hybrid Interconnect

In this section, we review proposed hybrid interconnects in the literature. In the previous section, we introduced five different taxonomies to classify the interconnects. Each interconnect group has its own advantages and disadvantages. For example, compared to the indirect interconnect group, direct interconnects are simpler in term of implementation but have lower performance while indirect interconnects provide better scalability but are accomplished with higher cost. Circuit switching interconnects are faster and have higher bandwidth than packet switching interconnects but they may block other messages because the physical path is reserved during the message communication. Meanwhile, many messages can be processed simultaneously in packet switching interconnects, however message partitioning produces some overhead. Therefore, in recent years, hybrid interconnects have been proposed to take the advantages of different interconnect types.

Hybrid interconnects can be classified into two groups. In the first group, a combination of different topologies of NoCs forms a hybrid interconnect, for example, a combination of a 2D-mesh topology and a ring topology. We name this group as *mixed topologies hybrid interconnect*. The second group includes hybrid interconnects that utilize multiple interconnect architectures, for example, a combination of a bus and a NoC. We name this group as *mixed architectures hybrid interconnect*. The following sections present the proposed hybrid interconnects of these groups.

#### **2.2.1.** MIXED TOPOLOGIES HYBRID INTERCONNECT

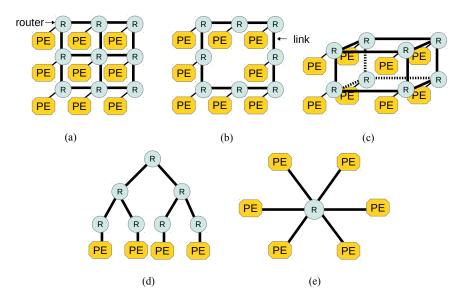

Network-on-chip topology [Jerger and Peh, 2009] refers to the structure upon which the nodes are connected together via the links. There are many standard topologies well presented in the literature. Figure 2.4 gives some examples of NoC topology including 2D-mesh, ring, hypercube, tree, and star. Although there are some certain advantages in those standard topologies, each topology suffers from some disadvantages, for example 2D-mesh has drawbacks in communication latency scalability, and the concentration of the traffic in the center of the mesh [Bourduas and Zilic, 2011] while ring topology does not offer a uniform latency for all nodes [Pham et al., 2011]. Therefore, hybrid topology or applicationspecific topology interconnects have been proposed. The following summary introduces some hybrid topology interconnects in the literature. The list is sorted by the publication year.

Figure 2.4: Examples of NoC topologies: (a) 2D-mesh; (b) ring; (c) hypercube; (d) tree; and (e) star.

CMesh (concentrated mesh) [Balfour and Dally, 2006] combines four communicating nodes into a group through a star connection. Those groups are connected together via a 2D-mesh network. Compared to the original mesh network, the CMesh network reduces the average hop count. As an extended CMesh network, the Flattened Butterfly network [Kim et al., 2007] adds dedicated links between the groups in a row or a column. With those point-to-point links, the maximum hop count of the Flattened Butterfly network is two. Simulation is used to evaluate both the network. The results show that CMesh has a 24% improvement in area-efficiency and a 48% reduction in energy consumption compared to other topologies. Compared to the mesh network, the Flattened Butterfly produces  $4 \times$  area reduction while reducing  $2.5 \times$  area when compared to CMesh.

Murali et al. [2006] proposed a design methodology that automated synthesizes a custom-tailored, application-specific NoC that satisfies the design objectives and the constraints of the targeted application domain. The main goal of the methodology is to design NoC topologies that satisfy two objective functions: minimizing network power consumption, and minimizing the hop-count. To achieve the goal, based on a task graph, the following steps are executed: 1) exploring several topologies with different number of switches; 2) automated performing floor-planning for the topologies; 3) choosing the topology that best optimizes the design objectives and satisfies all the constraints. Experimental results on an embedded platform using ARM processors as computing cores show that the synthesized topology improves system performance up to  $1.73 \times$  and reduces the power consumption  $2.78 \times$  in average when compared to the standard topologies.

The Mesh-of-Tree (MoT) interconnection network [Balkan et al., 2006] combines two sets of trees to connect processing elements (PEs) and memory modules. In contrast to other tree-based network architectures, where communicating nodes are connected to the leaf nodes, the communicating nodes are associated with the root nodes. The first set of trees, called the fan-out trees, is attached to PEs while the second set, called the fan-in set, is linked to memory modules. The leaf nodes of the fan-out set are associated with the leaf nodes of the fan-in set in an 1-to-1 mapping. The MoT network has two main properties: the path between each source and each destination is unique, and packets transferred between different sources and destinations will not interfere. Simulation is used to validate the proposed architecture. The results show that MoT can improve the network throughput by up to 76% and 28% when compared to butterfly and hypercube networks, respectively.

The hybrid MoT-BF network [Balkan et al., 2008] combining the MoT network and the area efficient butterfly network (BF) is an extended version of the MoT network. The main goal of this hybrid network is to reduce the area cost of the MoT network. Therefore, some intermediate nodes and leaf nodes of both the fan-in and fan-out trees are replaced by the  $2 \times 2$  butterfly networks. The number of replaced intermediate nodes is the level of the MoT-*h*-BF network where *h* is the network level. Simulation is done to validate the architecture and compare the throughput with the previous version. According to the results, a 64 terminals MoT-BF reduces 34% area overhead with only 0.5% sacrificing throughput compared to the MoT network.