Abstract

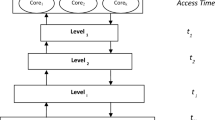

A system organised as a Hierarchy of Processor-And-Memory (HPAM) extends the familiar notion of memory hierarchy by including processors with different performance in different levels of the hierarchy. Tasks are assigned to different hierarchy levels according to their degree of parallelism. This paper studies the spatial locality (with respect to degree of parallelism) behaviour of simulated parallelised benchmarks in multi-level HPAM systems, and presents an inter-level cache coherence protocol that supports inclusion and multiple block sizes on an HPAM architecture. Inter-level miss rates and traffic simulation results show that the use of multiple data transfer sizes (as opposed to a unique size) across the HPAM hierarchy allows the reduction of data traffic between the uppermost levels in the hierarchy while not degrading the miss rate in the lowest level.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Cmelik, B., Keppel, D.: Shade: A fast instruction-set simulator for execution profiling. In: Proceedings of the 1994 SIGMETRICS Conf. on Measurement and Modeling of Computer Systems (1994)

Patterson, D., et al.: A Case for Intelligent RAM: IRAM. IEEE Micro, Los Alamitos (1997)

Figueiredo, R.J.O., Fortes, J.A.B., Ben-Miled, Z., Taylor, V., Eigenmann, R.: Impact of Computing-in-Memory on the Performance of Processorand- Memory Hierarchies. Technical Report TR-ECE-98-1, Electrical and Computer Engineering Department, Purdue University (1998)

Hagersten, E., Landin, A., Haridi, S.: DDM - A Cache-Only Memory Architecture. IEEE Computer, Los Alamitos (1992)

Hennessy, J.L., Patterson, D.A.: Computer Architecture: A Quantitative Approach. Morgan Kaufmann, San Francisco (1996)

Lenosky, D., Laudon, J., Gharacharloo, K., Gupta, A., Hennessy, J.: The Directory-Based Cache Coherence Protocol for the DASH Multiprocessor. In: Proc. of the 17th Annual Int. Symp. on Computer Architecture (May 1990)

Berry, M., et al.: The Perfect Club Benchmarks: Effective Performance Evaluation on Supercomputers. Technical Report UIUC-CSRD-827, Center for Supercomputing Research and Development, University of Illinois at Urbana-Champaign (July 1994)

Papamarcos, M., Patel, J.: A Low Overhead Coherence Solution for Multiprocessors with Private Cache Memories. In: Proc. of 11th Annual Int. Symp. On Computer Architecture (1984)

Dinda, P., et al.: The CMU Task parallel Program Suite. Technical Report CMUCS- 94-131, School of Computer Science, Carnegie Mellon University, Pittsburgh, Pennsylvania (January 1994)

Kogge, P.M., Sunaga, T., Miyataka, H., Kitamura, K., Retter, E.: Combined DRAM and Logic Chip for Massively Parallel Systems. In: 16th Conference on Advanced Research in VLSI (1995)

Standard Performance Evaluation Corporation. Spec newsletter (September 1995)

Blume, W., Doallo, R., Eigenmann, R., Grout, J., Hoeflinger, J., Lawrence, T., Lee, J., Padua, D., Paek, Y., Pottenger, B., Rauchwerger, L., Tu, P.: Parallel Programming with Polaris. IEEE Computer, Los Alamitos (1996)

Chen, Y.-S., Dubois, M.: Cache Protocols with Partial Block Invalidations. In: Proc. 7th Int. Parallel Processing Symp. (1993)

Ben-Miled, Z., Fortes, J.A.B.: A Heterogeneous Hierarchical Solution to Cost efficient High Performance Computing. In: Par. and Dist. Processing Symp. (October 1996)

Ben-Miled, Z., Eigenmann, R., Fortes, J.A.B., Taylor, V.: Hierarchical Processors-and-Memory Architecture for High Performance Computing. In: Frontiers of Massively Parallel Computation Symp. (October 1996)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1999 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Figueiredo, R.J.O., Fortes, J.A.B., Miled, Z.B. (1999). Spatial Data Locality with Respect to Degree of Parallelism in Processor-and-Memory Hierarchies. In: Hernández, V., Palma, J.M.L.M., Dongarra, J.J. (eds) Vector and Parallel Processing – VECPAR’98. VECPAR 1998. Lecture Notes in Computer Science, vol 1573. Springer, Berlin, Heidelberg. https://doi.org/10.1007/10703040_30

Download citation

DOI: https://doi.org/10.1007/10703040_30

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-66228-0

Online ISBN: 978-3-540-48516-2

eBook Packages: Springer Book Archive