Abstract

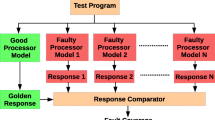

Core-based system-on-chip (SoC) design is quickly becoming a new paradigm in electronic system design due to the reusability of IP cores. However, the validation of IP cores is the most time consuming task in the design flow. This paper presents EmGen, an automatic test-program generation tool designed for embedded microprocessor cores. EmGen provides an configurable formal specification model with heuristic knowledge, which can generate test programs according to different configuration of microprocessors’ architecture, a test generation scheme based on heuristic algorithms, which can efficiently provide instructions in test programs, and validation testbenches, which support simulation with generated test programs automatically and check the equivalence of microprocessors and the specified instruction reference model. EmGen is currently in use at ICT for the verification of embedded microprocessor cores. Experiments results show that EmGen can improve verification process and cut down skilled manpower obviously.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Campenhout, D., Mudge, T., Hayes, J.: High-Level Test Generation for Design Verification of Pipelined Microprocessors. In: Proceeding of the 36th ACM/IEEE Design Automation Conference (DAC), pp. 184–188 (1999)

Fine, S., Ziv, A.: Coverage Directed Test Generation for Functional Verification Using Bayesian Networks. In: Proceeding of the 40th ACM/IEEE Design Automation Conference (DAC), pp. 286–291 (2003)

Emek, R., et al.: X-Gen: A Random Test-Case Generator for Systems and Socs. In: IEEE International High Level Design Validation and Test Workshop, Cannes (2002)

Lachish, O., Marcus, E., et al.: Hole Analysis for Functional Coverage Data. In: proceeding of the 39th ACM/IEEE Design Automation Conference (DAC), pp. 807–812 (2002)

Bartley, M., Galpin, D., Blackmore, T.: A Comparison of Three Verification Techniques: Directed Testing, Pseudo-Random Testing and Property Checking. In: Proceedings of the 39th ACM/IEEE Design Automation Conference (DAC), pp. 819–823 (2002)

Shen, H., et al.: Adaptive Test Program Generation for Embedded Microprocessor Core. In: Wu, Z., Chen, C., Guo, M., Bu, J. (eds.) ICESS 2004. LNCS, vol. 3605, pp. 472–479. Springer, Heidelberg (2005)

Synopsys, Inc.: Constrained-Random Test Generation and Functional Coverage with Vera (2003), http://www.synopsys.com/products/vera/vera60_wp.pdf

Verisity Design, Inc.: Specman Elite (2004), http://www.verisity.com/products/specman.html

Lipman, J.: Configurable SoCs Give You Options (2000), http://www.techonline.com/commnity/related_content/11384

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2005 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Shen, H., Chen, Y., Huang, J. (2005). EmGen: An Automatic Test-Program Generation Tool for Embedded IP Cores. In: Wu, Z., Chen, C., Guo, M., Bu, J. (eds) Embedded Software and Systems. ICESS 2004. Lecture Notes in Computer Science, vol 3605. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11535409_77

Download citation

DOI: https://doi.org/10.1007/11535409_77

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-28128-3

Online ISBN: 978-3-540-31823-1

eBook Packages: Computer ScienceComputer Science (R0)