Abstract

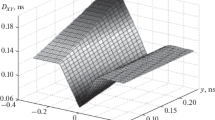

Nowadays, verification of digital integrated circuit has been focused more and more from the timing and area field to current and power estimations. The main problem with this kind of verification is on the lack of precision of current estimations when working at higher levels (logic, RT, architectural levels). To solve this problem it is not only necessary to use good current models for switching activity but, also, it is necessary to calculate this switching activity with high accuracy. In this paper we present an alternative to estimate current consumption using logic-level simulation. To do that, we use a simple but accurate enough current model to calculate the current consumption for each signal transition, and a delay model that obtains high accuracy when it is used to measure the switching activity (the Degradation Delay Model -DDM-). In the paper we present the current model for CMOS inverter, the characterization process and the model implementation in the logic simulator HALOTIS that includes the DDM. Results show a high accuracy in the estimation of current curves when compared to HSPICE, and a potentially large improvement over conventional approaches.

This work has been partially supported by the MEC META project TEC 2004-00840/MIC of the Spanish Government

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Arts, B., et al.: Stadistical power stimation of behavioral descriptions. In: Chico, J.J., Macii, E. (eds.) PATMOS 2003. LNCS, vol. 2799, pp. 197–207. Springer, Heidelberg (2003)

Bruno, M., Macii, A., Poncino, M.: A statistic power model for non.synthetic rtl operators. In: Chico, J.J., Macii, E. (eds.) PATMOS 2003. LNCS, vol. 2799, pp. 208–218. Springer, Heidelberg (2003)

Seen, E., Laurent, J., Julien, N., Martin, E.: Softexplorer: Estimation, characterizati ón and optimization of the power and energy consumption at the algoritmit level. In: Macii, E., Paliouras, V., Koufopavlou, O. (eds.) PATMOS 2004. LNCS, vol. 3254, pp. 342–351. Springer, Heidelberg (2004)

Lattanzi, E., Acquaviva, A., Alessandro, B.: Run-time software minitor of the power consumption of wireless network interface cards. In: Macii, E., Paliouras, V., Koufopavlou, O. (eds.) PATMOS 2004. LNCS, vol. 3254, pp. 352–361. Springer, Heidelberg (2004)

Jimenez, R., Parra, P., Sanmartin, P., Acosta, A.: Analysis of high-performance flips-flops for submicron mixed-signal applications. Int. Journal of Analg Integrated Circuits ans Signal Processing 33, 145–156 (2002)

Abbo, A.A., Kleihorst, R.P., Choudhary, V., Sevat, L.: Power consuption of performance-scaled simd processors. In: Macii, E., Paliouras, V., Koufopavlou, O. (eds.) PATMOS 2004. LNCS, vol. 3254, pp. 532–540. Springer, Heidelberg (2004)

Primepower reference manual in Synopsys, Inc., http://www.synopsys.com

Xpower reference manual in Xilinx, Inc., http://www.xilinx.com

Powertool reference manual in Veritools Inc., http://www.veritools.com

Bogliolo, A., Benini, L., De Micheli, G., Riccò, B.: Gate-level power and current simulation of cmos integrated circuits. IEEE Trans. on very large scale of integration (VLSI) systems 5, 473–488 (1997)

Nikolaidis, S., Chatzigeorgiou, A.: Analytical estimation of propagation delay and short-circuit power dissipation in cmos gates. International journal of circuit theory and applications 27, 375–392 (1999)

Baena, C., Juan, J., Bellido, M.J., Ruiz-de Clavijo, P., Jimenez, C.J., Valencia, M.: Simulation-driven switching activity evaluation of CMOS digital circuits. In: Proc. 16th Conference on Design of Circuits and Integrated Systems (DCIS) (November 2001)

Ghosh, A., Devadas, S., Keutzer, K., White, J.: Estimation of average switching activity in combinational and sequiential circuits. In: Proc. 29th Design Automation Conference, June 1992, pp. 253–259 (1992)

Metra, C., Favalli, B., Ricco, B.: Glitch power dissipation model. In: Proc. 5th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), September 1995, pp. 175–189 (1995)

Eisele, M., Berthold, J.: Dynamic gate delay modeling for accurate estimation of glitch power at logic level. In: Proc. 5th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS), September 1995, pp. 190–201 (1995)

Juan-Chico, J., Bellido, M.J., Ruiz-de Clavijo, P., Baena, C., Valencia, M.: Switching activity evaluation of cmos digital circuits using logic timing simulation. IEE Electronics Letters 37, 555–557 (2001)

Bellido-Díaz, M.J., Juan-Chico, J., Acosta, A.J., Valencia, M., Huertas, J.L.: Logical modelling of delay degradation effect in static CMOS gates. In: IEE Proc. Circuits Devices and Systems, vol. 147, pp. 107–117 (2000)

Ruiz-de Clavijo, P., Juan, J., Bellido, M.J., Acosta, A.J., Valencia, M.: Halotis: High Accuracy LOgic TIming Simulator with Inertial and Degradation Delay Model. In: Proc. Design, Automation and Test in Europe (DATE) Conference and Exhibition (March 2001)

Cadence home page, http://www.cadence.com

Maurine, P., Poirier, R., Azémard, N., Auvergne, D.: Switching current modeling in cmos inverter for speed and power estimation. In: Proc. 16th Conference on Design of Circuits and Integrated Systems (DCIS), November 2001, pp. 618–622 (2001)

Verilog resources page, http://www.verilog.com

Mentor graphics home page, http://www.mentor.com

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2005 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Ruiz de Clavijo, P. et al. (2005). Logic-Level Fast Current Simulation for Digital CMOS Circuits. In: Paliouras, V., Vounckx, J., Verkest, D. (eds) Integrated Circuit and System Design. Power and Timing Modeling, Optimization and Simulation. PATMOS 2005. Lecture Notes in Computer Science, vol 3728. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11556930_44

Download citation

DOI: https://doi.org/10.1007/11556930_44

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-29013-1

Online ISBN: 978-3-540-32080-7

eBook Packages: Computer ScienceComputer Science (R0)