Abstract

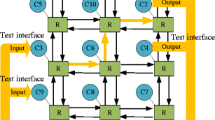

It may be impractical to have TAM for test usage only in NoC because it causes enormous hardware overhead. Therefore, the reuse of on-chip networks for TAM is very attractive and logical. In network-based TAM, an effective test scheduling for built-in cores is also important to minimize the total test time. In this paper, we propose a new efficient test scheduling algorithm for NoC based on the reuse of on-chip networks. Experimental results using some ITC’02 benchmark circuits show the proposed algorithm can reduce the test time by about 5 – 20% compared to previous methods. Consequently, the proposed algorithm can be widely used due to its feasibility and practicality.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Benini, L., Micheli, G.D.: Networks on Chips: A New SoC Paradigm. IEEE Computer, 70–78 (2002)

Guerrier, P., Greiner, A.: A Generic Architecture for On-Chip Packet-Switched Interconnections. In: Proc. of IEEE DATE, pp. 250–256 (2000)

Vermeulen, B., Dielissen, J., Goossen, K., Ciordas, C.: Bringing Communication Networks on a Chip: Test and Verification Implications. IEEE Communications Magazine, 74–81 (2003)

Nahvi, M., Ivanov, A.: Indirect Test Architecture for SoC Testing. IEEE Trans. on CAD, 1128–1142 (2004)

Liu, C., Cota, E., Sharif, H., Pradhan, D.K.: Test Scheduling for Network-on-Chip with BIST and Precedence Constraints. Proc. of IEEE ITC, 1369–1378 (2004)

Cota, E., et al.: The Impact of NoC Reuse on the Testing of Core-based Systems. Proc. of IEEE VTS, 128–133 (2003)

Cota, E., Carro, L., Wagner, F., Lubaszewski, M.: Power-Aware NoC Reuse on the Testing of Core-Based Systems. Proc. of IEEE ITC, 612–621 (2003)

Amory, A.M., et al.: Reducing Test Time with Processor Reuse in Network-on-Chip Based System. In: Proc. of the 17th Symposium on Integrated Circuits and Systems Design, pp. 111–116 (2004)

Busch, C., Herlihy, M., Wattenhofer, R.: Routing without Flow Control. In: Proc. of the 13th ACM Symposium on Parallel Algorithms and Architectures, pp. 11–20 (2001)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2005 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Ahn, JH., Moon, B.I., Kang, S. (2005). A Practical Test Scheduling Using Network-Based TAM in Network on Chip Architecture. In: Srikanthan, T., Xue, J., Chang, CH. (eds) Advances in Computer Systems Architecture. ACSAC 2005. Lecture Notes in Computer Science, vol 3740. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11572961_50

Download citation

DOI: https://doi.org/10.1007/11572961_50

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-29643-0

Online ISBN: 978-3-540-32108-8

eBook Packages: Computer ScienceComputer Science (R0)