Abstract

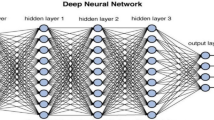

Neural Networks are usually implemented in software on sequential machines but when implemented in hardware, they are extremely fast due to the massive parallelism inherent in the hardware devices. Implementation of Neural Networks in Programmable Logic Devices such as FPGAs (Field Programmable Gate Arrays) gives us more flexibility since these devices are reconfigurable and their design can be altered whenever needed. The design proposed in this paper shows the implementation of perceptron neural network in FPGAs for the character recognition problem. The characters here are the English language alphabets which are input to the network and after training; they are tested for recognition. Each alphabet is tested for three different fonts. After implementation, the simulations are done and performance issues of the design are analyzed.The post-layout simulation gives excellent results even if some noise is introduced to the input patterns.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Ferrucci, A.: ACME: A Field Programmable Gate Array Implementation of a Self adapting and Scalable Connectionist Network. Masters Thesis, University of California, Santa Cruz (1994)

Fausett, L.V.: Fundamentals of Neural Networks: Architectures, Algorithms and Applications. Prentice-Hall International, Englewood Cliffs (1994)

Khan, A.H.: Multiplier-free Feedforward Networks. In: Proceedings of the IEEE International Joint Conference on Neural Networks (IJCNN), Honolulu, Hawaii, vol. 3, pp. 2698–2703 (2002)

Khan, F.A.: Implementation of Neural Network in FPGAs. Masters Thesis, GIK Institute of Engineering Sciences and Technology, Topi, Pakistan (2003)

Liao, Y.: Neural Networks in Hardware: A Survey. Report, Department of Computer Science. University of California, Davis CA (2001)

Ossoinig, H.: Design and FPGA-Implementation of a Neural Network. Masters Thesis, Institute for Technical Informatics, Graz University of Technology, Austria (1995)

Seiffert, U.: Artificial Neural Networks on Massively Parallel Computer Hardware. In: Proceedings of European Symposium on Artificial Neural Networks, Bruges, Belgium (2002)

Matlab available at MathWorks Homepage, http://www.mathworks.com/products/matlab/

Altera Homepage, http://www.altera.com/

Verilog HDL Homepage, http://www.verilog.com/

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Khan, F.A., Uppal, M., Song, WC., Kang, MJ., Mirza, A.M. (2006). FPGA Implementation of a Neural Network for Character Recognition. In: Wang, J., Yi, Z., Zurada, J.M., Lu, BL., Yin, H. (eds) Advances in Neural Networks - ISNN 2006. ISNN 2006. Lecture Notes in Computer Science, vol 3973. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11760191_197

Download citation

DOI: https://doi.org/10.1007/11760191_197

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-34482-7

Online ISBN: 978-3-540-34483-4

eBook Packages: Computer ScienceComputer Science (R0)