Abstract

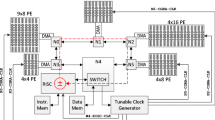

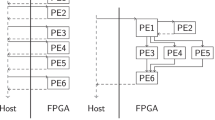

The increasing number of cores used on a single die in response to the power-computing applications tends to orient SoCs more and more toward communication-centric concept. Networks-on-chip (NoC) are good candidates providing both parallelism and flexibility. Nevertheless they imply to consider the notion of locality when distributing the computation among a set of cores. Defining an optimal placement at compile-time is difficult since other applications may temporarily make use of some of the processing resources. This paper explores the opportunity of dynamically mapping task graphs through using different placement algorithms, experiments and comparisons are conducted on a homogeneous coarse-grain reconfigurable architecture running JPEG applications. Results show that run-time task mapping is possible and brings interesting benefits over a random or static placement, especially when contention effects stemming from the communication medium are taken into account.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Lodi, et al.: A VLIW Processor With Reconfigurable Instruction Set for Embedded Application. IEEE Journal of Solid State Circuit 38(11) (November 2003)

Dally, W.J., Towles, B.: Route Packets, Not Wires: On-Chip Interconnection Networks. In: Proceedings of the Design Automation Conference, Las Vegas, NV, pp. 684–689 (June 2001)

Moraes, F.G., Mello, A.V., de Möller, L.H., Ost, L., Calazans, N.L.V.: A Low Area Overhead Packet-switched Network on Chip: Architecture and Prototyping. In: IFIP VLSI SOC 2003, International Conference on Very Large Scale Integration, Darmstadt (2003)

Marescaux, T., Mignolet, J.-Y., Bartic, A., Moffat, W., Verkest, D., Vernalde, S., Lauwereins, R.: Networks on Chip as Hardware Component of an OS for reconfigurable Systems. In: Y. K. Cheung, P., Constantinides, G.A. (eds.) FPL 2003. LNCS, vol. 2778. Springer, Heidelberg (2003)

Nollet, V., Coene, P., Verkest, D., Vernalde, S., Lauwereins, R.: Designing an Operating System for Heterogeneous Reconfigurable SoC. In: 10th Reconfigurable Architectures Workshop (RAW), Nice, France (2003)

Mignonet, J.-Y., Nollet, V., Coene, P., Verkest, D., Vernalde, S., Lauwereins, R.: Infrastructure for design and management of relocatable tasks in a heterogeneous reconfigurable system-on-chip. Proceedings of the DATE 2003 conference, Munich, pp. 986–991 (2003) ISBN 0-7695-1870-2

Nollet, V., Avasare, P., Mignolet, J.-Y., Verkest, D.: Low cost Task Migration Initiation in a Heterogenous MP-SoC. In: Proceedings of the DATE 2005 conference (2005)

Nollet, V., Marescaux, T., Verkest, D.: Operating System Controlled Network on Chip. In: DAC 2003 (2003)

Steiger, C., Walder, H., Platzner, M.: Operating Systems for Reconfigurable Embedded Platform: Online scheduling of Real-Time Tasks. IEEE Transactions on Computers 53(11) (November 2004)

Sassatelli, G., Torres, L., Benoit, P., Gil, T., Diou, C., Cambon, G., Galy, J.: Highly Scalable Dynamically Reconfigurable SystolicRing-Architecture for DSP applications. In: IEEE DATE 2002, France (2002)

Baumgarte, V., May, F., Nückel, A., Vorbach, M., Weinhardt, M.: PACT-XPP A Self-Reconfigurable Data Processing Architecture. The Journal of supercomputing 26, 167–184 (2003)

OMAP2420, www.ti.com

Caspi, E., Chu, M., Huang, R., Weaver, N., Yeh, J., Wawrzynek, J., DeHon, A.: Stream Computations Organized for Reconfigurable Execution (SCORE). In: Grünbacher, H., Hartenstein, R.W. (eds.) FPL 2000. LNCS, vol. 1896, pp. 605–614. Springer, Heidelberg (2000)

Heysters, P., Smit, G.: A Flexible and Energy-Efficient Coarse-Grained Reconfigurable Architecture for Mobile Systems. The Journal of supercomputing 26, 283–308 (2003)

OCPIP specification version 2.0, Available at: http://www.ocpip.org

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Ngouanga, A., Sassatelli, G., Torres, L., Gil, T., Suarez, A.B., Susin, A.A. (2006). Run-Time Resources Management on Coarse Grained, Packet-Switching Reconfigurable Architecture: A Case Study Through the APACHES’ Platform. In: Bertels, K., Cardoso, J.M.P., Vassiliadis, S. (eds) Reconfigurable Computing: Architectures and Applications. ARC 2006. Lecture Notes in Computer Science, vol 3985. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11802839_19

Download citation

DOI: https://doi.org/10.1007/11802839_19

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-36708-6

Online ISBN: 978-3-540-36863-2

eBook Packages: Computer ScienceComputer Science (R0)