Abstract

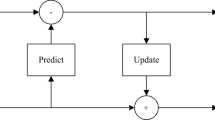

In this paper, we proposed a new architecture of lifting process for JPEG2000 and implemented it as an ASIC. It includes a new cell-structure that executes a unit lifting calculation to satisfy the property of lifting process of a repetitive arithmetic with a unit process. After the operational sequence of lifting arithmetic was analyzed in detail and the causality was imposed to implement in H/W, the unit cell was optimized. A new simple lifting kernel was organized possible by repeatedly arranging the unit cells and a lifting processor was realized with the kernel for Motion JPEG2000. From the comparison with previous works, we could conclude that the proposed architecture shows excellent properties in considering both the cost and the performance.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Boliek, M., Christopoulos, C., Majani, E.: JPEG2000 part-I fina1 draft international standard: ISO/IEC JTC1/SC29 WG1 (2000)

Parhi, K.K., Nishitani, T.: VLSI architectures for discrete wavelet transforms. IEEE Trans. VLSI Syst. 1, 191–202 (1993)

Grzeszczak, A., Mandal, M.K., Panchanathan, S., Yeap, T.: VLSI implementation of discrete wavelet transform. IEEE Trans. VLSI Syst. 4, 421–433 (1996)

Lafruit, G., Nachtergaele, L., Bormans, J., Engels, M., Bolsens, I.: Optimal memory organization for scalable texture codecs in MPEG-4. IEEE Trans. Circuits Syst. Video Technol. 9, 218–243 (1999)

Ferretti, M., Rizzo, D.: A parallel architecture for the 2-D discrete wavelet transform with integer lifting scheme. J. VLSI Signal Processing 28, 165–185 (2001)

Andra, K., Chakrabarti, C., Acharya, T.: A VLSI architecture for lifting-based forward and inverse wavelet transform. IEEE Trans. on Signal Processing 50(4) (2002)

Dillen, G., Georis, B., Legat, J.D., Cantineau, O.: Combined Line-Based Architecture for the 5-3 and 9-7 Wavelet Tansform of JPEG 2000. IEEE Transactions on Circuit Syst. Video Technol. 13(9) (2003)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Seo, YH., Kim, DW. (2006). A New VLSI Architecture of Lifting-Based DWT. In: Bertels, K., Cardoso, J.M.P., Vassiliadis, S. (eds) Reconfigurable Computing: Architectures and Applications. ARC 2006. Lecture Notes in Computer Science, vol 3985. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11802839_20

Download citation

DOI: https://doi.org/10.1007/11802839_20

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-36708-6

Online ISBN: 978-3-540-36863-2

eBook Packages: Computer ScienceComputer Science (R0)