Abstract

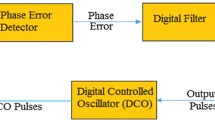

The aim of this study is to provide a multi level VHDL-AMS modeling of an analog Phase Locked Loop (PLL). Three model levels are described, analyzed and compared in terms of simulation CPU times and accuracy. The characteristic parameters of the PLL, such as the settling time, overshoot, voltage variations linked to charge pump architecture and final voltage are extracted from the intermediate level.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Nicolle, B., et al.: VHDL-AMS modeling of a multistandard Phase Locked Loop. In: ICECS 2005 Proceeding, pp. 33–36 (2005)

Pamarti, Jansson, Galton: A Wideband 2.4GHz Delta Sigma Fractional N PLL with 1Mb/s in loop modulation. IEEE Journal of Solid State Circuits 39(1), 4962 (2004)

Application notes for ADS Software, PLL Transient Response Simulation, Tutorial

Allen, P.E.: CMOS phase locked loops Lecture 130 (2003)

Juarez-Hernandez, E., Diaz-Sanchez, A.: A novel CMOS charge-pump circuit with positive feedback for PLL applications. In: Electro 2001 (2001)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Nicolle, B., Tatinian, W., Oudinot, J., Jacquemod, G. (2006). Hierarchical Modeling of a Fractional Phase Locked Loop. In: Vounckx, J., Azemard, N., Maurine, P. (eds) Integrated Circuit and System Design. Power and Timing Modeling, Optimization and Simulation. PATMOS 2006. Lecture Notes in Computer Science, vol 4148. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11847083_43

Download citation

DOI: https://doi.org/10.1007/11847083_43

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-39094-7

Online ISBN: 978-3-540-39097-8

eBook Packages: Computer ScienceComputer Science (R0)