Abstract

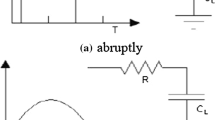

In this work we will introduce an enhanced, CMOS-compatible adiabatic logic family based on a new diode element for charge recovery. This diode element uses bipolar transistors to reduce the diode forward voltage losses in existing charge recovery logic families allwoing the use at lower supply voltages. Based on this element the CMOS compatible, static adiabatic logic familiy biQSERL is introduced.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Ye, Y., Roy, K.: QSERL: Quasi-Static Energy Recovery Logic. IEEE Journal of Solid-State Circuits 36, 239–248 (2001)

Lim, J., Kwon, K., Chae, S.-I.: NMOS reversible energy recovery logic for ultra-low-energy applications. IEEE Journal of Solid-State Circuits 35, 865–875 (2000)

Kim, S., Papaefthymiou, M.C.: True single-phase adiabatic circuitry. IEEE Transactions on Very Large Scale Integration 9, 52–63 (2001)

Paul, S., Schlaffer, A.M., Nossek, J.A.: Optimal Charging of Capacitors. IEEE Transactions on Circuits and Systems I 47, 1009–1015 (2000)

De, V.K., Meindl, J.D.: Complementary adiabatic and fully adiabatic MOS logic families for gigascale integration. In: 43rd Solid-State Circuits Conference (ISSCC), Digest of Technical Papers, pp. 298–299 (1996)

Reisch, M.: High-Frequency Bipolar Transistors. Springer, Heidelberg (2003)

Athas, W., Svensson, L., Tzartzanis, N.: A resonant signal driver for two-phase, almost-non-overlapping clocks. In: IEEE Symposium on Circuits and Systems (ISCAS), Digest of Technical Papers, ISCAS, pp. 298–299 (1996)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Schlachta, C., Glesner, M. (2006). A CMOS Compatible Charge Recovery Logic Family for Low Supply Voltages. In: Vounckx, J., Azemard, N., Maurine, P. (eds) Integrated Circuit and System Design. Power and Timing Modeling, Optimization and Simulation. PATMOS 2006. Lecture Notes in Computer Science, vol 4148. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11847083_55

Download citation

DOI: https://doi.org/10.1007/11847083_55

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-39094-7

Online ISBN: 978-3-540-39097-8

eBook Packages: Computer ScienceComputer Science (R0)