Abstract

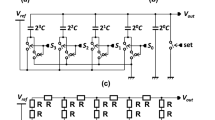

A novel CMOS four-quadrant analog-digital multiplier for implementing a programmable Cellular Neural Network (CNN) is presented. The circuit, which can be fabricated in a standard CMOS process, performs the four-quadrant weighting of interconnect signals. Using this multiplier a programmable CNN neuron can be implemented with little expense. Both simulation and test results are given for the circuit fabricated in a standard, mixed signal, 0.18μm, CMOS process. According to this design, one input is analog voltage and the other input is digital signal. The linearity deviation is less than 1% in the dynamic range (1.0V,2.2V) centered on Vref=1.6V. The power supply voltage is 3.3V.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Chua, L.O., Yang, L.: Cellular Neural Networks: Theory. Circuits and Systems. IEEE Transactions on 35(10), 1257–1272 (1988)

Harrer, H., Venetianer, P.L., Nossek, J.A., Roska, T., Chua, L.O.: Some Examples of Preprocessing Analog Images with Discrete-Time Cellular Neural Networks. In: Cellular Neural Networks and their Applications. CNNA 1994, Proceedings of the Third IEEE International Workshop on, pp. 201–206 (1994)

Tanaka, M., Tanji, Y., Onishi, M., Nakaguchi, T.: Lossless Image Compression and Reconstruction by Cellular Neural Networks. In: Cellular Neural Networks and Their Applications, 2000 (CNNA 2000). Proceedings of the 2000 6th IEEE International Workshop on, pp. 57–62 (2000)

Khryasshyov, V.V., Sautov, E.Y., Sokolenko, E.A.: Cellular Neural Network in Image Filtration Tasks. In: Circuits and Systems for Communications, 2002. Proceedings. ICCSC 2002. 1st IEEE International Conference on, pp. 267–270 (2002)

Cardarilli, G.C., Lojacono, R., Salerno, M., Sargeni, F.: VLSI Implementation of a Cellular Neural Network with Programmable Control Operator. In: Circuits and Systems, 1993. Proceedings of the 36th Midwest Symposium on, vol. 2, pp. 1089–1092 (1993)

Espejo, S., Carmona, R., Dominguez-Castro, R., Rodriguez-Vazquez, A.: A CNN Universal Chip in CMOS Technology. International Journal of Circuit Theory and Applications 24, 93–109 (1996)

Sindhwani, M., Srikanthan, T., Asari, K.V.: VLSI Efficient Discrete-Time Cellular Neural Network Processor. Circuits, Devices and Systems, IEE Proceedings 149(3), 167–171 (2002)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2006 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Wang, P., Zhang, X., Jin, D. (2006). A Novel Multiplier for Achieving the Programmability of Cellular Neural Network. In: King, I., Wang, J., Chan, LW., Wang, D. (eds) Neural Information Processing. ICONIP 2006. Lecture Notes in Computer Science, vol 4234. Springer, Berlin, Heidelberg. https://doi.org/10.1007/11893295_132

Download citation

DOI: https://doi.org/10.1007/11893295_132

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-46484-6

Online ISBN: 978-3-540-46485-3

eBook Packages: Computer ScienceComputer Science (R0)