Abstract

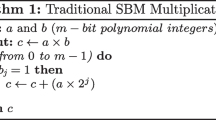

According to VLSI theory, [logn, √n] is the range of computation times for which there may exist an AT2-optimal multiplier of n-bit integers. Such networks were previously known for the time range [Ω(log2n), 0(√n)]; in this paper we settle this theoretical question, by exhibiting a-class of AT2-optimal multipliers with computation times [Ω(logn), 0(n1/2)]. Our designs are based on the DFT on a Fermat ring, whose elements are represented in a redundant radix-4 form to ensure 0(1) addition time.

This work was supported by the National Science Foundation under Grants MCS-81-05552 and ECS-81-06939; additional support was provided by Deutsche Forschungsgemeinschaft SFB 124, VLSI — Entwurf und Parallelität.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

H. Abelson and P. Andreae, "Information transfer and area-time trade-offs for VLSI-multiplication," Communications of the ACM, vol. 23, n. 1, pp. 20–22, Jan. 1980.

A. V. Aho, J. E. Hopcroft and J. D. Ullman, The Design and Analysis of Computer Algorithms, Addision-Wesley, Reading, MA, 1974.

B. Becker, "Schnelle Multiplizierwerke für VLSI — Implementierung," Technical Report, Uni. des Saarlandes, 1982.

R. P. Brent and H. T. Kung, "The chip complexity of binary arithmetic," J. Ass. Comp. Mach., vol. 28, pp. 521–534, July 1981.

L. Dadda, "Some schemes for parallel multipliers," Alta Frequenza, vol. 34, pp. 343–356, 1965.

A. Karazuba und Y. Ofman, "Multiplication of multidigit numbers on automata," Doklady Akademija Nauk SSSR, vol. 145, pp. 293–294, 1962.

Th. Lengauer und K. Mehlhorn, "VLSI complexity theory, efficient VLSI algorithms and the HILL design system," in The International Professorship in Computer Science: Algorithmics for VLSI, Ed. Trullemans, Academic Press, to appear.

W. K. Luk and J. E. Vuillemin, "Recursive implementation of optimal time VLSI integer multipliers," VLSI83, Trondheim, Norway, September 1983

K. Mehlhorn, AT2-optimal VLSI-circuits for integer division and integer square rooting, submitted for publication.

F. P. Preparata and J. Vuillemin, "Area-time optimal VLSI networks for computing integer multiplication and Discrete Fourier Transform," Proceedings of I.C.A.L.P., Haifa, Israel, July 1981, pp. 29–40.

F. P. Preparata and J. Vuillemin, "The Cube-Connected-Cycles: A versatile network for parallel computation," Communications of the ACM, vol. 24, n. 5, pp. 300–309, May 1981.

A. Schönhage and V. Strassen, "Schnelle Multiplikation grosser Zahlen," Computing 7, pp. 281–292, 1971.

C. D. Thompson, "Area-time complexity for VLSI," Proc. of the 11th Annual ACM Symposium on the Theory of Computing (SIGACT), pp. 81–88, May 1979

J. E. Vuillemin, "A very fast multiplication algorithm for VLSI implementation," Integration, VLSI Journal, vol. 1, n. 1, pp. 33–52, 1983.

C. S. Wallace, "A suggestion for a fast multiplier," IEEE Transactions on computers, vol. EC-13, n. 2, pp. 14–17, 1964.

Editor information

Rights and permissions

Copyright information

© 1984 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Mehlhorn, K., Preparata, F.P. (1984). Area-time optimal vlsi integer multiplier with minimum computation time. In: Paredaens, J. (eds) Automata, Languages and Programming. ICALP 1984. Lecture Notes in Computer Science, vol 172. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-13345-3_31

Download citation

DOI: https://doi.org/10.1007/3-540-13345-3_31

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-13345-2

Online ISBN: 978-3-540-38886-9

eBook Packages: Springer Book Archive