Abstract

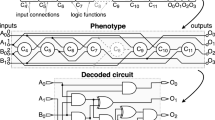

In this paper, we show how artificial evolution can be used to improve the fault-tolerance of electronic circuits. We show that evolution is able to improve the fault tolerance of a digital circuit, given a known fault model. Evolution is also able to create sets of different circuits that, when combined into an ensemble of circuits, have reduced correlation in their fault pattern, and therefore improved fault tolerance. An important part of the algorithm used to create the circuits is a measure of the correlation between the fault patterns of different circuits. Using this measure in the fitness, the circuits evolve towards different, highly fault-tolerant circuits. The measure also proves very useful for fitness sharing purposes. We have evolved a number of circuits for a simple 2x3 multiplier problem, and use these to demonstrate the performance under different simulated fault models.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Canham, R. O. amp; Tyrrell, A. M. (2002). Evolved fault tolerance in evolvable hardware, Congress on Evolutionary Computation CEC 2002, Hawaii, pp. 1267–1272.

Lala, J. H. amp; Harper, R. E. (1994). Architectural principles for safety critical real-time applications, Proceedings of the IEEE 82(1).

Miller, J. F., Job, D. amp; Vassilev, V. K. (2000). Principles in the evolutionary design of digital circuits—part i, Journal of Genetic Programming and Evolvable Machines 1(1): 8–35.

Mitra, S. amp; McCluskey, E. (2000). Word-voter: A new voter design for triple modular redundant systems, 18th IEEE VLSI Test Symposium, Montreal, Canada, pp. 465–470.

Mitra, S., Saxena, N. amp; McCluskey, E. (1999). A design diversity metric and reliability analysis for redundant systems, Proc. 1999 Int. Test Conf, Atlantic City, NJ, pp. 662–671.

Mitra, S., Saxena, N. amp; McCluskey, E. (2001). Techniques for estimation of design diversity for combinational logic circuit, Int. Conf. on Dependable Systems and Networks (DSN’01), Goteborg, Sweden, pp. 25–34.

T. Yu, J. F. M. (2001). Neutrality and evolvability of a boolean function landscape, in J. F. Miller, M. Tomassini, P. L. Lanzi, C. Ryan amp; W. Langdon (eds), Procedings of the 4th European Conference on Genetic Programming (EuroGP2001), Springer-Verlag, pp. 204–217.

Tyrrell, A., Hollingworth, G. amp; Smith, S. (2001). Evolutionary strategies and intirinsic fault tolerance, in D. Keymeulen, J. Lohn amp; R. Zebulum (eds), The Third NASA/DoD Workshop on Evolvable Hardware, Long Beach, CA, pp. 98–106.

V. K. Vassilev, Dominic Job, J. F. M. (2000). Towards the automatic design of more efficient digital circuits, in J. Lohn, A. Stoica, D. Keymeulen amp; S. Colombano (eds), Proceedings of the 2nd NASA/DOD Workshop on Evolvable Hardware, IEEE Computer Society, Los Alamitos, CA, pp. 151–160.

Vassilev, V. amp; Miller, J. F. (2000). The advantages of landscape neutrality in digital circuit evolution, in J. F. Miller, A. Thompson, P. Thomson amp; T. Fogarty (eds), Third International Conference on Evolvable Systems: From Biology to Hardware, Springer-Verlag, Edinburgh, pp. 252–263.

Yao, X. amp; Liu, Y. (2002). Getting most of evolutionary approaches, in A. Stoica, J. Lohn, R. Katz, D. Keymeulen amp; R. Zebulum (eds), 2002 NASA/DoD Conference on Evolvable Hardware (EH’02), IEEE Computer Society, Alexandria, Virginia, pp. 8–14.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2003 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Schnier, T., Yao, X. (2003). Using Negative Correlation to Evolve Fault-Tolerant Circuits. In: Tyrrell, A.M., Haddow, P.C., Torresen, J. (eds) Evolvable Systems: From Biology to Hardware. ICES 2003. Lecture Notes in Computer Science, vol 2606. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-36553-2_4

Download citation

DOI: https://doi.org/10.1007/3-540-36553-2_4

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-00730-2

Online ISBN: 978-3-540-36553-2

eBook Packages: Springer Book Archive