Abstract

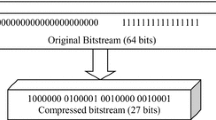

One important algorithm for data compression is the variable length coding that often utilizes large code tables.Despite the progress modern FPGAs made, concerning the available logic resources, an ef.cient mapping of those tables is still a challenging task.In this paper, we describe an ef.cient mapping methodology for code trees onto LUT-based FPGAs.Due to an adaptation to the LUT’s number of inputs, for large code tables a reduction of up to 40% of logic blocks is achievable compared with a conventional gate-based implementation.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

ITU-T Draft Recommendation H.263, “Video coding for low bitrate communication,” 1995.

ISO-IEC IS 13818, “Generic Coding of Moving Pictures and Associated Audio,” 1994.

Xilinx Inc., http://www.xilinx.com/products/virtex.htm, 2000.

Xilinx Inc., Core Solutions Data Book, 1997.

Altera Co., Data Sheet FLEX10K, 1995.

Altera Co., http://www.altera.com/html/products/apex.html, 2000.

Vantis Inc., Preliminary: Vantis VF1 Field Programmable Gate Array, 1998.

D.A. Huffman, “A Method for the Construction of Minimum-Redundancy Codes,” Proc. IRE 40, Sept. 1952, pp. 1098–1101.

H. Park, and V.K. Prasanna, “Area Ef.cient VLSI Architectures for Huffman Coding” IEEE Trans. on Circuits and Systems-II, Nr. 9 Vol. 40, Sept. 1993, pp. 568–575.

A. Mukherjee, N. Ranganathan, and M. Bassiouni, “Efficient VLSI Design for Data Transformation of Tree-Based-Codes” IEEE Trans. on Circuits and Systems, Nr. 3 Vol. 18, Mar. 1991, pp. 306–314.

V. Betz, J. Rose, “How Much Logic Should Go in an FPGA Logic Block?” IEEE Design and Test of Computers, Nr. 1 Vol. 15, Jan.–Mar. 1998, pp. 10–15.

H. Kropp, C. Reuter, P. Pirsch, “The Video and Image Emulation System VIPES,” Proc. 9th Int’l Works. Rapid System Prototyping, June 1998, pp. 177–275.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2000 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Kropp, H., Reuter, C. (2000). A Mapping Methodology for Code Trees onto LUT-Based FPGAs. In: Hartenstein, R.W., Grünbacher, H. (eds) Field-Programmable Logic and Applications: The Roadmap to Reconfigurable Computing. FPL 2000. Lecture Notes in Computer Science, vol 1896. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-44614-1_25

Download citation

DOI: https://doi.org/10.1007/3-540-44614-1_25

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-67899-1

Online ISBN: 978-3-540-44614-9

eBook Packages: Springer Book Archive