Abstract

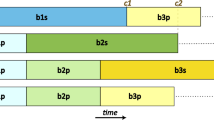

Enhanced pipeline scheduling (EPS) is a software pipelining technique which can achieve a variable initiation interval (II) for loops with control flows via its code motion pipelining. EPS, however, leaves behind many renaming copy instructions that cannot be coalesced due to interferences. These copies take resources, and more seriously, they may cause a stall if they rename a multi-latency instruction whose latency is longer than the II aimed for by EPS.

This paper describes how those renaming copies can be deleted through unrolling, which enables EPS to avoid a serious slowdown from latency handling and resource pressure while keeping its variable II and other advantages. In fact, EPS’s renaming through copies, followed by unroll-based copy elimination, provides a more general and simpler solution to the cross-iteration register overwrite problem in software pipelining which works for loops with control flows as well as for straight-line loops. Our empirical study performed on a VLIW testbed with a two-cycle load latency shows that the unrolled version of the 16-ALU VLIW code includes fewer no-op VLIWs caused by stalls, improving the performance by a geometric mean of 18%, yet the peak improvement with a longer latency reaches as much as a geometric mean of 25%.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

K. Ebcioğlu and T. Nakatani. A New Compilation Technique for Parallelizing Loops with Unpredictable Branches on a VLIW architecture. In Languages and Compilers for Parallel Computing, pages 213–229. MIT Press, 1989.

S.-M. Moon, S. Kim, and J. Park. Unroll-based Copy Coalescing. Technical report, Seoul National University, 1997.

M. Lam. Software Pipelining: An Effective Scheduling Technique for VLIW Machines. In Proceedings of the SIGPLAN 1988 Conference on Programming Language Design and Implementation, pages 318–328, 1988.

S.-M. Moon and K. Ebcioğlu. Parallelizing Nonnumerical Code with Selective Scheduling and Software Pipelining. ACM Transactions on Programming Languages and Systems, 19(6):853–898, Nov. 1997.

V. Allan, R. Jones, R. Lee, and S. Allan. Software Pipelining. ACM Computing Surveys, 27(3):367–432, Sep. 1995.

B. Rau and C. Glaeser. Some Scheduling Techniques and an Easily Schedulable Horizontal Architecture for High Performance Scientific Computing. In Proceedings of the 14th Annual Workshop on Microprogramming (Micro-14), pages 183–198, 1981.

Nancy J. Warter-Perez and Noubar Partamian. Modulo Scheduling with Multiple Initiation Intervals. In Proccedings of the 28th Annual ACM/IEEE International Symposium on Microarchitecture (Micro-28), pages 111–118, 1995.

Mark G. Stoodley and Corinna G. Lee. Software Pipelining Loops with Conditional Branches. In Proceedings of the 29th Annual ACM/IEEE International Symposium on Microarchitecture (Micro-29), 1996.

A. Aiken, A. Nicolau, and S. Novack. Resource-Constrained Software Pipelining. IEEE Transactions on Parallel and Distributed Systems, 6(12):1248–1269, Dec 1995.

J. Dehnert, P. Hsu, and J. Bratt. Overlapped Loop Support in the Cydra 5. In Proceedings of the 3rd International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS-3), pages 26–38, 1989.

S. Jain. Circular Scheduling: A New Technique to Perform Software Pipelining. In Proceedings of the SIGPLAN 1991 conference on Programming Language Design and Implementation, pages 219–228, Jun 1991.

SangMin Shim and Soo-Mook Moon. Split-Path Enhnaced Pipeline Scheduling for Loops with Control Flows. In Proceedings of the 31st Annual ACM/IEEE International Symposium on Microarchitecture (Micro-31), pages 93–102, 1998.

B. Rau. Data Flow and Dependence Analysis for Instruction Level Parallelism. In Languages and Compilers for Parallel Computing, pages 236–250. MIT Press, 1994.

L. George and A. Appel. Iterated Register Coalescing. ACM Transactions on Programming Languages and Systems, 18(3):300–324, May 1996.

P. Briggs, K. Cooper, and L. Torczon. Improvements to Graph Coloring Register Allocation. ACM Transactions on Programming Languages and Systems, 16(3):428–455, May 1994.

S. Park, S. Shim, and S.-M. Moon. Evaluation of Scheduling Techniques on a SPARC-based VLIW Testbed. In Proceedings of the 30th Annual International Symposium on Microarchitecture, Dec 1997.

S.-M. Moon and K. Ebcioğlu. Performance Analysis of Tree VLIW Architecture for Exploiting Branch ILP in Non-Numerical Code. In Proceedings of the 1997 International Conference on Supercomputing, pages 301–308, New York, July 1997.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2000 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Kim, S., Moon, SM., Park, J., Yun, H. (2000). Unroll-Based Copy Elimination for Enhanced Pipeline Scheduling. In: Carter, L., Ferrante, J. (eds) Languages and Compilers for Parallel Computing. LCPC 1999. Lecture Notes in Computer Science, vol 1863. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-44905-1_6

Download citation

DOI: https://doi.org/10.1007/3-540-44905-1_6

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-67858-8

Online ISBN: 978-3-540-44905-8

eBook Packages: Springer Book Archive