Abstract

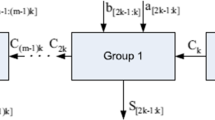

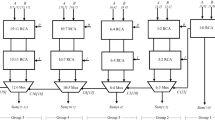

In this paper, several self-checking carry-propagate adders are examined and compared in terms of area integration, power dissipation and performance. Real-time detection of any single fault, permanent or transient, is ensured for all the presented circuits while the characteristics of each adder are illustrated. The results indicate that the characteristics of the adders change when safety mechanisms are applied. The constraints, also, of the required system design dictate the appropriate adder.

This work was supported by COSAFE project, ESPRIT 28593, ESD Design Cluster

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Mine, H., Koga, Y.: Basic Properties and a Construction Method for Fail-Safe Logical Systems, IEEE Trans. Electronic Computers, vol. 16, June 1967, 282–289

Kakaroudas, A. P., Papadomanolakis, K. S., Karaolis, E., Nikolaidis, S., Goutis, C. E.: Hardware/Power Requirements versus Fault Detection Effectiveness in Self-Checking Circuits, Proc. of Patmos’99, 387–396

Nicolaidis, M.: Fail-Safe Interfaces for VLSI: Theoritical Foundations and Implementation, IEEE Trans. On Comp., vol. 47, no. 1, January 1998, 62–77

Nikolos, D., Paschalis, A. M., Philokyprou, G.: Efficient Design of Totally Self-Checking Checkers for all Low-Cost Arithmetic Codes, IEEE Trans. On Comp., vol. 37, no. 7, July 1998, 807–814

Jha, N. K., Wang, S.: Design and Synthesis of Self-Checking VLSI Circuits, IEEE Trans. On CAD of Integr. Cir. And Syst., vol. 12, no. 6, June 1993

Duarte, R.O., Nicolaidis, M., Bederr, H., Zorian, Y.: Fault-Secure Shifter Design: Results and Implementations, 1997-European Design and Test Conference ED&TC, Paris, March 1997

Nicolaidis M., Duarte, R. O., Manich, S., Figueras, J.: Fault-Secure Parity Prediction Arithmetic Operators, IEEE Design & Test of Computers, April-June 1997, 60–71

Callaway, T. K., Swartzlander E.E., Jr.: The Power Consumption of CMOS Adders and Multipliers, Low-Power CMOS Design, IEEE Press, 1998, 218–224

Omondi, A. R., Computer Arithmetic Systems: algorithms, architecture, and implementation, Prentice Hall, 1994

Zervas, N., Theoharis, S., Soudris, D., Goutis, C.E., Thanailakis, A.: Generalized Low Power Design Flow, ESPRIT 25256 Deliverable Report LPGD/WP1/UP/D1.3R1, Jan.1999

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2000 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Kakaroudas, A.P., Papadomanolakis, K., Kokkinos, V., Goutis, C.E. (2000). Comparative Study on Self-Checking Carry-Propagate Adders in Terms of Area, Power and Performance. In: Soudris, D., Pirsch, P., Barke, E. (eds) Integrated Circuit Design. PATMOS 2000. Lecture Notes in Computer Science, vol 1918. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-45373-3_19

Download citation

DOI: https://doi.org/10.1007/3-540-45373-3_19

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-41068-3

Online ISBN: 978-3-540-45373-4

eBook Packages: Springer Book Archive