Abstract

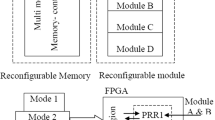

Field Programmable Gate Arrays (FPGAs) can be used to implement partial run-time reconfigurable (RTR) systems. A tool called PARBIT has been developed that transforms FPGA configuration bitstreams into partial bitstreams. With this tool it is possible to define a partial reconfigurable area inside the FPGA and download it into a specified region of the FPGA device. This paper presents PARBIT, the methodology used to design the partial RTR system, and three application examples.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Hutchings, B.L., Wirthlin, M.J.: Implementation approaches for reconfigurable logic applications. In Moore, W., Luk, W., eds.: Field-Programmable Logic and Applications (FPL’1995), Oxford, England, Springer-Verlag, Berlin (1995) 419–428

Hoang, D.T.: Searching genetic databases on splash 2. In Buell, D.A., Pocek, K.L., eds.: IEEE Workshop on FPGAs for Custom Computing Machines, Los Alamitos, CA, IEEE Computer Society Press (1993) 185–191

Bertin, P., Touati, H., Lagnese, E.: PAM programming environments: Practice and experience. In Buell, D.A., Pocek, K.L., eds.: IEEE Workshop on FPGAs for Custom Computing Machines, Los Alamitos, CA, IEEE Computer Society Press (1994) 133–138

Ditmar, J.M.: A Dynamically Reconfigurable FPGA-based Content Addressable Memory for IP Characterization. Master’s thesis, KTH-Royal Institute of Technology, Stockholm, Sweden (2000)

Hadley, J.D., Hutchings, B.L.: Designing a partially reconfigured system. In Schewel, J., ed.: Field Programmable Gate Arrays (FPGAs) for Fast Board Development and Reconfigurable Computing, Proc. SPIE 2607, Bellingham, WA, SPIE—The International Society for Optical Engineering (1995) 210–220

Ross, D., Vellacott, O., Turner, M.: An FPGA-based Hardware Accelerator for Image Processing. In Moore, W., Luk, W., eds.: More FPGAs: Proceedings of the 1993 International workshop on field-programmable logic and applications, Oxford, England (1993) 299–306

McMillan, S., Guccione, S.: Partial run-time reconfiguration using JRTR. In: Field-Programmable Logic and Applications / The Roadmap to Reconfigurable Computing (FPL’2000), Villach, Austria (2000) 352–360

Horta, E.L., Kofuji, S.T.: The architecture of a reconfigurable ATM switch (RECATS). In: Workshop de Computação Reconfigurável, Marília, SP, Brazil (2000)

Horta, E., Lockwood, J.W.: PARBIT: a tool to transform bitfiles to implement partial reconfiguration of field programmable gate arrays (FPGAs). Technical Report WUCS-01-13, Washington University in Saint Louis, Department of Computer Science (July 6, 2001)

Xilinx Inc.: Virtex-E 1.8V Field Programmable Gate Arrays. Xilinx DS022 (2001)

Carmichael, C.: Virtex configuration and readback. Xilinx XAPP138 (1999)

Xilinx Inc.: Configuration and readback of Virtex FPGAs using (JTAG) boundary scan. Xilinx XAPP139 (2000)

Taylor, D.E., Turner, J.S., Lockwood, J.W.: Dynamic Hardware Plugins (DHP): Exploiting reconfigurable hardware for high-performance programmable routers. In: IEEE OPENARCH 2001: 4th IEEE Conference on Open Architectures and Network Programming, Anchorage, AK (2001)

Lockwood, J.W., Naufel, N., Turner, J.S., Taylor, D.E.: Reprogrammable Network Packet Processing on the Field Programmable Port Extender (FPX). In: ACM International Symposium on Field Programmable Gate Arrays (FPGA’2001), Monterey, CA, USA (2001) 87–93

Horta, E.L., Kofuji, S.T., Martins, C.A.P.S.: (RECATS): A Reconfigurable ATM Switch Proposal. In: Workshop em Arquiteturas Reconfiguráveis-IX Simpósio Brasileiro de Arquiteturas de Computadores-Processamento de Alto Desempenho, Campos do Jordão, SP, Brazil (1997)

Katevenis, M., Serpanos, D., Vatsolaki, P.: ATLAS I: A General-Purpose, Single-Chip ATM Switch with Credit-Based Flow Control. In: Proceedings of the Hot Interconnects IV Symposium, Stanford, CA (1996) 63–73

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2002 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Horta, E.L., Lockwood, J.W., Kofuji, S.T. (2002). Using PARBIT to Implement Partial Run-Time Reconfigurable Systems. In: Glesner, M., Zipf, P., Renovell, M. (eds) Field-Programmable Logic and Applications: Reconfigurable Computing Is Going Mainstream. FPL 2002. Lecture Notes in Computer Science, vol 2438. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-46117-5_20

Download citation

DOI: https://doi.org/10.1007/3-540-46117-5_20

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-44108-3

Online ISBN: 978-3-540-46117-3

eBook Packages: Springer Book Archive