# A Fixed Point Homotopy Method for Efficient Time-Domain Simulation of Power Electronic Circuits

E. Chiarantoni<sup>1</sup>, G. Fornarelli<sup>1</sup>, S. Vergura<sup>1</sup>, T. Politi<sup>2</sup>

<sup>1</sup> Dipartimento di Elettrotecnica ed Elettronica, Politecnico di Bari, Via E. Orabona n° 4, 70125 Bari, Italy

chiarantoni@poliba.it, {fornarelli, verqura}@deemail.poliba.it

**Abstract.** The time domain analysis of switching circuits is a time consuming process as the change of switch state produces sharp discontinuities in switch variables. In this paper a method for fast time-domain analysis of switching circuits is described. The proposed method is based on piecewise temporal transient analysis windows joined by DC analysis at the switching instants. The DC analysis is carried out by means of fixed point homotopy to join operating points between consecutive time windows. The proposed method guarantees accurate results reducing of the number of iterations needed to simulate the circuit.

### 1 Introduction

Modern power electronic is characterized by an extensive use of non linear devices as diodes, BJTs, MOSFETs and IGBTs, in the role of power switches. From a mathematical point of view, these elements can pose severe limitations in the time domain simulation. The switches can be modeled in detail or in a simplified form. With detailed models the circuits become normal analog circuits and can be handled by standard commercial simulators based on various versions of the Berkley SPICE [1]. In this case the simulation is very accurate, but takes very long time. On the other hand, in many cases it is advantageous to use simplified models for the switches (nonlinear resistors) for example in the first stage of circuit design and generally when, during the switching, the exact values of the currents and voltages across the switches are not required. In these cases the simulation users do not need a very accurate simulation, but they prefer a very quick one.

When simplified models are used for the switches, at the switching instants the switch conductances change instantaneously their values of some orders of magnitude. To compute each time point solution of the transient analysis, the SPICE-like simulators adopt time point solution obtained by the Newton-Raphson method (NR) and the solution at the previous time step. The sudden changes of switch conductances produce numerical difficulties to join, using NR, two temporal instants since the problem becomes stiff. When a stiff problem occurs NR fails to converge and it starts

<sup>&</sup>lt;sup>2</sup> Dipartimento di Matematica, Politecnico di Bari, Via E. Orabona nº 4, 70125 Bari, Italy pptt@pascal.dm.uniba.it

again adopting a reduced time step to overcome the ill conditioned starting point. Hence very small time steps are used. For this reason, the iterations required by the simulation increase considerably and often even if a very little time step is adopted the simulation is stopped since the maximum number of iterations is exceeded.

To overcome this problem and to obtain fast simulations a big effort has been devoted and a new generation of Switch Mode Circuits analysis Methods (SMCM) (see [2], [3], [4], [5]) have been introduced.

To combine the advantages of simplified time analysis of SMCM and the efficiency of traditional simulators, in this paper we propose an hybrid approach to time domain analysis of switching circuits. The proposed method is based on piecewise temporal transient analysis windows joined by DC analysis at the switching instants. The switching instants are detected using a time-step analysis method while the DC analysis is carried out using fixed point homotopy. A great effort has been recently devoted to improve the performances of traditional simulators in the DC Analysis by means of homotopy methods (see [6], [7]) and global convergence results for Modified Nodal Equation (MNE) have been presented. The homotopy methods (also know as continuation methods) [10] are well know methods to solve convergence problems in NR equations when an appropriate starting point is unavailable.

These methods are based on a set of auxiliary equations to compute, with high efficiency, the solutions of nonlinear resistive circuits. In this paper it will be shown as the homotopy methods are useful also in transient analysis of switching circuits.

#### 2 **Time Domain Analysis of Electrical Circuits**

In the time domain transient analysis of electrical circuits, the modern simulators use the Modified Nodal method to build a set of Non-linear Differential Algebraic Equations (NDAEs). In the following we assume that the circuit consists of b passive elements, M of which produce the auxiliary equations (current controlled elements and independent voltages generators) and N+1 nodes. Moreover we assume that the circuit consists only of independent sources and voltage controlled current sources and, for the sake of simplicity, there are no loops consisting only of independent voltage sources and no cut-set consisting only of independent current sources. Using these elements we obtain a set of NDAEs of the form:

$$\mathbf{f}(\dot{\mathbf{x}}(t), \mathbf{x}(t), t) = 0 \tag{1}$$

where

$$\mathbf{x} = \begin{bmatrix} \mathbf{v} \\ \mathbf{i} \end{bmatrix} \in \mathfrak{R}^{N+M} \tag{2}$$

is the vector of the solutions, and  $\dot{\mathbf{x}}$  is its derivative respect to the time. In (2)  $\mathbf{v} \in \Re^N$ denotes the node voltages to the datum node and  $i \in \Re^M$  denotes the branch currents of voltages sources (independent and dependent) and inductors. Moreover, we assume that voltage and current variables are adopted, even if charge and flux are usually chosen in the numerical simulation for the numerical stability property (see [8], [9], [10]).

The equation (1) is solved using an integration method of variable step and variable order: Backward Euler, Trapezioidal or Gear formulae (see [9], [10], [11]). In the solution process, at each step of integration, after the discretization process, we obtain a set of Nonlinear Algebraic Equations (NAE) of the form:

$$\mathbf{f}(\mathbf{x}) = \mathbf{H}_{1}\mathbf{g}(\mathbf{H}_{1}^{T}\mathbf{x}) + \mathbf{H}_{2}\mathbf{x} + \mathbf{\acute{o}}$$

(3)

where  $\mathbf{g}: \mathfrak{R}^K \to \mathfrak{R}^K$  is a continuos function representing the relation between the branch voltages  $\mathbf{v}_b \in \mathfrak{R}^K$  and the branches currents  $\mathbf{i}_b \in \mathfrak{R}^K$ , excluding source branches, expressed as:

$$\mathbf{g}(\mathbf{v}_b, \mathbf{i}_b) = 0, \tag{4}$$

$\mathbf{H}_1$  is an  $n \times K$  constant matrix represented as:

$$\mathbf{H}_1 = \begin{bmatrix} \mathbf{D}_g \\ 0 \end{bmatrix} \tag{5}$$

and  $\mathbf{H}_2$  is an  $n \times n$  matrix represented as:

$$\mathbf{H}_2 = \begin{bmatrix} 0 & \mathbf{D}_E \\ \mathbf{D}_E^T & 0 \end{bmatrix} \tag{6}$$

where  $\mathbf{D}_g$  is an  $N \times K$  incidence matrix for the  $\mathbf{g}$  branches and  $\mathbf{D}_E$  is an  $N \times M$  reduced incidence matrix for the independent voltage sources branches. Moreover  $\mathbf{6} \in \mathbb{R}^n$  is the source vector that is represented as:

$$\begin{aligned}

\delta = \begin{bmatrix} \mathbf{J} \\ -\mathbf{E} \end{bmatrix} \end{aligned} \tag{7}$$

where  $\mathbf{J} \in \mathbb{R}^N$  is the current vector of the independent current sources and  $\mathbf{E} \in \mathbb{R}^M$  is the voltage vector of the independent voltage sources. From (2), (5), (6) and (7), equation (3) can be written as:

$$\mathbf{f}_{g}(\mathbf{x}) = \mathbf{D}_{g}\mathbf{g}(\mathbf{D}_{g}^{T}\mathbf{v}) + \mathbf{D}_{E}\mathbf{i} + \mathbf{J} = \mathbf{0}$$

(8a)

$$\mathbf{f}_{E}(\mathbf{v}) = \mathbf{D}_{E}^{T} \mathbf{v} - \mathbf{E} = \mathbf{0}.$$

(8b)

Equations (8) are usually solved adopting Newton-Raphson Method (NR), assuming as starting point the value of  $\mathbf{x}$  at the previous integration step. When NR iterations fail to converge, a reduced time step is adopted to obtain new coefficients for (8a) and (8b) and a new series of NR iterations is started.

All the modern simulators adopt switch models based on resistive elements. The constrain equation for the switch *j* is normally written as:

$$g_{sj} = \begin{cases} G_{ON} & \text{if } v_j \ge V_{ON} \\ G_{OFF} & \text{if } v_j < V_{OFF} \end{cases}$$

$$(9)$$

where  $g_{sj}$  is the switch conductance,  $G_{ON}$  and  $G_{OFF}$  are respectively the conductance of the switch in the closed and open conditions respectively. The two values have usually different orders of magnitude and cannot be singular  $(0 \text{ or } \infty)$ .  $V_{ON}$  and  $V_{OFF}$  are threshold voltages for OFF to ON and vice-versa. This element is normally inserted into the matrix g of (8a). In the transient analysis this element produces a sharp discontinuity in the associated variables (current into and voltage across the switch) and, as consequence, numerical difficulties in NR. In fact the solution at previous time step cannot be used to produce a new temporal solution, even if the time step is considerably reduced. This behavior depends on the stiffness of the equations.

To overcome the above problem the new simulators (e.g. Pspice-Orcad Rel. 9) use a more complex switch model in which the conductance is a more smooth differentiable function, but this precaution is often not sufficient. Hence, when strong discontinuities are present in the circuit variables, the variable stepsize methods produce a sequence of consecutive step size reductions which produce a global decrement in the time step required to simulate the whole circuit, therefore, a number of iterations increasing with the number of discontinuities, i.e., with the number of switching.

## 3 The Piecewise Temporal Window Approach

In the proposed approach, given a circuit to analyze using transient analysis, a standard simulation is started using a standard routine (the simulation core of a 3F5 version of SPICE [11]). The standard simulation is carried out until the solution at time  $t_2 = t_1 + \overline{\Delta}t$  requires 4 consecutive reductions of the time step (a time step control algorithm has been implemented);  $\overline{\Delta}t$  is the last tried time step and  $t_1$  the time of last solution found. If the above condition is met, the time step reduction routine is suspended, the solution at  $t_1$  is saved and a check on the values of variables at the time  $t_1 + \overline{\Delta}t$  is performed. We check if any switches result in inconsistent condition. A switch is in an inconsistent condition if the associated variables meet one of following conditions:

$$v_{j} \ge V_{ON} \text{ and } |V_{svj}| \ge \varepsilon$$

$$v_{j} \le V_{OFF} \text{ and } |I_{svj}| \ge \varepsilon$$

(10)

where  $\varepsilon$  is a small positive quantity and  $V_{swj}$ ,  $I_{swj}$  are respectively the voltage across and the current trough the j-th switch.

If an inconsistent condition is found on some switches, we remove this inconsistency imposing to zero the voltage across the switches ON and the current into switches OFF. A new solution is then obtained, using the DC analysis with Fixed Point Homotopy Method (FPH) in a resistive circuit obtained by the original circuit substituting the capacitors  $C_i$  and inductors  $L_i$  by independent voltages and current generators whose values are the voltages across the capacitors,  $V_{c_i}(t_1)$ , and the current in the inductors,  $I_{t_i}(t_1)$ , at time  $t_1$  and where all circuit parameters have the values of solution at time  $t_1$ , since the state of dynamic elements is unchanged between  $t_1$  and  $t_1 + \overline{\Delta}t$ .

The fixed point homotopy method is based on an auxiliary equation of the form:

$$\mathbf{h}(\mathbf{x},\alpha) = \alpha \mathbf{f}(\mathbf{x}) + (1-\alpha)\mathbf{A}(\mathbf{x} - \mathbf{x}^{0})$$

(11)

where  $\alpha \in [0,1]$  is the homotopy parameter and **A** is a non singular  $n \times n$  matrix. The solution curve of the homotopy equation:

$$\mathbf{h}(\mathbf{x},\alpha) = \mathbf{0} \tag{12}$$

is traced from the known solution  $(\mathbf{x}^0,0)$  at  $\alpha=0$  to the final solution  $(\mathbf{x}^*,1)$  at the  $\alpha=1$  hyperplane. In this case as starting point we consider the solution at time  $t_1$ ,  $\mathbf{x}^{t_1}$ , if the FPH converges, the solution  $\mathbf{x}^*$  is considered as bias point for the transient analysis at the time  $t_2=t_1+\overline{\Delta}t$ .

We assume that the resistive network associated to the circuit in the time  $t_1$  is characterized by Lipschitz continuous functions and satisfies the following condition of uniform passivity:

Definition 1: A continuous function  $\mathbf{g}:\mathfrak{R}^K\to\mathfrak{R}^K$  is said to be Uniformly Passive on  $\mathbf{v}_b^0$  if there exist a  $\gamma>0$  such that  $(\mathbf{v}_b-\mathbf{v}_b^0)^T(\mathbf{g}(\mathbf{v}_b)-\mathbf{g}(\mathbf{v}_b^0))\geq \gamma\|\mathbf{v}_b-\mathbf{v}_b^0\|^2$  for all  $\mathbf{v}_b\in\mathfrak{R}^K$ .

These assumptions usually hold for a fairly class of resistive circuits containing MOS, BJT's, diodes and positive resistors [12].

With the previous hypotheses the convergence conditions are the following:

- 1. The initial point  $\mathbf{x}^0$  is the unique solution of (3).

- 2. The solution curve starting from  $(\mathbf{x}^0,0)$  does not return to the same point  $(\mathbf{x}^0,0)$  for  $\alpha \neq 0$ .

- 3. There exists an  $\varepsilon > 0$  such that for all  $\mathbf{x} \in \{\mathbf{x} \in \mathfrak{R}^n | || \mathbf{x} || \ge \varepsilon \}$  and  $\alpha \in [0,1)$ ,  $\mathbf{h}(\mathbf{x},\alpha) \ne 0$  holds.

For the fixed point homotopy the conditions 1 and 2 always hold. Condition 3 is related to the structure of the circuit equations and to the structure of matrix  ${\bf A}$ . In this case we have chosen the following matrix:

$$\mathbf{A} = \begin{bmatrix} \mathbf{1}_N & \mathbf{0} \\ \mathbf{0} & -\mathbf{1}_M \end{bmatrix} . \tag{13}$$

In [6] the global convergence results preserved even for MNE have been shown using (13). Even if the convergence of the proposed method for a class of power electronic circuit is preserved, a problem in the homotopy implementation is the computational effort required to step the homotopy parameter in its definition range. The procedure to vary the homotopy parameter could significantly reduce the effectiveness of the method if compared with the standard integration method.

In the proposed approach a linear method has been utilized to obtain the value of the parameter  $\alpha_k$  for the k-th homotopy iteration:

$$\alpha_k = 0.1 \cdot k \quad k \in \mathbb{S}; \quad k \in [0, 10]; \quad (14)$$

The simulations have shown as this parameter is not critical and other choices could be satisfactory utilized.

The new trial solution is then used as starting point to compute the solution at time  $t_2$  in the suspended simulation. If the trial solution produce a solution without requiring a time step reduction in the integration routine, then the standard simulation is carried on. Otherwise we suspend the simulation and consider the circuit inconsistent.

In this way the DC analysis joints two switch cycles in succession, while during the switch cycle the transient analysis is not modified.

The proposed method avoids the iterations used by a standard simulation program to evaluate the switch variables during the switching. Finally, the time length of switch iterations is very short compared to switch cycle, therefore, the elimination of switching iterations does not yield any effect on the quality of final results.

## 4 Simulation and Comparison

To compare the aforesaid procedure with the standard simulators using the MNE, the method has been implemented modifying a kernel of the SPICE 3F5 source code [13], a new routine of time step reduction strategy has been added.

As example let us consider the transient analysis simulation of 2 ms on a standard buck converter with a power control element modeled by a switch internally driven. Figure 1 reports the values of the switch voltage  $V_{sw}$  (Fig. 1a) and switch current  $I_{sw}$  (Fig. 1b) as function of time, obtained by commercial simulation program, using the standard trapezoidal rule. The waveform are drawn between 0.945 ms and 0.963 ms of simulation.

We observe that the switch variables have sharp discontinuities. In particular when  $V_{sw}$  goes over 30 V there is the ON to OFF transition of the switch, while when  $V_{sw}$  goes above 30 V there is the OFF to ON transition. At the second transition we note a current pulse of  $I_{sw}$  (Fig. 1b). The switch current  $I_{sw}$  has been plotted in the range [0, 0.8] A.

**Fig. 1.** Voltage ( $V_{\rm SW}$  Fig. 1a) and current ( $I_{\rm SW}$  Fig. 1b) into switch in a period of simulation for the standard method.

The same circuit has been simulated adopting the proposed method. The simulation parameters and the time window are the same of the first case. Figure 2 reports again the values of  $I_{sw}$  and  $V_{sw}$  obtained. Comparing Figures 1 and 2 we note that the obtained waveforms are almost identical. The information lost is only about critical parameters of switches ( $I_{sw}$  pulse), but, during the commutation, the extreme values of current or voltage pulse across the switches depend essentially by the switch model, therefore, are not realistic and they are not very useful in our analysis. The variable  $I_{sw}$  is the most different in two methods. Therefore the main information about all circuit variables have been preserved.

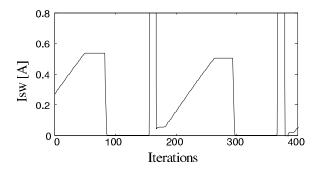

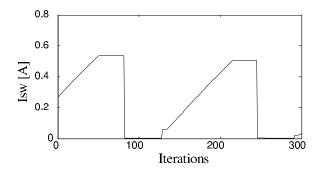

Figure 3 shows the values of the switch current  $I_{sw}$ , obtained by standard simulation program, with respect to iterates numerated from zero in previous time interval, while Figure 4 reports again  $I_{sw}$  with respect to iterates, obtained by proposed method.

If Figures 3 and 4 are compared it is easy to note the different number of iterates in switch cycle. In Figure 4 the calculation of a whole switch cycle need about 40% iterates less than the Figure 3. Moreover in these iterations the time-steps are very small.

In this simulation we have calculated the time steps distribution during the whole simulation time (2 ms). In the standard case a consistent number of iterations, about 65% is spent in very low time steps ( $T_s < 0.5\text{e-}9$ ).

**Fig. 2.** Voltage ( $V_{SW}$  fig. 2a) and current ( $I_{SW}$  fig. 2b) into switch in a period of simulation for the proposed method.

The most of these iterations are produced by switching instants, during the switching regions a lot of simulation time is spent to handle the discontinuities introduced by the adopted switch model. The proposed approach avoids the calculation of switching regions and allows the time step to preserve an high value in the whole simulation with a notable reduction of simulation time, in the proposed approach the time steps with  $T_s < 0.5$ e-9 are about 30%. The simulation time reduction clearly depends on the circuit analyzed, the computer used, the comparing method. In this example we obtained a reduction about 25% of simulation time.

## 5 Conclusions

In transient analysis of switching circuits a lot of simulation time is spent to analyze the commutations of the switches, when the switches are modeled by means of nonlinear resistors. In fact, the time steps of analysis program during the switching are very small compared to the time interval of analysis. In this paper has been proposed a method based on piecewise temporal transient analysis windows joined by DC analysis carry out by means of FPH at the switching instants. The proposed approach allows the elimination of the calculation of switching iterations.

**Fig. 3.** Current  $I_{sw}$  into switch in a period of simulation with respect to iterate, for the standard method.

**Fig. 4.** Current  $I_{sw}$  into switch in a period of simulation with respect to iterate, for the proposed method.

Comparing the results obtained by proposed method and the results obtained by a standard simulation program the tests give the reduction of the number of iterations between 30% and 50%, depending on the circuit to analyze. Moreover the proposed method guarantees accurate results as well as standard methods, in fact, we have shown the elimination of switching iterations does not yield any effect on the quality of final results. Finally, the simulation of power circuits is carried out adopting the same accurate models of the PSPICE libraries.

#### References

Nagel L. W., and Pederson D., SPICE: Simulation Program with Integrated Circuits Emphasis. Berkely, Calif.: Univ. Of California, Electronic Research Laboratory, Mwmorandum ERL-M382, Apr. 12, 1973

- Valsa J., and Vlach J.: SWANN-"A Programme for Analysis of switched Analogue Non-Linear Networks". International Journal of Circuits Theory and Applications, v. 23, 1995, pp. 369-379

- 3. Vlach J., Opal A.: Modern CAD methods for analysis of switched networks. IEEE Trans. CAS, vol. 44, 1997, pp. 759-762

- Weeks W. T., Jimenez A. J., Mahoney G. W., Metha D., Quassemzadeh H., and Scott T. R.: Algorithms for ASTAP – A Network-Analysis Program. IEEE Trans. Circuit Theory, v. CT-20, Nov. 1973, pp. 628-634

- Vlach J., Woiciechowski J. M., Opal A.: Analysis of Nonlinear Networks with Inconsistent Inizial Condicions. IEEE Trans. On Circuit and Systems-I, Vol. 42, No. 4, April 1995

- Yamamura K., Sekiguchi T., Inoue Y.: A Fixed-Point Homotopy Method for Solving Modified Nodal Equations. IEEE Trans. On Circuits and Systems-I, Vol. 46, No. 6, June 1999, pp. 654-665

- 7 Yamamura K., Sekiguchi T., Inoue Y.: A globally convergent algorithm using the fixed-point homotopy for solving modified nodal equations, in Proc. Int. Symp. Nonolinear Theory Applications, Kochi, Japan, Oct. 1996, pp. 463-466

- 8. J. Ogrodzki: Transient Analysis of circuits with ideal switches using charge and flux substitute networks. Proc. Intl. Conf. Electr. Circ. Syst., Lisboa, Portugal, 1998

- J. Ogrodzki, M. Skowron: The charge-flux method in simulation of first kind switched circuits. Proc. European Conference on Circuit Theory and Design, ECCTD'99, Stresa, Italy, pp. 475-478

- 10. J. Ogrodzki: Circuit simulation methods and algorithms. Bosa Ranton, Florida:CRC, 1994

- R. Kielkowski. Inside Spice. McGraw-Hill New York, 1998

- T. Ohtsuki, T. Fujisawa and S. Kumagai: Existence theorems and a solution algorithm for solving resistive circuits. Int. J. Circuit Theory Appl., vol. 18, pp.443-474, Sept. 1990

- 13. http://ieee.ing.uniroma1.it/ngspice/