Abstract

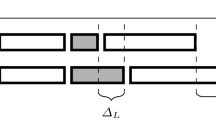

We extend a set of algebraic tools for representing microprocessors to model superscalar microprocessor implementations, and apply them to a case study. We develop existing correctness models to accommodate the more advanced timing relationships of superscalar processors, and consider formal verification. We illustrate our tools and techniques with an in-depth treatment of an example superscalar implementation. We use clocks to divide time into (not necessarily equal) segments, defined by the natural timing of the computational process of a device. We formally relate clocks by surjective, monotonic maps called retimings. In the case of superscalar microprocessors, the normal relationship between ‘architectural time’ and ‘implementation time’ is complicated by the fact that events that are distinct in time at the architectural level can occur simultaneously at the implementation level

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

T Arora, T Leung, K Levitt, T Schubert, and P Windley. Report on the UCD microcoded Viper verification project. In Higher-Order Logic Theorem Proving and its Applications, pages 239–252. Lecture Notes in Computer Science 780, Springer-Verlag, 1993.

D. W. Anderson, F. J. Sparacio, and R. M. Tomasulo. The IBM System/ 360 model 91: Machine philosophy and instruction handling. IBM Journal of Research and Development, 11:8–24, January 1967.

J Burch and D Dill. Automatic verification of pipelined microprocessor control. In D Dill, editor, Proceedings of the 6th International Conference, CAV'94: Computer-Aided Verification, pages 68–80. Lecture Notes in Computer Science 818, Springer-Verlag, 1994.

G Birtwistle and B Graham. Verifying SECD in HOL. In J Staunstrup, editor, Formal Methods for VLSI Design, pages 129–177. North-Holland, 1990.

B Bose and S D Johnson. DDD-FM9001: Derivation of a verified microprocessor. In L Pierre G Milne, editor, Correct Hardware Design and Verification Methods, pages 191–202. Lecture Notes in Computer Science 683, Springer-Verlag, 1993.

M Bickford and M Srivas. Verification of a pipelined processor using Clio. In M Leeser and G Brown, editors, Proceedings of the Mathematical Sciences Institute Workshop on Hardware Specifcation, Verification and Synthesis: Mathematical Aspects, pages 307–332. Lecture Notes in Computer Science 408, Springer-Verlag, 1990.

J Burch. Techniques for verifying superscalar microprocessors. In Design Automation Conference, 1996.

A Cohn. A proof of correctness of the Viper microprocessor: the first levels. In G Birtwistle and P A Subrahmanyam, editors, VLSI Specification, Verification and Synthesis, pages 27–72. Kluwer Academic Publishers, 1987.

D Cyrluk, J Rushby, and M Srivas. Systematic formal verification of interpreters. In IEEE International Conference on Formal Engineering Methods (ICFEM’97, pages 140–149, 1997.

W J Cullyer. Implementing safety critical systems: the Viper microprocessor. In G Birtwistle and P A Subrahmanyam, editors, VLSI Specification, Verification, and Synthesis, pages 1–26. Kluwer Academic Publishers, 1987.

D Cyrluk. Inverting the abstraction mapping: A methodology for hardware verification. In A Camilleri M Srivas, editor, Formal Methods in Computer-Aided Design, pages 172–186. Lecture Notes in Computer Science 1166, Springer-Verlag, 1996.

A C J Fox and N A Harman. An algebraic model of correctness for superscalar microprocessors. In Formal Methods in Computer-Aided Design, pages 346–361. Lecture Notes in Computer Science 1166, Springer-Verlag, 1996.

A C J Fox and N A Harman. Algebraic models of correctness for microprocessors. Technical Report CSR 8-98, University of Wales Swansea, 1998.

A C J Fox. Algebraic Representation of Advanced Microprocessors PhD thesis, Department of Computer Science, University of Wales Swansea, 1998.

M J C Gordon and T F Melham. Introduction to HOL. Cambridge University Press, 1993.

M J C Gordon. Proving a computer correct with the LCF-LSM hardware verification system. Technical report, Technical Report No. 42, Computer Laboratory, University of Cambridge, 1983.

B Graham. The SECD Microprocessor: a Verification Case Study. Kluwer, 1992.

G.F. Grohoski. Machine organisation of the IBM RISC System/6000 processor. IBM Journal of Research and Development, 34:37–58, January 1990.

N A Harman. Formal Specifications for Digital Systems. PhD thesis, School of Computer Studies, University of Leeds, 1989.

J L Hennessy and D A Patterson. Computer Architecture: A Quantative Approach. Morgan Kaufman, 1996.

N A Harman and J V Tucker. The formal specification of a digital correlator I: Abstract user specification. In K McEvoy and J V Tucker, editors, Theoretical Foundations for VLSI Design, pages 161–262. Cambridge University Press Tracts in Theoretical Computer Science 10, 1990.

N A Harman and J V Tucker. Algebraic models and the correctness of microprocessors. In L Pierre G Milne, editor, Correct Hardware Design and Verification Methods. Lecture Notes in Computer Science 683, Springer-Verlag, 1993.

N A Harman and J V Tucker. Algebraic models of microprocessors: Architecture and organisation. Acta Informatica, 33:421–456, 1996.

N A Harman and J V Tucker. Algebraic models of microprocessors: the verification of a simple computer. In V Stavridou, editor, Proceedings of the 1995 IMA Conference on Mathematics for Dependable Systems. Oxford University Press, 1997.

W A Hunt. Microprocessor design verification. Journal of Automated Reasoning, 5(4):429–460, 1989.

W Hunt. A formal HDL and its use in the FM9001 verification. In C A R Hoare and M Gordon, editors, Mechanized Reasoning in Hardware Design. Prentice-Hall, 1992.

W Hunt. FM8501: A Verified Microprocessor. Lecture Notes on Artificial Intelligence 795, Springer Verlag, 1994.

M Johnson. Superscalar microprocessor design. Prentice Hall, Englewood Cliffs, N. J., 1991.

J Joyce. Formal verification and implementation of a microprocessor. In G Birtwistle and P A Subrahmanyam, editors, VLSI Specification, Verification and Synthesis, pages 129–159. Kluwer Academic Publishers, 1987.

P Landin. On the mechanical evaluation of expressions. Computer Journal, 6:308–320, 1963.

T F Melham. Higher Order Logic and Hardware Verification. Cambridge University Press Tracts in Theoretical Computer Science 31, 1993.

S Miller and M Srivas. Formal verification of an avionics microprocessor. Technical report, SRI International Computer Science Laboratory CSL-95-04, 1995.

S Miller and M Srivas. Formal verification of the AAMP5 microprocessor: a case study in the industrial use of formal methods. In Proceedings of WIFT 95, Boca Raton, 1995.

S Owre, J Rushby, N Shankar, and M Srivas. A tutorial on using PVS. In Proceedings of TPCD 94, pages 258–279. Lecture Notes in Computer Science 901, Springer-Verlag, 1994.

M Srivas and M Bickford. Formal verification of a pipelined microprocessor. IEEE Software, 7(5):52–64, 1991.

J Su, D Dill, and C Barrett. Automatic generation of invariants in processor verification. In A Camilleri M Srivas, editor, Formal Methods in Computer-Aided Design, pages 377–388. Lecture Notes in Computer Science 1166, Springer-Verlag, 1996.

J. E. Smith and G. S. Sohi. The microarchitecture of superscalar processors. In Proceedings of the IEEE, volume 83, pages 1609–1624, December 1995.

V Stavridou. Formal Specification of Digital Systems. Cambridge University Press Tracts in Theoretical Computer Science 37, 1993.

K Stephenson. An Algebraic Approach to Syntax, Semantics and Compilation. PhD thesis, University of Wales Swansea Computer Science Department, 1996.

K Stephenson. Algebraic specification of the Java virtual machine. In B Möller and J V Tucker, editors, Prospects for Hardware Foundations. Lecture Notes in Computer Science 1546, Springer-Verlag, 1998.

H S Stone. High Performance Computer Architecture. Addison-Wesley, 1993.

J. E. Thornton. Parallel operation in the Control Data 6600. In Proceedings of the Fall Joint Computer Conference, volume 26, pages 33–40, 1961.

J. E. Thornton. Design of a Computer — The Control Data 6600. Glenview, IL: Scott, Foresman and Co., 1970.

R. M. Tomasulo. An eficient algorithm for exploiting multiple arithmetic units. IBM Journal of Research and Development, pages 176–188, January 1967.

P Windley and J Burch. Mechanically checking a lemma used in an automatic verification tool. In A Camilleri M Srivas, editor, Formal Methods in Computer-Aided Design, pages 362–376. Lecture Notes in Computer Science 1166, Springer-Verlag, 1996.

P Windley and M Coe. A correctness model for pipelined microprocessors. In Proceedings of the 2nd Conference on Theorem Provers in Circuit Design, 1994.

P Windley. A theory of generic interpreters. In L Pierre G Milne, editor, Correct Hardware Design and Verification Methods, pages 122–134. Lecture Notes in Computer Science 683, Springer-Verlag, 1993.

S. Weiss and J. E. Smith. Instruction issue logic in pipelined supercomputers. IEEE Transactions on Computers, c-33(11):1013–1022, November 1984.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1998 Springer-Verlag Berlin Heidelberg

About this chapter

Cite this chapter

Fox, A.C.J., Harman, N.A. (1998). Algebraic Models of Superscalar Microprocessor Implementations: a Case Study. In: Möller, B., Tucker, J.V. (eds) Prospects for Hardware Foundations. Lecture Notes in Computer Science, vol 1546. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-49254-2_5

Download citation

DOI: https://doi.org/10.1007/3-540-49254-2_5

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-65461-2

Online ISBN: 978-3-540-49254-2

eBook Packages: Springer Book Archive