Abstract

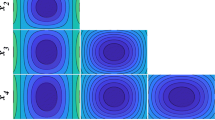

In this paper we present a novel placement algorithm for FPGAs. This algorithm is based upon the self-organizing map used in unsupervised learning algorithms for artificial neural networks performing pattern classification. The self-organizing map is used to map the connectivity of the design to a two dimensional regular mesh topology. This is followed by simple compaction to minimize wire costs.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Kohonen,T.: The Self Organizing Map. Proceedings of the IEEE. Vol. 78 No. 9 (1990) pp.1464–1480.

McClelland,J.L., Rumelhart D.E.: Explorations in Parallel Distributed Processing. MIT Press (1988).

Kirkpatrick S., Gelatt C.D., Veechi M.P.: Optimization by simulated annealing. Science 220 (1983) pp. 671–680.

Xilinx, The Programmable gate Array Data Book, Xilinx 1991.

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 1993 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Blight, D.C., McLeod, R.D. (1993). Self-organizing Kohonen maps for FPGA placement. In: Grünbacher, H., Hartenstein, R.W. (eds) Field-Programmable Gate Arrays: Architecture and Tools for Rapid Prototyping. FPL 1992. Lecture Notes in Computer Science, vol 705. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-57091-8_33

Download citation

DOI: https://doi.org/10.1007/3-540-57091-8_33

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-57091-2

Online ISBN: 978-3-540-47902-4

eBook Packages: Springer Book Archive