Abstract

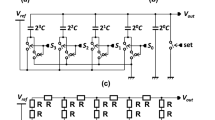

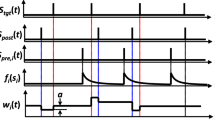

Two-quadrant multipliers are required for several neural network architectures. The efficient implementation of these architectures in silicon requires the development of small, compact, reliable and accurate hardware multipliers. This paper details simulation and hardware results for the DYnamic Mirror PuLsed Experimental Synapse (DYMPLES) Chip. DYMPLES is an analogue current mode chip which utilises dynamic current mirrors and current matching to implement two quadrant multiplication based on the pulse stream approach[1]. HSPICE simulations indicate that the DYMPLES circuits produce excellent current matching and this is reinforced by the hardware results.

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

HAMILTON, A., MURRAY, A. F., BAXTER D. J., CHURCHER, S., REEKIE, H. M., and TARASSENKO, L.: ‘Integrated pulse-stream neural networks — results, issues and pointers', IEEE Transactions on Neural Networks, Vol. 3, No. 3, 1992, pp. 385–93.

LIPPMANN, R. P.: ‘An introduction to computing with neural nets', IEEE ASSP Magazine, 1987, Vol. 4, pp. 4–22.

VERLEYSEN, M., THISSEN, P., VOZ, J-L., and MADRENAS, J.: ‘An analog processor architecture for a neural network classifier', IEEE Micro, Vol. 14, No. 3, June 1994, pp. 16–28.

VITTOZ, E. A., and WEGMANN, G.: ‘Dynamic current mirrors’ in TOUMAZOU, C., LIDGEY, F. J., and HAIGH, D. G. (Eds.), ‘Analogue IC design: the current-mode approach’ (Peter Peregrinus Ltd., London, 1990), pp.297–326.

HAMILTON, A.: 'synaptic weight representation in pulsed neural network VLSI: Voltage or Current ?', Proc. of Int. Conf. on Neural Information Processing, Seoul 1994, pp.353–8.

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 1995 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Mayes, D.J., Hamilton, A., Louvet, J.E. (1995). A VLSI current mode synapse chip. In: Mira, J., Sandoval, F. (eds) From Natural to Artificial Neural Computation. IWANN 1995. Lecture Notes in Computer Science, vol 930. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-59497-3_255

Download citation

DOI: https://doi.org/10.1007/3-540-59497-3_255

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-59497-0

Online ISBN: 978-3-540-49288-7

eBook Packages: Springer Book Archive