Abstract

The paper shows how iterative parametric sequential circuits, which are most relevant in practice, can be verified fully automatically. Key observation is that monadic second-order logic on strings provides an adequate level for hardware specification and implementation. This allows us to apply the corresponding decision procedure and counter-model generator implemented in the Mona verification tool, which, for the first time, yields ‘push-button’ verification, and error detection and diagnosis for the considered class of circuits. As illustrated by means of various versions of counters, this approach captures hierarchical and mixed mode verification, as well as the treatment of varying connectivity in iterative designs.

Chapter PDF

Similar content being viewed by others

Keywords

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

References

M. Allemand: “Formal verification of characteristic properties: Proc. TPCD'94 (Theorem Provers in Circuit Design — Theory, Practice, and Experience), Bad Herrenhalb (D), Sept.'94, LNCS N. 901, pp. 292–297.

C. Angelo, L. Claesen, H. De Man: “A Methodology for Proving Correctness of parameterized hardware Modules in HOL”, Proc. CHDL'91, Marseille (F), April 1991, IFIP Transactions, North-Holland, pp.63–82.

D. Basin, N. Klarlund: “Hardware verification using monadic second-order logic”, Proc. CAV '95, Liège (B), July 1995, LNCS N. 939, Springer Verlag, pp. 31–41.

D. Basin, P. DelVecchio: “Verification of combinational logic in Nuprl”, In “Hardware Specification, Verification and Synthesis: Mathematical Aspects”, Ithaca, New York, 1989. Springer-Verlag.

M. Barbacci, G. Barnes, R. Cattell, D. Siewiorek: “The ISPS Computer Description Language”, Tech. Rep. CMU-CS-79-137, Carnegie-Mellon University, Computer Science Department, Aug. 1979.

D. Borrione, C. Le Faou: “Overview of the CASCADE multi-level hardware description language and its mixed-mode simulation mechanisms”, Proc. 7th Int. Conf. on Computer Hardware Description Languages (CHDL'85), Tokyo (Japan), Aug. 1985.

M. Browne, E. Clarke, O. Grumberg: “Reasoning about networks with many identical finite state processes”, Information and Computation, 81(1), Apr. 1989, pp. 13–31.

A. Camilleri, M. Gordon, T. Melham: “Hardware verification using higher-order logic”, In D. Borrione (ed.), “From HDL Descriptions to Guaranteed Correct Circuit Designs”, pages 43–67. Elsevier Science Publishers B. V. (North-Holland), 1987.

A. Church: “Logic, arithmetic and automata”, Proc. Int. Congr. Math., Almqvist and Wiksells, Uppsala 1963, pp. 23–35.

R. L. Constable et al.: “Implementing Mathematics with the Nuprl Proof Development System”, Prentice-Hall, Englewood Cliffs, NJ, 1986.

H. Eveking: “Axiomatizing Hardware Description Languages”, Int. Journal of VLSI Design, 2(3), pp. 263–280, 1990.

“Databook of Analog and Synchronous Components”, Fairchild —1993.

A. de Geus: “High Level design: A design vision for the '90s,” Proc. IEEE Int. Conf. on Computer Design, p.8, 1992.

M. Gordon: “Why higher-order logic is a good formalism for specifying and verifying hardware”, In G. J. Milne and P. A. Subrahmanyam, editors, “Formal Aspects of VLSI Design”, North-Holland, 1986.

A. Gupta, A. Fisher: “Parametric Circuit Representation Using Inductive Boolean Functions,” Proc. CAV'93, Elounda (GR), June 1993, LNCS N. 697, pp. 15–28.

F.K. Hanna, N. Daeche: “Specification and verification using higher-order logic: a case study”, In G.J. Milne and P.A. Subrahmanyam, editors, “Formal Aspects of VLSI Design”, pp. 179–213. Elsevier, 1986.

W. Hunt: “Microprocessor design verification”, Journal of Automated Reasoning, 5(4):429–460, 1989.

J. Henriksen, J. Jensen, M. JØrgensen N. Klarlund, R. Paige, T. Rauhe, A. Sandholm: “Mona: Monadic second-order logic in practice”, Proc. of TACAS'95, Aarhus (DK), May 1995, LNCS 1019, Springer Verlag, pp. 89–110.

Z. Kohavi: “Switching and finite automata theory”, Computer Science Series, McGraw Hill, New York, NY (USA), 1970.

R. Kurshan, K. McMillan: “A structural induction theorem for processes”, Proc. 8th ACM PODC Symposium, Edmonton (CAN), Aug. 1989, pp. 239–247.

IEEE: “Standard VHDL Language Reference Manual”, 1988, IEEE Std. 1076–1987.

T. Margaria, M. Mendler: “Automatic Treatment of Sequential Circuits in Second-Order Monadic Logic”, 4th GI/ITG/GME Worksh. on Methoden des Entwurfs und der Verifikation digitaler Systeme, Kreischa (D), March 1996, Shaker Verlag.

T. Margaria: “First-Order theories for the verification of complex FSMs”, Aachener Informatik-Berichte Nr. 91-30, RWTH-Aachen, Dec. 1991.

T. Margaria: “Efficient RT-Level Verification by Theorem Proving”, IFIP World Congr.'92, Madrid (E), Sept. 1992, North-Holland pp. 696–702.

T. Margaria: “Verifica formale della correttezza del progetto di sistemi digitali”, Dissertazione di Dottorato (in Italian), Politecnico di Torino, Turin (I), Feb. 1993.

T. Margaria, B. Steffen: “Distinguishing Formulas for Free”, EDAC-EUROASIC'93: IEEE European Design Automation Conference, Paris (France), February 1993.

T. Melham: “Using recursive types of reasoning about hardware in higher order logic”, In Int. Working Conf. on The Fusion of Hardware Design and Verification, pp. 26–49, July 1988.

L. Pierre: “The Formal Proof of the “Min-max” sequential benchmark described in CASCADE using the Boyer-Moore theorem prover,” Proc. IMEC-IFIP Worksh. on Applied Formal Methods for Correct VLSI Design, Leuven (B), Nov. 1989, pp. 129–149.

L. Pierre: “An Automatic Generalization Method for the Inductive Proof of Replicated and Parallel Architectures”, Proc. TPCD'94, Bad Herrenhalb (D), Sept.'94, LNCS N. 901, pp. 72–91.

J.K Rho, F. Somenzi: “Inductive Verification for Iterative circuits”, Proc. DAC'92, Anaheim (CA), June 1992, pp. 628–633.

J.K Rho, F. Somenzi: “Automatic Generation of Network Invariants for the verification of Iterative sequential Systems”, Proc. CAV'93, Elounda (GR), June 1993, LNCS N. 697, pp. 123–137.

A. Sistla, S. German: “Reasoning with many processes”, Proc. LICS'97, Ithaca, NY, June 1987, pp. 138–152.

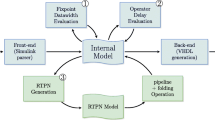

B. Steffen, T. Margaria, A. Cla\en. “The META-Frame: An Environment for Flexible Tool Management”, Proc. TAPSOFT'95, Aarhus (Denmark), May 1995, LNCS N. 915, Springer Verlag.

W. Thomas: “Automata on infinite objects”, In J. van Leeuwen, editor, Handbook of Theoretical Computer Science, vol. B, p. 133–191. MIT Press/Elsevier, 1990.

P. Wolper: “Expressing interesting properties of programs in propositional temporal logic”, Proc. POPL'86, St. Petersburg, Jan. 1986, pp. 184–192.

P. Wolper, V. Lovinfosse: “Verifying properties of large sets of processes with network invariants”, Proc. Automatic Verification Methods for Finite Systems, LNCS 407, Springer Verlag, 1989, pp 68–80.

Author information

Authors and Affiliations

Editor information

Rights and permissions

Copyright information

© 1996 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Margaria, T. (1996). Fully automatic verification and error detection for parameterized iterative sequential circuits. In: Margaria, T., Steffen, B. (eds) Tools and Algorithms for the Construction and Analysis of Systems. TACAS 1996. Lecture Notes in Computer Science, vol 1055. Springer, Berlin, Heidelberg. https://doi.org/10.1007/3-540-61042-1_49

Download citation

DOI: https://doi.org/10.1007/3-540-61042-1_49

Published:

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-61042-7

Online ISBN: 978-3-540-49874-2

eBook Packages: Springer Book Archive