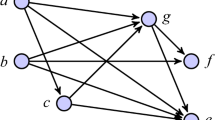

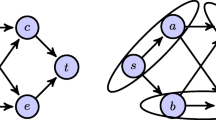

Modern design requirements have brought additional complexities to netlists and layouts. Millions of components, whitespace resources, and fixed/movable blocks are just a few to mention in the list of complexities.With these complexities in mind, placers are faced with the burden of finding an arrangement of placeable objects under strict wirelength, timing, and power constraints. In this chapter, we describe the architecture and novel details of our high quality, large-scale analytical placer APlace2 (and the subsequent APlace3) [26–28]. The performance of APlace2, has been recognized in the recent ISPD-2005 placement contest, and in this paper we disclose many of the technical details that we believe are key factors to its performance. We describe (1) a new clustering architecture, (2) a dynamically adaptive analytical solver, and (3) better legalization schemes and novel detailed placement methods. We also provide extensive experimental results on a number of benchmark sets, including the IBM ISPD’04, IBM-PLACE 2.0, ICCAD’04, ISPD’05, PEKO’05, ISPD’06, PEKO’06 as well as using the zero-change netlist transformation benchmarking framework.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

S. N. Adya, S. Chaturvedi, J. A. Roy, D. A. Papa and I. L. Markov, “Unification of Partitioning, Placement and Floorplanning,” in Proc. IEEE International Conference on Computer-Aided Design, 2004, pp. 550-557

A. R. Agnihotri, S. Ono, C. Li, M. C. Yildiz, A. Khatkhate, C.-K. Koh and P. H. Madden, “Mixed Block Placement via Fractional Cut Recursive Bisection,” IEEE Transactions on Computer-Aided Design, vol. 24(5), 2005

A. Agnihotri, S. Ono and P. Madden, “Recursive Bisection Placement: Feng Shui 5.0 Implementation Details,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 230-232

A. Agnihotri, M. Yildiz, A. Khatkhate, A. Mathur, S. Ono and P. Madden, “Fractional Cut: Improved Recursive Bisection Placement,” in Proc. IEEE International Conference on Computer-Aided Design, 2003, pp. 307-310

C. Alpert, A. Kahng, G.-J. Nam, S. Reda and P. Villarrubia, “A Semi-Persistent Clustering Technique for VLSI Circuit Placement,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 200-207

C. J. Alpert, J. H. Huang and A. B. Kahng, “Multilevel Circuit Partitioning,” in Proc. ACM/IEEE Design Automation Conference, 1997, pp. 530-533

U. Brenner, A. Pauli and J. Vygen, “Almost Optimum Placement Legalization by Minimum Cost Flow and Dynamic Programming,” in Proc. ACM/IEEE International Symposium on Physical Design, 2004, pp. 2-9

U. Brenner and J. Vygen, “Faster Optimal Single-Row Placement with Fixed Ordering,” in Proc. Design, Automation and Test in Europe, 2000, pp. 117-121

A. E. Caldwell, A. B. Kahng and I. L. Markov, “Optimal Partitioners and End-Case Placers for Standard-Cell Layout,” in Proc. ACM/IEEE International Symposium on Physical Design, 1999, pp. 90-96

A. E. Caldwell, A. B. Kahng and I. L. Markov, “Can Recursive Bisection Alone Produce Routable Placements?” in Proc. ACM/IEEE Design Automation Conference, 2000, pp. 477-482

T. F. Chan, J. Cong, T. Kong and J. R. Shinnerl, “Multilevel Optimization for Large-Scale Circuit Placement,” in Proc. IEEE International Conference on Computer-Aided Design, 2000, pp. 171-176

T. F. Chan, J. Cong, M. Romesis, J. R. Shinnerl, K. Sze and M. Xie, “mPL6: A Robust Multilevel Mixed-Size Placement Engine,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 227-229

T. F. Chan, J. Cong and K. Sze, “Multilevel Generalized Force-directed Method for Circuit Placement,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 185-192

T.-C. Chen, T.-C. Hsu, Z.-W. Jiang and Y.-W. Chang, “NTUplace: A Ratio Partitioning Based Placement Algorithm for Large-Scale Mixed-Size Designs,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 236-238

K. Doll, F. Johannes and K. Antreich, “Iterative Placement Improvement by Network Flow Methods,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 13(10), pp. 1189-1200, 1994

H. Eisenmann and F. M. Johannes, “Generic Global Placement and Floorplanning,” in Proc. ACM/IEEE Design Automation Conference, 1998, pp. 269-274

S. Goto, “An Efficient Algorithm for the Two-Dimensional Placement Problem in Electrical Circuit Layout,” IEEE Transactions on Circuits and Systems, vol. 28(1), pp. 12-18, 1981

D. Hill, “Method and System for High Speed Detailed Placement of Cells Within an Integrated Circuit Design,” US Patent 6370673, 2001

B. Hu and M. Marek-Sadowska, “Fine Granularity Clustering-Based Placement,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 23(4), pp. 527-536, 2004

B. Hu, Y. Zeng and M. Marek-Sadowska, “mFAR: Fixed-Points-Addtion-Based VLSI Placement Algorithm,” Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 239-241

A. B. Kahng, I. Markov and S. Reda, “On Legalization of Row-Based Placements,” in Proc. IEEE Great Lakes Symposium on VLSI, 2004, pp. 214-219

A. B. Kahng and Q. Wang, “Implementation and Extensibility of an Analytic Placer,” in Proc. ACM/IEEE International Symposium on Physical Design, 2004, pp. 18-25

A. B. Kahng and S. Reda, “Zero-Change Netlist Transformations: A New Technique for Placement Benchmarking,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 25(121), pp. 2806-2819, 2006

A. B. Kahng and S. Reda, “An Analytic Placer for Mixed-Size Placement and TimingDriven Placement,” in Proc. IEEE International Conference on Computer-Aided Design, 2004, pp. 565-572

A. B. Kahng, P. Tucker and A. Zelikovsky, “Optimization of Linear Placements for Wirelength Minimization with Free Sites,” in Proc. IEEE Asia and South Pacific Design Automation Conference, 1999, pp. 241-244

A. B. Kahng and Q. Wang, “Implementation and Extensibility of an Analytic Placer,” IEEE Transactions on Computer-Aided Design 24(5) (2005), pp. 734-747

A. B. Kahng, S. Reda, and Q. Wang, “APlace: A General Analytic Placement Framework,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 233-235

A. B. Kahng, S. Reda, and Q. Wang, “Architecture and Details of a High Quality, LargeScale Analytical Placer,” in Proc. International Conference Computer-Aided Design, 2005, pp. 891-898

A. B. Kahng and X. Xu, “Accurate Pseudo-Constructive Wirelength and Congestion Estimation,” in Proc. ACM International Workshop on System-Level Interconnect Prediction, 2003, pp. 61-68

A. A. Kennings and I. L. Markov, “Analytical Minimization of Half-Perimeter Wirelength”, Proc. IEEE/ACM Asia and South Pacific Design Automation Conference, Jan. 2000, pp. 179-184

G. Karypis, R. Aggarwal, V. Kumar and S. Shekhar, “Multilevel hypergraph partitioning: Application in VLSI domain,” in Proc. ACM/IEEE Design Automation Conference, 1997, pp. 526-529

G. Karypis and V. Kumar, “Multilevel k -way hypergraph partitioning,” in Proc. ACM/IEEE Design Automation Conference, 1999, pp. 343-348

A. Khatkhate, C. Li, A. R. Agnihotri, M. C. Yildiz, S. Ono, C.-K. Koh and P. H. Madden, “Recursive Bisection Based Mixed Block Placement,” in Proc. ACM/IEEE International Symposium on Physical Design, 2004, pp. 84-89

C. Li, M. Xie, C.-K. Koh, J. Cong and P. H. Madden, “Routability-Driven Placement and White Space Allocation,” in Proc. IEEE International Conference on Computer-Aided Design, 2004, pp. 394-401

G.-J. Nam, “ISPD 2006 Placement Contest: Benchmark Suite and Results,” in Proc. ACM/IEEE International Symposium on Physical Design, 2006, pp. 167-167

G.-J. Nam, C. Alpert, P. Villarrubia, B. Winter and M. Yildiz, “The ISPD2005 Placement Contest and Benchmark Suite,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 216-219

W. Naylor, “Non-Linear Optimization System and Method for Wire Length and Delay Optimization for an Automatic Electric Circuit Placer,” US Patent 6301693, 2001

B. Obermeier, H. Ranke and F. M. Johannes, “Kraftwerk - A Versatile Placement Approach,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 242-244

J. A. Roy, D. A. Papa, S. N. Adya, H. H. Chan A. N. Ng, J. F. Lu and I. L. Markov, “Capo: Robust and Scalable Open-Source Min-Cut Floorplacer,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 224-226

C. Sechen and K. W. Lee, “An Improved Simulated Annealing Algorithm for Row-Based Placement,” in Proc. IEEE International Conference on Computer-Aided Design, 1987, pp. 478-481

G. Sigl, K. Doll and F. M. Johannes, “Analytical Placement: A Linear or a Quadratic Objective Function?,” in Proc. ACM/IEEE Design Automation Conference, 1991, pp. 427-431

W.-J. Sun and C. Sechen, “Efficient and Effective Placement for Very Large Circuits,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 14(5), pp. 349-359, 1995

T. Taghavi, X. Yang, B. K. Choi, M. Wang and M. Sarrafzadeh, “DRAGON2005: LargeScale Mixed-Size Placement Tool,” in Proc. ACM/IEEE International Symposium on Physical Design, 2001, pp. 245-247

N. Viswanathan and C. Chu, “FastPlace: Efficient Analytical Placement Using Cell Shifting, Iterative Local Refinement and a Hybrid Net Model,” in Proc. ACM/IEEE International Symposium on Physical Design, 2004, pp. 26-33

N. Viswanathan and C. Chu, “FastPlace: An Analytical Placer for Mixed-Mode Designs,” in Proc. ACM/IEEE International Symposium on Physical Design, 2005, pp. 221-223

J. Vygen, “Algorithms for Large-Scale Flat Placement,” in Proc. ACM/IEEE Design Automation Conference, 1997, pp. 746-751

J. Vygen, “Algorithms for Detailed Placement of Standard Cells,” in Design, Automation and Test in Europe, 1998, pp. 321-324

M. Wang, X. Yang and M. Sarrafzadeh, “DRAGON2000: Standard-Cell Placement Tool for Large Industry Circuits,” in Proc. IEEE International Conference on Computer-Aided Design, 2001, pp. 260-263

X. Yang, B.-K. Choi and M. Sarrafzadeh, “Routability Driven White Space Allocation for Fixed-Die Standard-Cell Placement,” in Proc. ACM/IEEE International Symposium on Physical Design, 2002, pp. 42-47

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2007 Springer Science+Business Media, LLC

About this chapter

Cite this chapter

Kahng, A.B., Reda, S., Wang, Q. (2007). APlace: A High Quality, Large-Scale Analytical Placer. In: Nam, GJ., Cong, J. (eds) Modern Circuit Placement. Series on Integrated Circuits and Systems. Springer, Boston, MA. https://doi.org/10.1007/978-0-387-68739-1_7

Download citation

DOI: https://doi.org/10.1007/978-0-387-68739-1_7

Publisher Name: Springer, Boston, MA

Print ISBN: 978-0-387-36837-5

Online ISBN: 978-0-387-68739-1

eBook Packages: EngineeringEngineering (R0)