Abstract

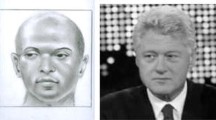

Ever-growing IoT demands big data processing and cognitive computing on mobile and battery operated devices. However, big data processing on low power embedded cores is challenging due to their limited communication bandwidth and on-chip storage. Additionally, IoT and cloud-based computing demand low overhead security kernel to avoid data breaches. In this chapter, we present, “SENSE”, Sketching and Encryption on Scalable heterogeneous Engine for data reduction and encryption. SENSE is a heterogeneous framework which consists of three important kernels: 1. sketching module for data reduction, 2. an accelerator for efficient sketch recovery using scalable and parallel reconstruction architecture and 3. a host processor to perform post processing. SENSE framework can reduce data up to 67% with 3.81 dB signal-to-reconstruction error rate (SRER). One of the critical challenges in big data processing on embedded hardware platforms is to reconstruct the sketched data in real-time with stringent constraints on error bounds and hardware resources. We explore Orthogonal Matching Pursuit (OMP) algorithm for sketch data recovery. OMP is a greedy algorithm with high computational complexity which has emerged as an important tool for signal recovery, dictionary learning and sparse data classification. We use a domain specific many-core hardware named Power Efficient Nano Cluster (PENC) designed by EEHPC lab at University of Maryland, Baltimore County. To demonstrate efficiency of SENSE framework, we integrate it with Hadoop MapReduce platform for face detection application. The full hardware integration consists of tiny ARM cores which perform task scheduling and application processing, while PENC acts as an accelerator for sketch reconstruction. We show performance of SENSE framework on face identification application.

This work is an extended version of the paper LESS: Big data sketching and Encryption on low power platform [1] and Low Overhead CS-Based Heterogeneous Framework for Big Data Acceleration [2].

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

Notes

- 1.

PENC many-core platform is developed by EEHPC lab at University of Maryland Baltimore County, USA, Web: http://eehpc.csee.umbc.edu/.

- 2.

For convenience to explain overview of the framework, we selected row and column size to be same. In real-time streaming data can be of different column and row sizes.

References

Kulkarni, A., Shea, C., Homayoun, H., Mohsenin, T.: LESS: big data sketching and encryption on low power platform. In: 2017 Design, Automation Test in Europe Conference Exhibition (DATE) (2017)

Kulkarni, A., et al.: Low overhead CS-based heterogeneous framework for big data acceleration. In: Proceedings of the ACM Transactions Embedded Computing System 17, 1, Article 25 (2017), 25 pages, GLSVLSI ’16, pp. 57–62. ACM (2017)

Kulkarni, A., et al.: CS-based secured big data processing on FPGA. In: 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pp. 201–201 (2016)

Rouhani, B., et al.: Sketch: An automated framework for streaming sketch-based analysis of big data on fpga. In: 2015 IEEE 23rd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pp. 187–194 (2015)

Mirhoseini, A., et al.: Perform-ml: performance optimized machine learning by platform and content aware customization. In: Proceedings of the 53rd Annual Design Automation Conference, DAC ’16, pp. 20:1–20:6. ACM, New York, NY, USA(2016)

Kulkarni, A.M., Homayoun, H., Mohsenin, T.: A parallel and reconfigurable architecture for efficient OMP compressive sensing reconstruction. In: Proceedings of the 24th Edition of the Great Lakes Symposium on VLSI, GLSVLSI ’14, 299–304. ACM, New York, NY, USA (2014)

Kulkarni, A., Jafari, A., Sagedy, C., Mohsenin, T.: Sketching-based high-performance biomedical big data processing accelerator. In: 2016 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1138–1141 (2016)

Candès, E., Wakin, M.: An introduction to compressive sampling. Signal Process. Mag. IEEE 25(2), 21–30 (2010)

Tropp, J., Gilbert, A.: Signal recovery from random measurements via orthogonal matching pursuit. IEEE Trans. Inf. Theory 53(12), 4655–4666 (2007)

Needell, D., Vershynin, R.: Signal recovery from incomplete and inaccurate measurements via regularized orthogonal matching pursuit. IEEE J. Select. Topics Signal Process. 4(2), 310–316 (2010)

Korde, A., Bradley, D., Mohsenin, T.: Detection performance of radar compressive sensing in noisy environments. In: International SPIE Conference on Defense, Security, and Sensing (2013)

Tropp, J., Gilbert, A.: Signal recovery from random measurements via orthogonal matching pursuit. IEEE Trans. Inf. Theory 53(12), 4655–4666 (2007)

Kulkarni, A., Mohsenin, T.: Accelerating compressive sensing reconstruction OMP algorithm with CPU, GPU, FPGA and domain specific many-core. In: 2015 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 970–973 (2015). https://doi.org/10.1109/ISCAS.2015.7168797

Page, A., Attaran, N., Shea, C., Homayoun, H., Mohsenin, T.: Low-power manycore accelerator for personalized biomedical applications. In: Proceedings of the 26th Edition on Great Lakes Symposium on VLSI, (GLSVLSI ’16), pp. 63–68. ACM, New York, NY, USA. 978-1-4503-4274-2 (2016). https://doi.org/10.1145/2902961.2902986

Kulkarni, A., Pino, Y., Mohsenin, T.: Adaptive real-time Trojan detection framework through machine learning. In: 2016 IEEE International Symposium on Hardware Oriented Security and Trust, (HOST ’16), May 2016, pp. 120–123 (2016)

Kulkarni, A., et al.: Low energy sketching engines on many-core platform for big data acceleration. In: Proceedings of the 26th Edition on Great Lakes Symposium on VLSI, GLSVLSI ’16, pp. 57–62. ACM (2016)

Bianchi, T.: Analysis of one-time random projections for privacy preserving compressed sensing. IEEE Trans. Inf. Forens. Sec. 11(2), 313–327 (2016)

Martinez, A., Benavente, R.: The AR face database. In: CVC Technical Report #24 (1998)

Jain, V., Learned-miller, E.: FDDB: a benchmark for face detection in unconstrained settings. Technical Report (2010)

Apache kernel description (2016). http://www.apache.org/

Viola, P., Jones, M.: Rapid object detection using a boosted cascade of simple features. In: Proceedings of the 2001 IEEE Computer Society Conference on Computer Vision and Pattern Recognition, 2001. CVPR 2001, vol. 1, pp. I–511–I–518 (2001)

Girshick, R.: Fast r-cnn. In: The IEEE International Conference on Computer Vision (ICCV) (2015)

Haar Feature-based Cascade Classifier for Object Detection. http://docs.opencv.org/. Accessed 2 Feb 2016

Lienhart, R., Kuranov, A., Pisarevsky, V.: Pattern Recognition: 25th DAGM Symposium, Magdeburg, Germany, September 10–12, 2003. Proceedings. Chapter Empirical Analysis of Detection Cascades of Boosted Classifiers for Rapid Object Detection, pp. 297–304. Springer, Berlin, Heidelberg (2003)

Sinha, P., Balas, B., Ostrovsky, Y., Russell, R.: Face recognition by humans: nineteen results all computer vision researchers should know about. Proc. IEEE 94(11), 1948–1962 (2006)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Switzerland AG

About this chapter

Cite this chapter

Kulkarni, A., Mohsenin, T. (2019). SENSE: Sketching Framework for Big Data Acceleration on Low Power Embedded Cores. In: Chakraborty, R., Mathew, J., Vasilakos, A. (eds) Security and Fault Tolerance in Internet of Things. Internet of Things. Springer, Cham. https://doi.org/10.1007/978-3-030-02807-7_10

Download citation

DOI: https://doi.org/10.1007/978-3-030-02807-7_10

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-02806-0

Online ISBN: 978-3-030-02807-7

eBook Packages: EngineeringEngineering (R0)