Abstract

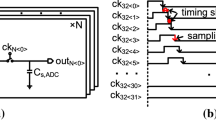

We present a novel encoder design for FPGA-based Time-to-Digital Converters (TDCs) that use tapped delay lines. The encoder is the most challenging and problematic unit on such measurement devices. Recent developments in TDC methodology include the Wave Union principle, and encoders based on population count. These two methods can alleviate fundamental disadvantages of FPGA-based TDCs. However, it appeared to be problematic to combine the two methods. The contribution of this paper is a special arithmetic unit that allows us to combine these two methods into a fast and compact encoder.

The paper is a report on work in progress, real-world measurement results cannot be given at this point in time.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Horstmann, M.: Picosecond TDC Design. Ecole de microélectronique 2017 de l’IN2P3, Paris, 14–19 May 2017

Lattice Semiconductor: ECP5 and ECP5-5G Family Data Sheet. FPGA-DS-02012 Version 1.9, March 2018

Liu, C., Wang, Y.: A 128-channel, 710 M samples/second, and less than 10 ps RMS resolution time-to-digital converter implemented in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 62(3), 773–783 (2015)

Uǧur, C., Korcyl, G., Michel, J., Penschuk, M., Traxler, M.: 264 channel TDC platform applying 65 channel high precision (7.2 psRMS) FPGA based TDCs. In: 2013 IEEE Nordic-Mediterranean Workshop on Time-to-Digital Converters, Perugia, Italy, 3 Oct 2013 (2013)

Wang, Y., Kuang, J., Liu, C., Cao, Q.: A 3.9-ps RMS precision time-to-digital converter using ones-counter encoding scheme in a Kintex-7 FPGA. IEEE Trans. Nucl. Sci. 64(10), 2713–2718 (2017)

Wu, J., Shi, Z.: The 10-ps wave union TDC: improving FPGA TDC resolution beyond its cell delay. In: IEEE Nuclear Science Symposium, Dresden, Germany, 19–25 Oct 2008 (2008)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Switzerland AG

About this paper

Cite this paper

Knittel, G. (2019). A Novel Encoder for TDCs. In: Hochberger, C., Nelson, B., Koch, A., Woods, R., Diniz, P. (eds) Applied Reconfigurable Computing. ARC 2019. Lecture Notes in Computer Science(), vol 11444. Springer, Cham. https://doi.org/10.1007/978-3-030-17227-5_4

Download citation

DOI: https://doi.org/10.1007/978-3-030-17227-5_4

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-17226-8

Online ISBN: 978-3-030-17227-5

eBook Packages: Computer ScienceComputer Science (R0)