Abstract

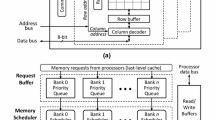

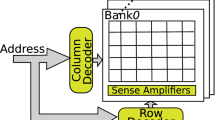

Mixed-criticality systems integrate tasks with various levels of criticality onto the same hardware platform. Critical tasks require tight bounding of worst case latency at any cost, yet for non-critical tasks it is important to provide high performance as much as possible. In this paper, we take workload-driven approach and propose a novel workload-aware DRAM controller design for mixed-criticality system that can successfully achieve both of the conflicting demands in the presence of memory-intensive workloads. By using bank partitioning and request batching with prioritization, we provide tighter worst case latency bound for critical tasks and high performance and fairness for non-critical tasks. Our evaluation shows that the design achieves maximum 18% of performance improvement.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Akesson, B., Goossens, K.: Architectures and modeling of predictable memory controllers for improved system integration. In: 2011 Design, Automation Test in Europe. pp. 1–6, March 2011. https://doi.org/10.1109/DATE.2011.5763145

Burns, A., Davis, R.: Mixed criticality systems-a review. Department of Computer Science, University of York, Technical Reports (2013)

Ecco, L., Tobuschat, S., Saidi, S., Ernst, R.: A mixed critical memory controller using bank privatization and fixed priority scheduling. In: 2014 IEEE 20th International Conference on Embedded and Real-Time Computing Systems and Applications, pp. 1–10, August 2014. https://doi.org/10.1109/RTCSA.2014.6910550

Goossens, S., Kuijsten, J., Akesson, B., Goossens, K.: A reconfigurable real-time sdram controller for mixed time-criticality systems. In: 2013 International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), pp. 1–10, September 2013. https://doi.org/10.1109/CODES-ISSS.2013.6658989

Henning, J.L.: SPEC CPU2006 benchmark descriptions. SIGARCH Comput. Archit. News 34(4), 1–17 (2006). https://doi.org/10.1145/1186736.1186737

Jacob, B., Ng, S., Wang, D.: Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann Publishers Inc., San Francisco (2007)

Kim, H., Broman, D., Lee, E.A., Zimmer, M., Shrivastava, A., Oh, J.: A predictable and command-level priority-based dram controller for mixed-criticality systems. In: 21st IEEE Real-Time and Embedded Technology and Applications Symposium, pp. 317–326, April 2015. https://doi.org/10.1109/RTAS.2015.7108455

Kim, H., de Niz, D., Andersson, B., Klein, M., Mutlu, O., Rajkumar, R.: Bounding memory interference delay in cots-based multi-core systems. In: 2014 IEEE 19th Real-Time and Embedded Technology and Applications Symposium (RTAS), pp. 145–154, April 2014. https://doi.org/10.1109/RTAS.2014.6925998

Kim, Y., Papamichael, M., Mutlu, O., Harchol-Balter, M.: Thread cluster memory scheduling: exploiting differences in memory access behavior. In: 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture, pp. 65–76, December 2010. https://doi.org/10.1109/MICRO.2010.51

Liu, L., Cui, Z., Li, Y., Bao, Y., Chen, M., Wu, C.: BPM/BPM+: software-based dynamic memory partitioning mechanisms for mitigating dram bank-/channel-level interferences in multicore systems. ACM Trans. Archit. Code Optim. (TACO) 11(1), 5 (2014)

Liu, L., Cui, Z., Xing, M., Bao, Y., Chen, M., Wu, C.: A software memory partition approach for eliminating bank-level interference in multicore systems. In: Proceedings of the 21st International Conference on Parallel Architectures and Compilation Techniques, pp. 367–376. ACM (2012)

Mancuso, R., Pellizzoni, R., Caccamo, M., Sha, L., Yun, H.: WCET(m) estimation in multi-core systems using single core equivalence. In: 2015 27th Euromicro Conference on Real-Time Systems, pp. 174–183, July 2015. https://doi.org/10.1109/ECRTS.2015.23

Mutlu, O., Moscibroda, T.: Parallelism-aware batch scheduling: enhancing both performance and fairness of shared dram systems. In: Proceedings of the 35th Annual International Symposium on Computer Architecture, ISCA 2008, pp. 63–74. IEEE Computer Society, Washington (2008). https://doi.org/10.1109/ISCA.2008.7

Reineke, J., Liu, I., Patel, H.D., Kim, S., Lee, E.A.: Pret dram controller: bank privatization for predictability and temporal isolation. In: 2011 Proceedings of the Ninth IEEE/ACM/IFIP International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS), pp. 99–108, October 2011. https://doi.org/10.1145/2039370.2039388

Rixner, S.: Memory controller optimizations for web servers. In: Proceedings of the 37th Annual IEEE/ACM International Symposium on Microarchitecture, MICRO 37, pp. 355–366. IEEE Computer Society, Washington (2004). https://doi.org/10.1109/MICRO.2004.22

Rixner, S., Dally, W.J., Kapasi, U.J., Mattson, P., Owens, J.D.: Memory access scheduling. In: Proceedings of the 27th Annual International Symposium on Computer Architecture, ISCA 2000, pp. 128–138. ACM, New York (2000). https://doi.org/10.1145/339647.339668

Snavely, A., Tullsen, D.M.: Symbiotic jobscheduling for a simultaneous multithreaded processor. In: Proceedings of the Ninth International Conference on Architectural Support for Programming Languages and Operating Systems, ASPLOS IX, pp. 234–244. ACM, New York (2000). https://doi.org/10.1145/378993.379244

Xie, M., Tong, D., Huang, K., Cheng, X.: Improving system throughput and fairness simultaneously in shared memory cmp systems via dynamic bank partitioning. In: 2014 IEEE 20th International Symposium on High Performance Computer Architecture (HPCA), pp. 344–355, February 2014. https://doi.org/10.1109/HPCA.2014.6835945

Yun, H., Mancuso, R., Wu, Z.P., Pellizzoni, R.: PALLOC: DRAM bank-aware memory allocator for performance isolation on multicore platforms. In: 2014 IEEE 19th Real-Time and Embedded Technology and Applications Symposium (RTAS), pp. 155–166, April 2014. https://doi.org/10.1109/RTAS.2014.6925999

Yun, H., Pellizzon, R., Valsan, P.K.: Parallelism-aware memory interference delay analysis for cots multicore systems. In: 2015 27th Euromicro Conference on Real-Time Systems, pp. 184–195, July 2015. https://doi.org/10.1109/ECRTS.2015.24

Zhou, Y., Wentzlaff, D.: MITTS: memory inter-arrival time traffic shaping. In: Proceedings of the 43rd International Symposium on Computer Architecture, ISCA 2016, pp. 532–544. IEEE Press, Piscataway (2016). https://doi.org/10.1109/ISCA.2016.53

Acknowledgement

This research was partly supported by the MSIT (Ministry of Science and ICT), Korea, under the SW Starlab (IITP-2015-0-00209) supervised by the IITP (Institute for Information & Communications Technology Promotion) and partly supported by Next-Generation Information Computing Development Program through the National Research Foundation of Korea (NRF) funded by the MSIT (2017M3C4A7065925, On-the-fly Machine Learning and Its Specialized Real-time/Security System SW for Evolving Intelligent CPS).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Switzerland AG

About this paper

Cite this paper

Eo, J., Kim, KW., Lee, CG. (2019). Memory Access Pattern-Aware DRAM Controller Design for Mixed-Criticality Systems. In: Chamberlain, R., Taha, W., Törngren, M. (eds) Cyber Physical Systems. Design, Modeling, and Evaluation. CyPhy 2017. Lecture Notes in Computer Science(), vol 11267. Springer, Cham. https://doi.org/10.1007/978-3-030-17910-6_3

Download citation

DOI: https://doi.org/10.1007/978-3-030-17910-6_3

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-17909-0

Online ISBN: 978-3-030-17910-6

eBook Packages: Computer ScienceComputer Science (R0)