Abstract

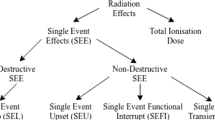

The electronics devices that operate in the extreme space environment require a high grade of reliability in order to mitigate the effect of the ionizing particles. For COTS components this can be achieved using fault-tolerant design techniques which allow such design to fulfil the space mission requirements. This paper presents the design and the implementation of one of the Klessydra F03x microcontroller soft core family, called the F03_mini, which is a RISC-V RV32I compatible fault-tolerant architecture enhanced by a Hardware Thread (HART) full/partial protection and a thread-controlled Watch-Dog Timer module. The core architecture has been synthesized and implemented on an ARTIX-7 A35 FPGA and fault-injection by the meaning of a functional RTL simulation has been performed in order to evaluate the robustness to Single Event Effects (SEE). Experimental results are provided, illustrating the impact and the benefits obtained by the usage of the proposed TMR protection techniques as well as a thread-controlled Watch-Dog Timer.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

ESA-ESTEC (2016) Space product assurance—techniques for radiation effects mitigation in ASICs and FPGAs handbook. ECSS-Q-HB-60-02A

RISC-V User-Level ISA Specification v2.2, Online: https://riscv.org/specifications/

RISC-V Privileged ISA Specification v1.10, Online: https://riscv.org/specifications/privileged-isa/

Gupta S, Gala N, Madhusudan G, Kamakoti V (2015) SHAKTI-F: a fault tolerant microprocessor architecture. In: IEEE 24th Asian test symposium

Blasi L, Mastrandrea A, Menichelli F, Olivieri M (2018) A space-rated soft IP-core compatible with the PIC® hardware architecture and instruction set. Adv Astronaut Sci 163:581–594

PULP Platform, Open hardware, the way it should be!, Online: https://pulp-platform.org/

Klessydra Processing Core Family Technical Manualv8, 2019. Online: http://github.com/klessydra

Cheikh A, Sordillo S, Mastrandrea A, Menichelli F, Olivieri M (2019) Efficient mathematic accelerator design coupled with an interleaved multi-threading RISC-V microprocessor. In: Applications in electronics pervading industry, environment and society. ApplePies

Cheikh A, Cerutti G, Mastrandrea A, Menichelli F, Olivieri M (2019) The microarchitecture of a multi-threaded RISC-V compliant processing core family for IoT end-nodes. In: Applications in electronics pervading industry, environment and society. ApplePies 2017. Lecture Notes in Electrical engineering, vol 512. Springer, Berlin

Olivieri M, Cheikh A, Cerutti G, Mastrandrea A, Menichelli F (2017) Investigation on the optimal pipeline organization in RISC-V multi-threaded soft processor cores. In: 2017 New Generation of CAS (NGCAS), Genova

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 Springer Nature Switzerland AG

About this paper

Cite this paper

Blasi, L., Vigli, F., Cheikh, A., Mastrandrea, A., Menichelli, F., Olivieri, M. (2020). A RISC-V Fault-Tolerant Microcontroller Core Architecture Based on a Hardware Thread Full/Partial Protection and a Thread-Controlled Watch-Dog Timer. In: Saponara, S., De Gloria, A. (eds) Applications in Electronics Pervading Industry, Environment and Society. ApplePies 2019. Lecture Notes in Electrical Engineering, vol 627. Springer, Cham. https://doi.org/10.1007/978-3-030-37277-4_59

Download citation

DOI: https://doi.org/10.1007/978-3-030-37277-4_59

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-37276-7

Online ISBN: 978-3-030-37277-4

eBook Packages: Physics and AstronomyPhysics and Astronomy (R0)