Abstract

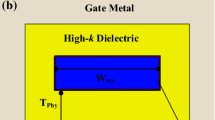

This paper presents optimization of drain/source extension length of 5 nm node Nano-sheet Transistor (NSHT) using a fully-calibrated TCAD platform. A 12 nm extension length shows a 49.5% increase in ION/IOFF compared to NSHT with a 5 nm extension length. For the extension lengths longer than 12 nm, ION/IOFF begins degrading. SHEs effects are worse for higher supply voltages (VDD). An increase in VDD from 0.7 V to 1.5 V results in a 50.89% increase in peak lattice temperature for the NSHT. Also, at VDD = 1.5 V, the ON current (ION) degrades by 12.27% when SHEs are considered. Finally, the effect of different spacer dielectric materials on SHEs is studied for the optimized NSHT device. The ION degradations of 11.73%, 10.68%, and 12.27% are observed for HfO2, Si3N4, and SiO2, respectively. The use of spacer dielectric with larger thermal conductivity is observed as a possible remedy to tackle the ION degradation.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Loubet, N., et al.: T17–5 (late news ) stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET T230 T231. VLSI Technol. 2017(5), 14–15 (2017)

Yakimets, D., et al.: Power aware FinFET and lateral nano-sheet FET targeting for 3nm CMOS technology. Technical Digest International Electron Devices Meeting. IEDM, pp. 20.4.1–20.4.4 (2018). https://doi.org/10.1109/IEDM.2017.8268429

Seon, Y., Chang, J., Yoo, C., Jeon, J.: Device and circuit exploration of multi-nanosheet transistor for sub-3 nm technology node. Electron 10, 1–14 (2021). https://doi.org/10.3390/electronics10020180

Yoon, J.S., Jeong, J., Lee, S., Baek, R.H.: Systematic DC/AC performance benchmarking of sub-7-nm node FinFETs and nanosheet FETs. IEEE J. Electron Devices Soc. 6, 942–947 (2018). https://doi.org/10.1109/JEDS.2018.2866026

Young, C.D., et al.: Critical discussion on (100) and (110) orientation dependent transport: nMOS planar and FinFET. Digest of Technical Papers - Symposium on VLSI Technology, pp. 18–19 (2011)

Pundir, Y.P., Saha, R., Pal, P.K.: Effect of gate length on performance of 5nm node N-channel nano-sheet transistors for analog circuits. Semicond. Sci. Technol. 36 (2020). https://doi.org/10.1088/1361-6641/abc51e

Jang, D., et al.: Device exploration of nanosheet transistors for Sub-7-nm technology node. IEEE Trans. Electron Devices. 64, 2707–2713 (2017). https://doi.org/10.1109/TED.2017.2695455

Yoon, J.S., Jeong, J., Lee, S., Baek, R.H.: Optimization of nano-sheet number and width of multi-stacked nano-sheet FETs for sub-7-nm node system on chip applications. Jpn. J. Appl. Phys. 58 (2019). https://doi.org/10.7567/1347-4065/ab0277

Liu, R., Li, X., Sun, Y., Shi, Y.: A vertical combo spacer to optimize electro-thermal characteristics of 7-nm nanosheet gate-all-around transistor. IEEE Trans. Electron Devices. 67, 2249–2254 (2020). https://doi.org/10.1109/TED.2020.2988655

Prasad, C.: A review of self-heating effects in advanced CMOS technologies. IEEE Trans. Electron Devices. 66, 4546–4555 (2019). https://doi.org/10.1109/TED.2019.2943744

Kim, H., Son, D., Myeong, I., Kang, M., Jeon, J., Shin, H.: Analysis on self-heating effects in three-stacked nanoplate FET. IEEE Trans. Electron Devices. 65, 4520–4526 (2018). https://doi.org/10.1109/TED.2018.2862918

Cai, L., Chen, W., Du, G., Zhang, X., Liu, X.: Layout design correlated with self-heating effect in stacked nanosheet transistors. IEEE Trans. Electron Devices. 65, 2647–2653 (2018). https://doi.org/10.1109/TED.2018.2825498

Yoon, J.S., Jeong, J., Lee, S., Baek, R.H.: Multi-Vth strategies of 7-nm node nanosheet FETs with limited nanosheet spacing. IEEE J. Electron Devices Soc. 6, 861–865 (2018). https://doi.org/10.1109/JEDS.2018.2859799

Pundir, Y.P., Bisht, A., Saha, R., Pal, P.K.: Effect of temperature on performance of 5-nm node silicon nanosheet transistors for analog applications. SILICON (2022). https://doi.org/10.1007/s12633-022-01800-w

Synopsys: Sentaurus Device User Guide. (2019)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Bisht, A., Pundir, Y.P., Pal, P.K. (2022). Electro-Thermal Analysis of Vertically Stacked Gate All Around Nano-sheet Transistor. In: Shah, A.P., Dasgupta, S., Darji, A., Tudu, J. (eds) VLSI Design and Test. VDAT 2022. Communications in Computer and Information Science, vol 1687. Springer, Cham. https://doi.org/10.1007/978-3-031-21514-8_12

Download citation

DOI: https://doi.org/10.1007/978-3-031-21514-8_12

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-21513-1

Online ISBN: 978-3-031-21514-8

eBook Packages: Computer ScienceComputer Science (R0)