Abstract

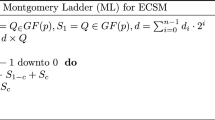

Elliptic curve cryptography (ECC) is one of the most popular asymmetric key cryptography techniques used in secured data communications. The scalar multiplication is the most expensive operation in the ECC. In this paper, we propose a low cost hardware for scalar multiplication in Affine coordinates based ECC. Here, we use a reconfigurable Galois field (GF) arithmetic circuit, which performs various GF arithmetic operations such as addition, multiplication, inverse, and fused multiply add (FMA) using a same set of hardware circuit. Instead of using a number of multipliers and adders in point addition/doubling, we have used only one reconfigurable GF arithmetic circuit. The existing and proposed designs are implemented in 45 nm CMOS technology using Cadence. The synthesis results show that the affine co-ordinate based proposed \(GF(2^{163})\) scalar multiplier achieves \(69\%\) of reduction in the switching power dissipation as compared with the Lopez-Dahab projective co-ordinates based conventional design in 45 nm CMOS technology.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Mohamed Asan Basiri, M., Shukla, S.K.: Hardware optimization for crypto implementation. In: IEEE International Symposium on VLSI Design and Test, pp. 1–6 (2016). https://doi.org/10.1109/ISVDAT.2016.8064877a

López, J., Dahab, R.: Fast multiplication on elliptic curves over GF(2m) without precomputation. In: Koç, Ç.K., Paar, C. (eds.) CHES 1999. LNCS, vol. 1717, pp. 316–327. Springer, Heidelberg (1999). https://doi.org/10.1007/3-540-48059-5_27

Hong, J., Wu, W.: The design of high performance elliptic curve cryptographic. In: 52nd IEEE International Midwest Symposium on Circuits and Systems, pp. 527–530 (2009). https://doi.org/10.1109/MWSCAS.2009.5236038

Ansari, B., Wu, H.: Efficient finite field processor for \(GF(2^{163})\) and its VLSI implementation. In: Fourth IEEE International Conference on Information Technology, pp. 1–6 (2007). https://doi.org/10.1109/ITNG.2007.83

Venugopal, E., Hailu, T.: FPGA based architecture of elliptic curve scalar multiplication for IOT. In: IEEE International Conference on Emerging Devices and Smart Systems, pp. 178–182 (2018). https://doi.org/10.1109/ICEDSS.2018.8544305

Ansari, B., Hasan, M.A.: High performance architecture of elliptic curve scalar multiplication. IEEE Trans. Comput. 57(11), 1443–1453 (2008)

Zhang, Y., Chen, D., Choi, Y., Chen, L., Ko, S.: A high performance pseudo-multi-core ECC processor over \(GF(2^{163})\). In: IEEE International Symposium on Circuits and Systems, pp. 701–704 (2010). https://doi.org/10.1109/ISCAS.2010.5537486

Li, L., Li, S.: High-performance pipelined architecture of elliptic curve scalar multiplication over \(GF(2^m)\). IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(4), 1223–1232 (2016)

Rashid, M., Hazzazi, M.M., Khan, S.Z., Alharbi, A.R., Sajid, A., Aljaedi, A.: A novel low-area point multiplication architecture for elliptic-curve cryptography. Electronics 10(2698), 1–16 (2021)

Song, L., Parhi, K.K.: Low-energy digit-serial/parallel finite field multipliers. J. VLSI Signal Process. Syst. Signal Image Video Technol. 19, 149–166 (1998). https://doi.org/10.1023/A:1008013818413

Lin, C.-C., Chang, F.-K., Chang, H.-C., Lee, C.-Y.: An universal VLSI architecture for bit-parallel computation in \(GF(2^m)\). In: IEEE Asia-Pacific Conference on Circuits and Systems, pp. 125–128 (2004). https://doi.org/10.1109/APCCAS.2004.1412708

Inumary, H., Mohamed Asan Basiri, M.: Reconfigurable hardware design for polynomial Galois field arithmetic operations. In: IEEE International Symposium on VLSI Design and Test, pp. 1–5 (2020). https://doi.org/10.1109/VDAT50263.2020.9190485

Mohamed Asan Basiri, M., Shukla, S.K.: Flexible VLSI architectures for Galois field multipliers. Integr. VLSI J. 50, 109–124 (2017)

Acknowledgements

This work is a part of sponsored project (IHUB-NTIHAC/2021/01/1) of C3I Center, IIT Kanpur. Also, this work is fully supported and funded by the same. We thank IHUB-NTIHAC, C3I Center of IIT Kanpur for the given support.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Inumarty, H., Mohamed Asan Basiri, M. (2022). Low Cost Hardware Design of ECC Scalar Multiplication. In: Shah, A.P., Dasgupta, S., Darji, A., Tudu, J. (eds) VLSI Design and Test. VDAT 2022. Communications in Computer and Information Science, vol 1687. Springer, Cham. https://doi.org/10.1007/978-3-031-21514-8_32

Download citation

DOI: https://doi.org/10.1007/978-3-031-21514-8_32

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-21513-1

Online ISBN: 978-3-031-21514-8

eBook Packages: Computer ScienceComputer Science (R0)