Abstract

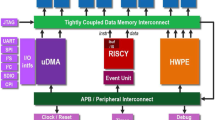

Convolution image filtering technique has been extensively used in image processing applications for sharpening the image, detecting the edges, blurring the image, noise removal etc. Optimization of the convolution algorithm for execution speed has become crucial as the size of the image increases. Loop unrolling is an optimization technique that is adopted for reducing the execution time of the algorithm by reducing the overheads caused by the loops in the algorithm implementation. RISC-V ISA based processing elements being open source are widely used in academia and industry. Hence, in this paper, we have attempted to implement convolution algorithm sequentially and with loop unrolling technique on a custom-developed RISC-V soft core processor. Further, to enhance the speed of operation, a multiprocessor framework has also been developed with Network-on-Chip based inter-core communication platform. The implemented algorithms are tested with RARS tool at assembly level and with Vivado tool at the architectural level. The architecture is also synthesized and implemented on Kintex FPGA evaluation platform.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Capobianco, G., et al.: Image convolution: a linear programming approach for filters design. Soft Comput. 25(14), 8941–8956 (2021). https://doi.org/10.1007/s00500-021-05783-5

Toolchain Primer. Power and Performance in Enterprise Systems, pp. 207–239 (2015)

Loop unrolling - Wikipedia. https://en.wikipedia.org/wiki/Loop_unrolling

Getting started with RISC-V and its Architecture - Softnautics. https://www.softnautics.com/getting-started-with-risc-v-and-its-architecture/

Waterman, A., Asanovi’c, K. (eds.): The RISC-V Instruction Set Manual, Volume I: User-Level ISA, Document Version 2.2, RISC-V Foundation (2017). https://riscv.org/wp-content/uploads/2017/05/riscv-spec-v2.2.pdf. Accessed 07 Nov 2021

Garcia-Ramirez, R., et al.: Siwa: a RISC-V RV32I based micro-controller for implantable medical applications. In: 2020 IEEE 11th Latin American Symposium on Circuits and Systems, LASCAS 2020, February 2020

Bilbao-Castro, J.R., Martínez, J.A., Baldó, J.I.A.: Multicore computing. In: Dubitzky, W., Wolkenhauer, O., Cho, K.H., Yokota, H. (eds.) Encyclopedia of Systems Biology, pp. 1461–1463. Springer, New York (2013). https://doi.org/10.1007/978-1-4419-9863-7_1000

Bosi, B., Bois, G., Savaria, Y.: Reconfigurable pipelined 2-D convolvers for fast digital signal processing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 7(3), 299–308 (1999)

Yazhuo, D., Jie, Z., Yong, D., Lin, D., Jinjing, Z.: Impact of loop unrolling on area, throughput and clock frequency for window operations based on a data schedule method. In: Proceedings - 1st International Congress on Image and Signal Processing, CISP 2008, vol. 1, pp. 641–645 (2008)

Akgün, D.: Performance evaluations for parallel image filter on multi - core computer using Java threads. Int. J. Comput. Appl. 74(11), 13–19 (2013)

Samyan, Q.W., Sahar, W., Talha, W., Aslam, M., Martinez-Enriquez, A.M.: Real time digital image processing using point operations in multithreaded systems. Proceedings - 14th Mexican International Conference on Artificial Intelligence: Advances in Artificial Intelligence, MICAI 2015, pp. 52–57, March 2016

Pour, E.S.H.: A survey of multithreading image analysis, June 2015. http://arxiv.org/abs/1506.04472

Zekri, A.S.: Multi-threaded computation of the Sobel image gradient on intel multi-core processors using OpenMP library. Int. J. Comput. Sci. Inf. Technol. 8(2), 87–100 (2016)

Micheli, G.D., Benini, L.: Networks on Chips. Morgan Kaufmann, San Fransisco (2006)

Kundu, S., Soumya, J., Chattopadhyay, S.: Design and evaluation of mesh-of-tree based network-on-chip using virtual channel router. Microprocess. Microsyst. 36(6), 471–488 (2012)

RARS RISC-V Simulator [ECEN 323]. http://ecen323wiki.groups.et.byu.net/dokuwiki/doku.php?id=labs:riscv_rars

Palnitker, S.: Verilog HDL. Prentice Hall Press, Upper Saddle River (2003)

UG973 (v2016.2): Vivado Design Suite User Guide, Xilinx, June 2016

Xilinx and Inc.: KC705 Evaluation Board for the Kintex-7 FPGA User Guide. www.xilinx.com

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Aparna Nair, M.K., Gautam, V.V., Revinipati, A., Soumya, J. (2022). Implementation and Analysis of Convolution Image Filtering with RISC-V Based Architecture. In: Shah, A.P., Dasgupta, S., Darji, A., Tudu, J. (eds) VLSI Design and Test. VDAT 2022. Communications in Computer and Information Science, vol 1687. Springer, Cham. https://doi.org/10.1007/978-3-031-21514-8_42

Download citation

DOI: https://doi.org/10.1007/978-3-031-21514-8_42

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-21513-1

Online ISBN: 978-3-031-21514-8

eBook Packages: Computer ScienceComputer Science (R0)