Abstract

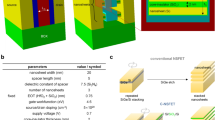

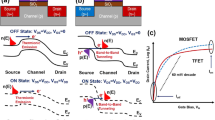

Reliability and yield are major concerns of nano-scaled devices. Bias temperature instability (BTI) has always been one of the major reliability issue for the semiconductor transistors. BTI induced interface traps play a vital role in defining important figures of merits such as threshold voltage (V\(_{TH}\)), ON current, and \(I_{ON}/I_{OFF}\) in terms of the reliability of the transistor, especially in p-type devices. In this paper, for the first time, we investigate the impact of the Si-SiO\(_{2}\) interface traps (N\(_{it}\)) on the performance of the p-type Negative Capacitance Nanosheet (NC-NS) FET. Using well-calibrated TCAD models our results demonstrate that: 1) the end of life (EOL) concentration (i.e., shift of threshold voltage (\(\Delta V_{TH}= 50\) mV) in threshold voltage degradation is improved in NC NSFET as compared to baseline NSFET; 2) the smaller degradation in \(I_{ON}/I_{OFF}\) and subthreshold slope (SS) is achieved in NC-NSFET. We investigate and evaluate the performance metrics of NC-NS FET in comparison to the baseline NSFET. Our result reveals that NC-NSFET exhibit 2.5 times less degradation in V\(_{TH}\), and 11.76x less degradation in \(I_{ON}/I_{OFF}\) ratio.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Salahuddin, S., Datta, S.: Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8(2), 405–410, (2008). https://doi.org/10.1021/nl071804g.

Chauhan, N., Bagga, N., Banchhor, S., Datta, A., Dasgupta, S., Bulusu, A.: Negative-to-positive differential resistance transition in ferroelectric FET: physical insight and utilization in analog circuits. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 69(1), 430–437 (2022)

Zhou, J., et al.: Negative differential resistance in negative capacitance FETs. IEEE Electron Device Lett. 39(4), 622–625 (2018)

Chauhan, N.: BOX engineering to mitigate negative differential resistance in MFIS negative capacitance FDSOI FET: an analog perspective. Nanotechnology 33(8), 085203 (2021). https://doi.org/10.1088/1361-6528/ac328a

Hoffmann, M., Max, B., Mittmann, T., Schroeder, U., Slesazeck, S., Mikolajick, T.: Demonstration of high-speed hysteresis-free negative capacitance in ferroelectric hf0.5zr0.5o2. In: 2018 IEEE International Electron Devices Meeting (IEDM), pp. 1–4 (2018). https://doi.org/10.1109/IEDM.2018.8614677

Hoffmann, M., et al.: Unveiling the double-well energy landscape in a ferroelectric layer. Nature 565(7740) 464–467 (2019). https://doi.org/10.1038/s41586-018-0854-z

Bajpai, G., et al.: Impact of radiation on negative capacitance finfet. In: 2020 IEEE International Reliability Physics Symposium (IRPS), pp. 1–5 (2020). https://doi.org/10.1109/IRPS45951.2020.9129165

Bajpai, G., Gupta, A., Prakash, O., Chauhan, Y.S., Amrouch, H.: Soft errors in negative capacitance fdsoi srams. In: 2021 5th IEEE Electron Devices Technology Manufacturing Conference (EDTM), pp. 1–3 (2021). https://doi.org/10.1109/EDTM50988.2021.9421043

Prakash, O., Gupta, A., Pahwa, G., Henkel, J., Chauhan, Y.S., Amrouch, H.: Impact of interface traps on negative capacitance transistor: device and circuit reliability. IEEE J. Electron Devices Soc. 8, 1193–1201 (2020). https://doi.org/10.1109/JEDS.2020.3022180

Gupta, A., et al: Traps based reliability barrier on performance and revealing early ageing in negative capacitance FET. In: 2021 IEEE International Reliability Physics Symposium (IRPS), pp. 1–6 (2021). https://doi.org/10.1109/IRPS46558.2021.9405185

Garg, C., et al.: Investigation of trap-induced performance degradation and restriction on higher ferroelectric thickness in negative capacitance FDSOI FET. IEEE Trans. Electron Devices 68(10), 5298–5304 (2021)

Loubet, N., et al.: Stacked nanosheet gate-all-around transistor to enable scaling beyond FINFET. In: Symposium on VLSI Technology, vol. 2017, pp. 230–231 (2017)

Sentaurus device user guide, version p-2019.03-sp1, synopsys, inc. mountain view, CA, USA. https://www.synopsys.com/. Accessed Apr 2020

Mahapatra, S. (ed.): Fundamentals of Bias Temperature Instability in MOS Transistors. SSAM, vol. 52. Springer, New Delhi (2016). https://doi.org/10.1007/978-81-322-2508-9

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Gupta, A. et al. (2022). Unveiling the Impact of Interface Traps Induced on Negative Capacitance Nanosheet FET: A Reliability Perspective. In: Shah, A.P., Dasgupta, S., Darji, A., Tudu, J. (eds) VLSI Design and Test. VDAT 2022. Communications in Computer and Information Science, vol 1687. Springer, Cham. https://doi.org/10.1007/978-3-031-21514-8_8

Download citation

DOI: https://doi.org/10.1007/978-3-031-21514-8_8

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-21513-1

Online ISBN: 978-3-031-21514-8

eBook Packages: Computer ScienceComputer Science (R0)