Abstract

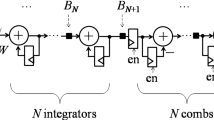

The number of Additions Per Output Sample (APOS) is, currently, a standard way to estimate the computational complexity of Cascaded Integrator-Comb (CIC) decimators. This metric originates from a perspective with a high level of abstraction, where the amount of additions performed by the CIC hardware architecture accounts in general for the switching activity of the system, and therefore represents the power consumption in a direct proportion. In this paper we introduce an approach that leads towards a more appropriate way to estimate the computational complexity of CIC decimators, which considers the width of the internal buses of the architecture. We employ the pruning scheme by Hogenauer, and we provide explicit formulas to find, through a simple procedure, the number of Atomic Additions Per Output Sample (AAPOS), which accounts for the computational complexity on a bit-by-bit (i.e., atomic) basis. Three detailed examples are included to show how the AAPOS provides different results for systems with apparently equal computational complexity when estimated with APOS, leading to a more precise and trustable estimation.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Harris, F.: Multirate Signal Processing for Communication Systems, 2nd edn. River Publishers, Gistrup (2021)

Luo, F.-L.: Digital Front-End in Wireless Communications and Broadcasting: Circuits and Signal Processing. Cambridge University Press, Cambridge (2011)

Hogenauer, E.: An economical class of digital filters for decimation and interpolation. IEEE Trans. Acoust. Speech Sig. Process. 29(2), 155–162 (1981)

Abinaya, A., Maheswari, M., Alqahtani, A.S.: Heuristic analysis of CIC filter design for next-generation wireless applications. Arab. J. Sci. Eng. 46, 1257–1268 (2021)

Datta, D., Mitra, P., Dutta, H.S.: FPGA implementation of high performance digital down converter for software defined radio. Microsyst. Technol. (2019)

Gautam, D., Khare, K., Shrivastava, B.P.: A novel approach for optimal design of sample rate conversion filter using linear optimization technique. IEEE Access (2021)

Aggarwal, S.: Efficient design of decimation filters using linear programming and its FPGA implementation. Integr. VLSI J. 79, 94–106 (2021)

Martens, E., et al.: RF-to-baseband digitization in 40 nm CMOS with RF bandpass Σ-Δ modulator and polyphase decimation filter. IEEE J. Solid State Circuit 47(4), 990–1002 (2012)

Pavan, S., Shcreier, R., Temes, G.C.: Understanding Delta-Sigma Data Converters. Wiley, Hoboken (2017)

Troncoso-Romero, D.E., Jimenez, M.G.C., Meyer-Baese, U.: Alternative data paths for the Cascaded Integrator-Comb decimator. IEEE Sig. Process. Mag. 38(3), 194–200 (2021)

Troncoso-Romero, D.E., Jimenez, M.G.C., Meyer-Baese, U.: Hardware-efficient decimation with spectral shape approximating the Nth power of a Dirichlet kernel. Circuits Syst. Sig. Process. 41, 4886–4905 (2022)

Dudarin, A., Vucic, M., Molnar, G.: Decimation filters with minimum number of additions per output sample. Electron. Lett. 58(6), 246–248 (2022)

Jovanovic, G.: Update on the CIC multistage decimation filter with a minimum number of additions per output sample (APOS): can we still decrease the number of APOS? IEEE Sig. Process. Mag. 40(2), 151–172 (2023)

Troncoso-Romero, D.E.: Simplifying zero rotations in Cascaded Integrator-Comb decimators. IEEE Sig. Process. Mag. 40(3), 50–58 (2023)

Meyer-Baese, U.: Digital Signal Processing with Field Programmable Gate Arrays, 4th edn. Springer, Heidelberg (2014). https://doi.org/10.1007/978-3-642-45309-0

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Romero, D.E.T., Pacheco, J.C.R., Borges, J.A.L., Cruz, H.T. (2023). APOS is Not Enough: Towards a More Appropriate Way to Estimate Computational Complexity in CIC Decimation Architectures. In: Mata-Rivera, M.F., Zagal-Flores, R., Barria-Huidobro, C. (eds) Telematics and Computing. WITCOM 2023. Communications in Computer and Information Science, vol 1906. Springer, Cham. https://doi.org/10.1007/978-3-031-45316-8_2

Download citation

DOI: https://doi.org/10.1007/978-3-031-45316-8_2

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-45315-1

Online ISBN: 978-3-031-45316-8

eBook Packages: Computer ScienceComputer Science (R0)