Abstract

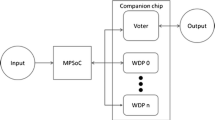

Among all the fault tolerance (FT) techniques developed over the years, Dual-core lock-step techniques have emerged as an effective approach to enhance the fault tolerance capabilities of these systems. However, they cannot withstand Hard Errors occurring in the architecture, and they have certain drawbacks for checkpoints and restore methodologies necessary to save and restore the correct state of the core. This paper shows an execution paradigm within a new architectural approach to overcome the disadvantages related to the long checkpointing/restoring procedures that affect the classical lock-step architectures, also improving the hard, destructive faults resilience, leveraging the advantages of the already published dynamic-TMR technique inside the Klessydra-dfT03 architecture.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Barbirotta M, Mastrandrea A, Cheikh A, Menichelli F, Olivieri M (2022) Improving set fault resilience by exploiting buffered DMR microarchitecture. In: Annual meeting of the Italian electronics society. Springer, pp 233–238

Barbirotta M, Mastrandrea A, Menichelli F, Vigli F, Blasi L, Cheikh A, Sordillo S, Di Gennaro F, Olivieri M (2020) Fault resilience analysis of a risc-v microprocessor design through a dedicated UVM environment. In: 2020 IEEE international symposium on defect and fault tolerance in VLSI and nanotechnology systems (DFT). IEEE, pp 1–6

Secretariat E (2008) Space product assurance

Violante M, Meinhardt C, Reis R, Reorda MS (2011) A low-cost solution for deploying processor cores in harsh environments. IEEE Trans Ind Electron 58(7):2617–2626

de Oliveira ÁB, Rodrigues GS, Kastensmidt FL (2017) Analyzing lockstep dual-core arm cortex-a9 soft error mitigation in Freertos applications. In: Proceedings of the 30th symposium on integrated circuits and systems design: chip on the sands, pp 84–89

Yiu J (2015) Design of SOC for high reliability systems with embedded processors. In: Embedded World Conference

Iturbe X, Venu B, Ozer E, Poupat JL, Gimenez G, Zurek HU (2019) The arm triple core lock-step (TCLS) processor. ACM Trans Comput Syst (TOCS) 36(3):1–30

Marques I, Rodrigues C, Tavares A, Pinto S, Gomes T (2021) Lock-V: a heterogeneous fault tolerance architecture based on Arm and RISC-V. Microelectron Reliabil 120:114120

Kasap S, Wächter EW, Zhai X, Ehsan S, McDonald-Maier KD (2021) Novel lockstep-based fault mitigation approach for SOCs with roll-back and roll-forward recovery. Microelectron Reliabil 124:114297

Cheikh A, Sordillo S, Mastrandrea A, Menichelli F, Scotti G, Olivieri M (2021) Klessydra-t: designing vector coprocessors for multithreaded edge-computing cores. IEEE Micro 41(2):64–71

Barbirotta M, Cheikh A, Mastrandrea A, Menichelli F, Olivieri M (2022) Design and evaluation of buffered triple modular redundancy in interleaved-multi-threading processors. IEEE Access 10:126074–126088

Barbirotta M, Cheikh A, Mastrandrea A, Menichelli F, Ottavi M, Olivieri M (2023) Evaluation of dynamic triple modular redundancy in an interleaved-multi-threading RISC-V core. J Low Power Electron Appl 13(1). https://www.mdpi.com/2079-9268/13/1/2

Liu K, Li Y, Ouyang L (2022) A survey of fault tolerance hardware architecture. In: 2021 international conference on advanced computing and endogenous security. IEEE, pp 01–06

Poivey C, Carriere T, Beaucour J, Oldham T (1994) Characterization of single hard errors (SHE) in 1 m-bit SRAMS from single ion. IEEE Trans Nucl Sci 41(6):2235–2239

Amrouch H, van Santen VM, Ebi T, Wenzel V, Henkel J (2014) Towards interdependencies of aging mechanisms. In: 2014 IEEE/ACM international conference on computer-aided design (ICCAD). IEEE, pp 478–485

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2024 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Barbirotta, M. et al. (2024). Heterogeneous Tightly-Coupled Dual Core Architecture Against Single Event Effects. In: Bellotti, F., et al. Applications in Electronics Pervading Industry, Environment and Society. ApplePies 2023. Lecture Notes in Electrical Engineering, vol 1110. Springer, Cham. https://doi.org/10.1007/978-3-031-48121-5_2

Download citation

DOI: https://doi.org/10.1007/978-3-031-48121-5_2

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-48120-8

Online ISBN: 978-3-031-48121-5

eBook Packages: EngineeringEngineering (R0)