Abstract

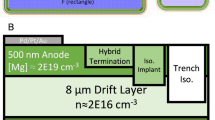

Moore’s Law states that transistor density will double every two years, which is sustained until today due to continuous multidirectional innovations (such as extreme ultraviolet lithography, novel patterning techniques etc.), leading the semiconductor industry towards 3 nm node (N3) and beyond. For any patterning scheme, the most important metric to evaluate the quality of printed patterns is edge placement error, with overlay being its largest contribution. Overlay errors can lead to fatal failures of IC devices such as short circuits or broken connections in terms of pattern-to-pattern electrical contacts. Therefore, it is essential to develop effective overlay analysis and control techniques to ensure good functionality of fabricated semiconductor devices. In this work we have used an imec N-14 BEOL process flow using litho-etch-litho-etch (LELE) patterning technique to print metal layers with minimum pitch of 48 nm with 193i lithography. Fork-fork structures are decomposed into two mask layers (M1A and M1B) and then the LELE flow is carried out to make the final patterns. Since a single M1 layer is decomposed into two masks, control of overlay between the two masks is critical. The goal of this work is of two-fold as, (1) to quantify the impact of overlay on capacitance and (2) to see if we can predict the final capacitance measurements with selected machine learning models at an early stage. To do so, scatterometry spectra are collected on these electrical test structures at (a) post litho, (b) post TiN hardmask etch, and (c) post Cu plating and CMP. Critical Dimension (CD) and overlay measurements for line/space (L/S) pattern are done with SEM post litho, post etch and post Cu CMP. Various machine learning models are applied to do the capacitance prediction with multiple metrology inputs at different steps of wafer processing. Finally, we demonstrate that by using appropriate machine learning models we are able to do better prediction of electrical results.

B. Dey, A. T. Ngo and S. Sacchi—Contributed equally to the work.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Bode, C., et al.: Run-to-run control and performance monitoring of overlay in semiconductor manufacturing. Control. Eng. Pract. 12(7), 893–900 (2004). https://doi.org/10.1016/S0967-0661(03)00154-0

Breton, M., et al.: Electrical test prediction using hybrid metrology and machine learning. In: Metrology, Inspection, and Process Control for Microlithography XXXI, vol. 10145, pp. 16–23. SPIE (2017). https://doi.org/10.1117/12.2261091

Ngo, A.T., et al.: Machine learning based edge placement error analysis and optimization: a systematic review. IEEE Trans. Semicond. Manuf. (2022). https://doi.org/10.1109/TSM.2022.3217326

Orji, N.G., et al.: Metrology for the next generation of semiconductor devices. Nat. Electron. 1(10), 532–547 (2018). https://doi.org/10.1038/s41928-018-0150-9

Pedregosa, F., et al.: Scikit-learn: machine learning in python. J. Mach. Learn. Res. 12, 2825–2830 (2011)

Prasad, D.J.L., et al.: Diffraction based overlay metrology for double patterning technologies. In: Recent Advances in Nanofabrication Techniques and Applications, p. 433 (2011)

Rana, N., et al.: Leveraging advanced data analytics, machine learning, and metrology models to enable critical dimension metrology solutions for advanced integrated circuit nodes. J. Micro/Nanolithogr. MEMS MOEMS 13(4), 041415–041415 (2014). https://doi.org/10.1117/1.JMM.13.4.041415

Saravanan, C.S., et al.: Evaluating diffraction based overlay metrology for double patterning technologies. In: Metrology, Inspection, and Process Control for Microlithography XXII, vol. 6922, pp. 125–136. SPIE (2008). https://doi.org/10.1117/12.774736

Vaid, A., et al.: A holistic metrology approach: hybrid metrology utilizing scatterometry, cd-afm, and cd-sem. In: Metrology, Inspection, and Process Control for Microlithography XXV, vol. 7971, pp. 21–40. SPIE (2011). https://doi.org/10.1117/12.881632

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2025 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Dey, B., Tuan Ngo, A., Sacchi, S., Blanco, V., Leray, P., Halder, S. (2025). Applying Machine Learning Models on Metrology Data for Predicting Device Electrical Performance. In: Meo, R., Silvestri, F. (eds) Machine Learning and Principles and Practice of Knowledge Discovery in Databases. ECML PKDD 2023. Communications in Computer and Information Science, vol 2136. Springer, Cham. https://doi.org/10.1007/978-3-031-74640-6_36

Download citation

DOI: https://doi.org/10.1007/978-3-031-74640-6_36

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-74639-0

Online ISBN: 978-3-031-74640-6

eBook Packages: Artificial Intelligence (R0)