Abstract

State-of-the-art optimizations for high performance are frequently related to particular hardware parameters and features. This typically leads to optimized software for execution on particular hardware configurations. However, so far, the applications lack the ability to modify hardware parameters either statically before execution of a program or dynamically during run-time.

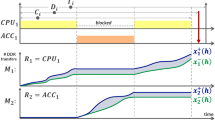

In this paper, we first propose to utilize the flexibility of underlying invasive hardware to adapt to the needs of the software. This enables us to ask for more than just processing power by, e.g., requesting particular cache parameters that correspond to certain application properties. The adaptive hardware architecture therefore is able to dynamically reconfigure itself dependent on the availability of the resources in order to achieve an optimized working point for each application scenario. Secondly, we present requirements for dynamical scheduling of computing resources to resource-competing applications. This becomes mandatory to account for memory-access characteristics of concurrently executed applications. We propose consideration of such characteristics with bandwidth-aware invasion.

With this novel approach, we are able to show that dynamic hardware and software co-design leads to improved utilization of the underlying hardware resulting in higher throughput in means of efficiency such as application-throughput per time-unit.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Bader, M., Bungartz, H.-J., Gerndt, M., Hollmann, A., Weidendorfer, J.: Invasive programming as a concept for hpc. In: Proc. of the 10h IASTED Int. Conf. on Par. and Dist. Comp. and Netw. (2011)

Brechmann, E.C., Schepsmeier, U.: Modeling dependence with c-and d-vine copulas: The r-package cdvine. Journal of Statistical Software 52 (2012)

Bungartz, H.-J., Mehl, M., Weinzierl, T.: A Parallel Adaptive Cartesian PDE Solver Using Space–Filling Curves. In: Nagel, W.E., Walter, W.V., Lehner, W. (eds.) Euro-Par 2006. LNCS, vol. 4128, pp. 1064–1074. Springer, Heidelberg (2006)

Bungartz, H.-J., Riesinger, C., Schreiber, M., Snelting, G., Zwinkau, A.: Invasive Computing in HPC with X10. In: X10 Workshop, X10 2013 (2013)

Damien, G.: Study of different cache line replacement algorithms in embedded systems. PhD thesis, KTH (2007)

Gerndt, M., Hollmann, A., Meyer, M., Schreiber, M., Weidendorfer, J.: Invasive computing with iomp. In: Specification and Design Languages, FDL (2012)

Gordon-Ross, A., Vahid, F.: A self-tuning configurable cache. In: Proceedings of the 44th Annual Conference on Design Automation, DAC (2007)

Heinecke, A., Trinitis, C.: Cache-oblivious matrix algorithms in the age of multi- and many-cores. In: Concurrency and Computation: Practice and Experience (2012)

Henkel, J., Bauer, L., Hübner, M., Grudnitsky, A.: i-Core: A run-time adaptive processor for embedded multi-core systems. In: International Conference on Engineering of Reconfigurable Systems and Algorithms (2011)

Ji, X., Nicolaescu, D., Veidenbaum, A., Nicolau, A., Gupta, R.: Compiler Directed Cache Assist Adaptivity. In: High Performance Computing (2000)

Malik, A., Moyer, B., Cermak, D.: A low power unified cache architecture providing power and performance flexibility (poster session). In: Proceedings of the 2000 International Symposium on Low Power Electronics and Design (2000)

Marty, M.R.: Cache Coherence Techniques for Multicore Proc. PhD thesis (2008)

Nicolaescu, D., Ji, X., Veidenbaum, A.V., Nicolau, A., Gupta, R.: Compiler-directed cache line size adaptivity. In: Chong, F.T., Kozyrakis, C., Oskin, M. (eds.) IMS 2000. LNCS, vol. 2107, p. 183. Springer, Heidelberg (2001)

Nowak, F., Buchty, R., Karl, W.: A Run-time Reconfigurable Cache Architecture. In: International Conference on Parallel Computing: Architectures, Algorithms and Applications (2007)

Nowak, F., Buchty, R., Karl, W.: Adaptive Cache Infrastructure: Supporting dynamic Program Changes following dynamic Program Behavior. In: Proceedings of the 9th Workshop on Parallel Systems and Algorithms, PASA (2008)

Ogita, T., Rump, S.M., Oishi, S.: Accurate sum and dot product. SIAM Journal on Scientific Computing 26 (2005)

Rüde, U.: Mathematical and computational techniques for multilevel adaptive methods. Society for Industrial and Applied Mathematics (1993)

Schreiber, M., Bungartz, H.-J., Bader, M.: Shared memory parallelization of fully-adaptive simulations using a dynamic tree-split and -join approach. In: IEEE Int. Conf. on High Performance Comp, HiPC (2012)

Tradowsky, C., Thoma, F., Hubner, M., Becker, J.: Lisparc: Using an architecture description language approach for modelling an adaptive processor microarchitecture (best work-in-progress (wip) paper award). In: 7th IEEE International Symposium on Industrial Embedded Systems, SIES (2012)

Zhang, C., Vahid, F., Najjar, W.: A Highly Configurable Cache Architecture for Embedded Systems. In: 30th Annual Int. Symp. on Computer Architecture (2003)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2014 Springer International Publishing Switzerland

About this paper

Cite this paper

Tradowsky, C. et al. (2014). Towards Dynamic Cache and Bandwidth Invasion. In: Goehringer, D., Santambrogio, M.D., Cardoso, J.M.P., Bertels, K. (eds) Reconfigurable Computing: Architectures, Tools, and Applications. ARC 2014. Lecture Notes in Computer Science, vol 8405. Springer, Cham. https://doi.org/10.1007/978-3-319-05960-0_9

Download citation

DOI: https://doi.org/10.1007/978-3-319-05960-0_9

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-05959-4

Online ISBN: 978-3-319-05960-0

eBook Packages: Computer ScienceComputer Science (R0)