Abstract

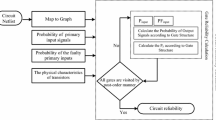

As CMOS technology scales to nanometer dimensions, its performance and behavior become less predictable. Reliability studies for nanocircuits and systems become important when the circuit’s outputs are affected by its sensitive noisy inputs. In conventional circuits, the impact of the inputs on reliability can be observed by the deterministic input patterns. However, in nanoscale circuits, the inputs behave probabilistically. The Bayesian networks technique is used to compute the reliability of a circuit in conjunction with the Monte Carlo simulations approach which is applied to model the probabilistic inputs and ultimately to determine sensitive inputs and worst-case input combinations.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

Notes

- 1.

Deep submicron design technologies refers to those CMOS circuits which have physical gate length less than 100 nm but greater than 10 nm.

References

Zhang, K.: Challenges and opportunities in nano-scale VLSI design, International Symposium on VLSI Design, Automation and Test, 2005. (VLSI-TSA-DAT). IEEE VLSI-TSA 6(7), 27–29 (2005)

Siewiorek, D.P., Swarz, R.S.: Reliable Computer Systems: Design and Evaluation. AK Peters, Natick (1998)

ITRS. International Technology Roadmap for Semiconductors (ITRS). Available via DIALOG. http://www.itrs.net/ (2013)

Stanisavljevic, M.: Optimization of nanoelectronic systems reliability by reducing logic depth. In: Stanisavljevic, M., Schmid, A., Leblebici, Y. (eds.) Fourth International Conference on Nano-Nets, Nano-Net. Lucerne, Switzerland (2009)

Bhaduri, D.: Design and analysis of defect- and dault-tolerant nano-computing systems. Ph.D. dissertation, Virginia Polytechnic Institute and State University, etd-03182007-194734 (2007)

Khakifirooz, A., Antoniadis, D.A.: MOSFET Performance Scaling—Part II: Future Directions. IEEE Trans. Electron Dev. 55(6), 1401–1408 (2008)

Rusu, S.: Trends and scaling in VLSI technology scaling towards 100nm (Invited Paper). In: Rusu, S. (eds.) European Solid-State Circuits Conference (ESSCIRC) (2001)

Huang, C.: Robust Computing with Nanoscale Devices: Progresses and Challenges. Springer, New York (2010)

Stanisavljevic, M., Schmid, A., Leblebici, Y.: Reliability of Nanoscale Circuits and Systems: Methodologies and Circuit Architectures. Springer, New York (2010)

Ryhnen, T., Uusitalo, M.A., Ikkala, O., Krkkinen, A.: Nanotechnologies for Future Mobile Devices. Springer, Cambridge (2010)

Casati, G., Matrasulov, D.: Complex Phenomena in Nanoscale Systems. Springer, New York (2009)

Wooley, J.C., Lin, H.: Catalyzing Inquiry at the Interface of Computing and Biology. National Academies Press, Washington (2005)

Tehranipoor, M.: Emerging Nanotechnologies: Test, Defect-Tolerance and Reliability, Frontiers in Electronic Testing, vol. 37. Springer, New York (2008)

Bahar, R.I., Mundy, J., Chan, J.: A probabilistic based design methodology for nanoscale computation. In: International Conference on Computer Aided Design (IC- CAD), pp. 480–486 (2003)

Anwer, J., Khalid, U., Singh, N., Hamid, N.H., Asirvadam, V.S.: A novel error-detection mechanism for digital circuits using Markov random field modelling. In: IEEE International Conference on Computational Intelligence and Communication Networks (CICN), pp. 883–886 (2012)

Nepal, K., Bahar, R.I., Mundy, J., Patterson, W.R., Zaslavsky, A.: MRF reinforcer: a probabilistic element for space redundancy in nanoscale circuits. IEEE Micro, IEEE Comput. Soc. Mag. 26(5), 19–27 (2006)

Nepal, K.: Markov random field: in designing reliable nanoscale circuits using principles of Markov random fields. Ph.D. dissertation. Brown University

Anwer, J., Khalid, U., Singh, N., Hamid, N.H., Asirvadam, V.S.: Highly noise-tolerant design of digital logic gates using Markov random field modelling. In: International Conference on Electronic Computer Technology (ICECT), pp. 24–28 (2010)

Anwer, J., Shaukat, S.F., Khalid, U., Hamid, N.H.: Reliable area index: a novel approach to measure reliability of Markov random field based circuits. In: International Conference on Intelligent and Advanced Systems (ICIAS), pp. 24–28 (2012)

Anwer, J., Fayyaz, A., Masud, M.M., Shaukat, S.F., Hamid, N.H.: Fault-tolerance and noise modelling in nanoscale circuit design. In: International Symposium on Signals Systems and Electronics (ISSSE), vol. 2, pp. 1–4 (2010)

Anwer, J., Khalid, U., Singh, N., Hamid, N.H., Asirvadam, V.S.: Joint and marginal probability analyses of Markov random field networks for digital logic circuits. In: International Conference on Intelligent and Advanced Systems (ICIAS), pp. 1–4 (2010)

Han, J., Taylor, E., Gao. J., Fortes, J.: Faults, error bounds and reliability of nanoelectronic circuits. In: Proceedings of 16th International Conference on Application-Specific Systems, Architecture and Processors (ASAP), pp. 247–253 (2005)

Mohyuddin, N., Pakbaznia, E., Pedram, M.: Probabilistic error propagation in logic circuits using the boolean difference calculus. In: Proceedings of 26th International Conference on Computer Design (ICCD), pp. 7–13 (2008)

Krishnaswamy, S., Viamontes, G.F., Markov, I.L., Hayes, J.P.: Probabilistic transfer matrices in symbolic reliability analysis of logic circuits. ACM Trans. Des. Autom. Electron. Syst. (TODAES) 13(1), 7–13 (2008)

Rejimon, T., Lingasubramanian, K., Bhanja, S.: Probabilistic error modeling for nano-domain logic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 17(1), 5565 (2009)

Han, J., Chen, H., Liang, J., Zhu, P., Yang, Z., Lombardi, F., Lombardi, F.: A stochastic computational approach for accurate and efficient reliability evaluation. IEEE Trans. Comput. 63(6), 1336–1350 (2014)

Singh, N.S.S., Hamid, N.H., Asirvadam, V.S., Khalid, U., Anwer, J.: Evaluation of circuit reliability based on distribution of different signal input patterns. In: IEEE 8th International Colloquium on Signal Processing and Its Applications (CSPA), pp. 5–9 (2012)

Singh, N.S.S., Hamid, N.H., Asirvadam, V.S., Khalid, U., Anwer, J.: Sensitivity analysis of probability transfer matrix (PTM) on same functionality circuit architectures. In: IEEE 8th International Colloquium on Signal Processing and Its Applications (CSPA), pp. 250–254 (2012)

Zhao, C., Bai, X., Dey, S.: Evaluating transient error effects in digital nanometer circuits. IEEE Trans. Reliab. 56(3), 381–391 (2007)

Mavis, D.G., Eaton, P.H.: SEU and SET modeling and mitigation in deep submicron technologies. In: IEEE international Reliability Physics Symposium (IRPS), pp. 293–305, 15–19 (2007)

Veeravalli, V.S., Polzer, T., Steininger, A., Schmid, U.: Architecture and design analysis of a digital single-event transient/upset measurement chip. In: 15th Euromicro Conference on Digital System Design (DSD), pp. 8–17, 5–8 (2012)

Ferlet-Cavrois, V., Massengill, L.W., Gouker, P.: Single event transients in digital CMOS a review. IEEE Trans. Nucl. Sci. 60(3), 1767–1790 (2013)

Sulieman, M., Beiu, V.: Design and analysis of SET circuits: using MATLAB modules and SIMON. In: 4th IEEE Conference on Nanotechnology, pp. 618–621, 16–19 (2004)

Landau, D.P., Binder, K.: A Guide to Monte Carlo Simulations in Statistical Physics, pp. 384. Cambridge University Press, Cambridge (2009)

Khalid, U., Anwer, J., Singh, N., Hamid, N.H., Asirvadam, V.S.: Reliability-evaluation of digital circuits using probabilistic computation schemes. In: National Postgraduate Conference (NPC), pp. 19–20 (2011)

Khalid, U., Anwer, J., Singh, N., Hamid, N.H., Asirvadam, V.S.: Computation and analysis of output error probability for C17 benchmark circuit using Bayesian networks error modeling. In: IEEE Student Conference on Research and Development (SCOReD), pp. 348–351 (2011)

Khalid, U.: Reliability-evaluation of nanoscale circuit design using Bayesian networks. Masters thesis, Universiti Teknologi Petronas. http://utpedia.utp.edu.my/id/eprint/3315 (2012)

BNT. Bayes Net Toolbox for Matlab (BNT). Available via DIALOG. http://code.google.com/p/bnt/ (1997–2002). Accessed April 2014

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer International Publishing Switzerland

About this chapter

Cite this chapter

Khalid, U., Anwer, J., Hamid, N.H., Asirvadam, V.S. (2015). The Impact of Sensitive Inputs on the Reliability of Nanoscale Circuits. In: Fakhfakh, M., Tlelo-Cuautle, E., Siarry, P. (eds) Computational Intelligence in Digital and Network Designs and Applications. Springer, Cham. https://doi.org/10.1007/978-3-319-20071-2_9

Download citation

DOI: https://doi.org/10.1007/978-3-319-20071-2_9

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-20070-5

Online ISBN: 978-3-319-20071-2

eBook Packages: Computer ScienceComputer Science (R0)