Abstract

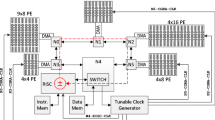

The concept of a reconfigurable coprocessor controlled by the general purpose processor, with the coprocessor acting as a specialized functional unit, has evolved to accelerate applications requiring higher computing power. The idea of Adaptive Balanced Computing (ABC) architecture has evolved, where a module of Reconfigurable Functional Cache (RFC) is configured with a selective core function in the application whenever a higher computing resources are required. Initial results have proved that the ABC architecture provides with speedups ranging from 1.04x to 5.0x depending on the application and the speedups in the range of 2.61x to 27.4x are observed for the core functions. This paper further explores the issues of management of RFC, where the impact of various schemes for configuration of core function into the RFC module is studied. This paper also gives a detailed analysis on the performance of ABC architecture for various configuration schemes, including the study of the effect of the percentage of the core function in an entire application over the management of RFC modules.

The research reported in this paper is partially funded by the grants Carver’s Trust and Nicholas Professorship from Iowa State University, and grant No. CCR9900601 from NSF.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Hauser, J.R., Wawrzynek, J.: Garp: a MIPS processor with a reconfigurable coprocessor. In: Proc. IEEE Symposium on Field-Programmable Custom Computing Machines, April 1997, pp. 12–21 (1997)

Ye, Z.A., Moshovos, A., Hauck, S., Banerjee, P.: CHIMAERA: a highperformance architecture with a tightly-coupled reconfigurable functional unit. In: Proc. 27th International Symposium on Computer Architecture, pp. 225–235 (2000)

DeHon, A.: DPGA-coupled microprocessors: commodity ICs for the early 21st Century. In: Proc. IEEE Workshop on FPGAs for Custom Computing Machines, pp. 31–39 (1994)

Razdan, R., Smith, M.D.: A High-Performance Microarchitecture With Hardware-Programmable Functional Units. In: Proc. 27th Annual International Symposium on Microarchitecture, MICRO-27, pp. 172–180 (1994)

Ranganathan, P., Adve, S., Jouppi, N.P.: Reconfigurable caches and their application to media processing. In: Proc. 27th International Symposium on Computer Architecture, pp. 214–224 (2000)

Kim, H., Somani, A.K., Tyagi, A.: A Reconfigurable Multi-function Computing Cache Architecture. In: Proc. FPGA 2000, February 2000, pp. 85–94 (2000)

Kim, H., Somani, A.K., Tyagi, A.: A reconfigurable multifunction computing cache architecture. IEEE Transactions on Very Large Scale Integration (VLSI) Systems 9(4), 509–523 (2001)

Kim, H.: Towards Adaptive Balanced Computing (ABC) Using Reconfigurable Functional Caches (RFCs)., Ph. D. Dissertation, Dept. of Electrical and Computer Engineering, Iowa State University (July 2001)

Lee, C., Potkonjak, M., Mangione-Smith, W.H.: MediaBench: a tool for evaluating and synthesizing multimedia and communications systems. In: Proc. Thirtieth Annual IEEE/ACM International Symposium on Microarchitecture, pp. 330–335 (1997)

Texas Instruments, “TMS320C6000 benchmarks” (2000), Available on, http://www.ti.com/sc/docs/products/dsp/c6000/62bench.htm

Burger, D., Austin, T.M.: The SimpleScalar Tool Set, Version 2.0. Computer Sciences Department Technical report # 1342, University of Wisconsin- Madison (June 1997)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2003 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Sangireddy, R., Kim, H., Somani, A.K. (2003). Timing Issues of Operating Mode Switch in High Performance Reconfigurable Architectures. In: Pinkston, T.M., Prasanna, V.K. (eds) High Performance Computing - HiPC 2003. HiPC 2003. Lecture Notes in Computer Science, vol 2913. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-24596-4_4

Download citation

DOI: https://doi.org/10.1007/978-3-540-24596-4_4

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-20626-2

Online ISBN: 978-3-540-24596-4

eBook Packages: Springer Book Archive