Abstract

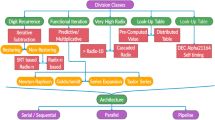

Digit-serial architecture is an attractive solution for systems requiring moderate sample rate and where area and time consumption are critical. The current paper presents a digit-serial-in-serial-out systolic architecture for performing an AB2 operation in GF(2m). If the appropriate digit-size is selected, the proposed method can meet the throughput requirement of a specific application with minimum hardware. And, the area-time complexity of the pipelined digit-serial AB2 systolic architecture is approximately 10.9% lower than that of the nonpipelined version when m = 160 and L = 2. Based on the new AB2 digit-serial architecture, we also proposed a digit-serial systolic for inverse/divisions. Furthermore, since the proposed architectures are simplicity, regularity, modularity and pipelinability, they are well suited to VLSI, and can also be utilized as the basic architecture for a cryptoprocessor.

This research was supported by University IT Research Center Project.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Denning, D.E.R.: Cryptography and data security. Addison-Wesley, MA (1983)

Menezes, A.: Elliptic Curve Public Key Cryptosystems. Kluwer Academic Publishers, Boston (1993)

Wei, S.W.: A Systolic Power-Sum Circuit for GF(2m). IEEE Trans. Computers 43, 226–229 (1994)

Guo, J.H., Wang, C.L.: Digit-serial systolic multiplier for finite fields GF(2m). IEE Proc.- Comput. Digit. Tech. 145 (1998)

Wang, C.L., Guo, J.H.: ‘New systolic arrays for C+AB2, inversion, and division in GF(2m). IEEE Transactions on Computers 49(10), 1120–1125 (2000)

Wei, S.W.: A Systolic Power-Sum Circuit for GF(2m). IEEE Trans. Computers 43, 226–229 (1994)

McCanny, J.V., Evans, R.A., Mcwhirter, J.G.: Use of unidirectional data flow in bitlevel systolic array chips. Electron. Lett. 22, 540–541 (1986)

Wang, C.L., Guo, J.H.: New systolic arrays for C+AB2, inversion, and division in GF(2m). IEEE Trans. Computers 29, 1120–1125 (2000)

Kung, S.Y.: VLSI array processors. Prentice Hall, Englewood Cliffs (1988)

Kung, H.T., Lam, M.: Fault tolerant and two level pipelining in VLSI systolic arrays. In: MIT conference on Advanced res. VLSI, Cambridge, MA, January 1984, pp. 74–83 (1984)

Knuth, D.E.: The Art of Computer Programming, 2nd edn. Seminumerical Algorithms, vol. 2. Addison-Wesley, Reading (1997)

Gajski, D.D.: Principles of Digital Design. Prentice-hall international, INC., Englewood Cliffs (1997)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2004 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Kim, NY., Yoo, KY. (2004). Digit-Serial AB 2 Systolic Array for Division in GF(2m). In: Laganá, A., Gavrilova, M.L., Kumar, V., Mun, Y., Tan, C.J.K., Gervasi, O. (eds) Computational Science and Its Applications – ICCSA 2004. ICCSA 2004. Lecture Notes in Computer Science, vol 3046. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-24768-5_10

Download citation

DOI: https://doi.org/10.1007/978-3-540-24768-5_10

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-22060-2

Online ISBN: 978-3-540-24768-5

eBook Packages: Springer Book Archive