Abstract

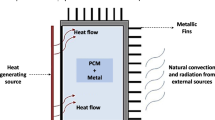

Power is rapidly becoming the primary design constraint for systems ranging from server computers to handhelds. In this paper we study microarchitecture-level coupled power and thermal simulation considering dynamic and leakage power models with temperature and voltage scaling. We develop an accurate temperature-dependent leakage power model and efficient temperature calculation, and show that leakage energy can be different by up to 10X for temperatures between 35oC and 110oC. Given the growing significance of leakage power and its sensitive dependence on temperature, no power simulation without considering dynamic temperature calculation is accurate. Furthermore, we discuss the thermal runaway induced by the interdependence between leakage power and temperature, and show that in the near future thermal runaway could be a severe problem. We also study the microarchitecture level coupled power and thermal management by novel active cooling techniques that reduce packaging thermal resistance. We show that the direct water-spray cooling technique reduces thermal resistance from 0.8oC/W for conventional packaging to 0.05oC/W, and increases system maximum clock by up to 2.44X under the same thermal constraints.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Chandrakasan, A., Bowhill, W.J., Fox, F.: Design of High-Performance Microprocessor Circuits. IEEE Press, Los Alamitos (2001)

Grove, A.S.: Changing vectors of moore’s law. Keynote speech, International Electron Devices Meeting (December 2002)

Burd, T., Pering, T., Stratakos, A., Bordersen, R.: A dynamic voltage-scaled microprocessor system. In: 2000 IEEE International Solid-State Circuits Conference Digest of Technical Papers (February 2000)

Bakoglu, H.B.: Circuits, Interconnections, and Packaging for VLSI. Addison-Wesley, Reading (1990)

Ye, W., Vijaykrishnan, N., Kandemir, M., Irwin, M.J.: The design and use of simplepower: a cycle-accurate energy estimation tool. In: DAC (2000)

Brooks, D., Tiwari, V., Martonosi, M.: Wattch: A framework for architectural-level power analysis optimization. In: ISCA (2000)

Liao, W., Basile, J.M., He, L.: Leakage power modeling and reduction with data retention. In: ICCAD 2002 (November 2002)

Butts, J., Sohi, G.: A static power model for architects. In: Proc. of MICRO33 (December 2000)

Liao, W., Li, F., He, L.: Microarchitecture level power and thermal simulation considering temperature dependent leakage model. In: ISLPED (August 2003)

Dhodapkar, A., Lim, C., Cai, G.: Tem2p2est: A thermal enabled multi-model power/performance estimator. In: Workshop on Power Aware Computer Systems (November 2000)

Skadron, K., Stan, M., Huang, W., Velusamy, S., Sankaranarayanan, K., Tarjan, D.: Temperature-aware microarchitecture. In: Proceedings of the 30th International Symposium on Computer Architecture (2003)

Mutoh, S., et al.: 1-v power supply high-speed digital circuit technology with multithreshold-voltage cmos. IEEE Journal of Solid-state circuits 30, 847–854 (1995)

Vegte, J.V.D.: Feedback Control System, 3rd edn. Prentice-Hall, Englewood Cliffs (1994)

Shivakumar, P., Jouppi, N.P.: Cacti 3.0: An integrated cache timing, power, and area model. In: WRL Research Report 2001/2 (2001)

Gieseke, B.A., et al.: A 600mhz superscalar risc microprocessor with out-of-order execution. In: Proc. IEEE Int. Solid-State Circuits Conf., pp. 176–177 (1997)

Stinson, J., Rusu, S.: A 1.5ghz third generation itanium 2 processor. In: DAC (June 2003)

Skadron, K., Abdelzaher, T., Stan, M.: Control-theoretic techniques and thermal-rc modeling for accurate and localized dynamic thermal management. In: Proceedings of the Eighth International Symposium on High-Performance Computer Architercture (2002)

Hanson, H., Hrishikesh, M., Agarwal, V., Keckler, S., Burger, D.: Static energy reduction techniques for microprocessor caches. In: Proceedings of the International Conference on Computer Design (2001)

Severns, R.: Safe operating area and thermal design for mospower transistors. In: Siliconix applications note AN83-10 (November 1983)

Liao, W., He, L.: Microarchitecture Level Power and Thermal Simulation Considering Temperature Dependent Leakage Model. Technical Report 04-246, University of California at Los Angeles (2003)

Shaw, M., Waldrop, J., Chandrasekaran, S., Kagalwala, B., Jing, X., Brown, E., Dhir, V., Fabbeo, M.: Enhanced thermal management by direct water spray of high-voltage, high power devices in a three-phase, 18-hp ac motor drive demonstration. In: Eighth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (2002)

Tiwari, V., Singh, D., Rajgopal, S., Mehta, G.: Reducing power in high-performance microprocessors. In: DAC (1998)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2005 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Liao, W., He, L. (2005). Coupled Power and Thermal Simulation with Active Cooling. In: Falsafi, B., VijayKumar, T.N. (eds) Power-Aware Computer Systems. PACS 2003. Lecture Notes in Computer Science, vol 3164. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-28641-7_11

Download citation

DOI: https://doi.org/10.1007/978-3-540-28641-7_11

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-24031-0

Online ISBN: 978-3-540-28641-7

eBook Packages: Computer ScienceComputer Science (R0)